LDMOS device capable of improving rebound performance and manufacturing method thereof

A device and performance technology, applied in the field of LDMOS devices and their manufacturing, can solve the problems of lowering the maximum working voltage of LDMOS devices, poor bounce performance, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The LDMOS device capable of improving snapback performance and its manufacturing method of the present invention will be further described in detail below.

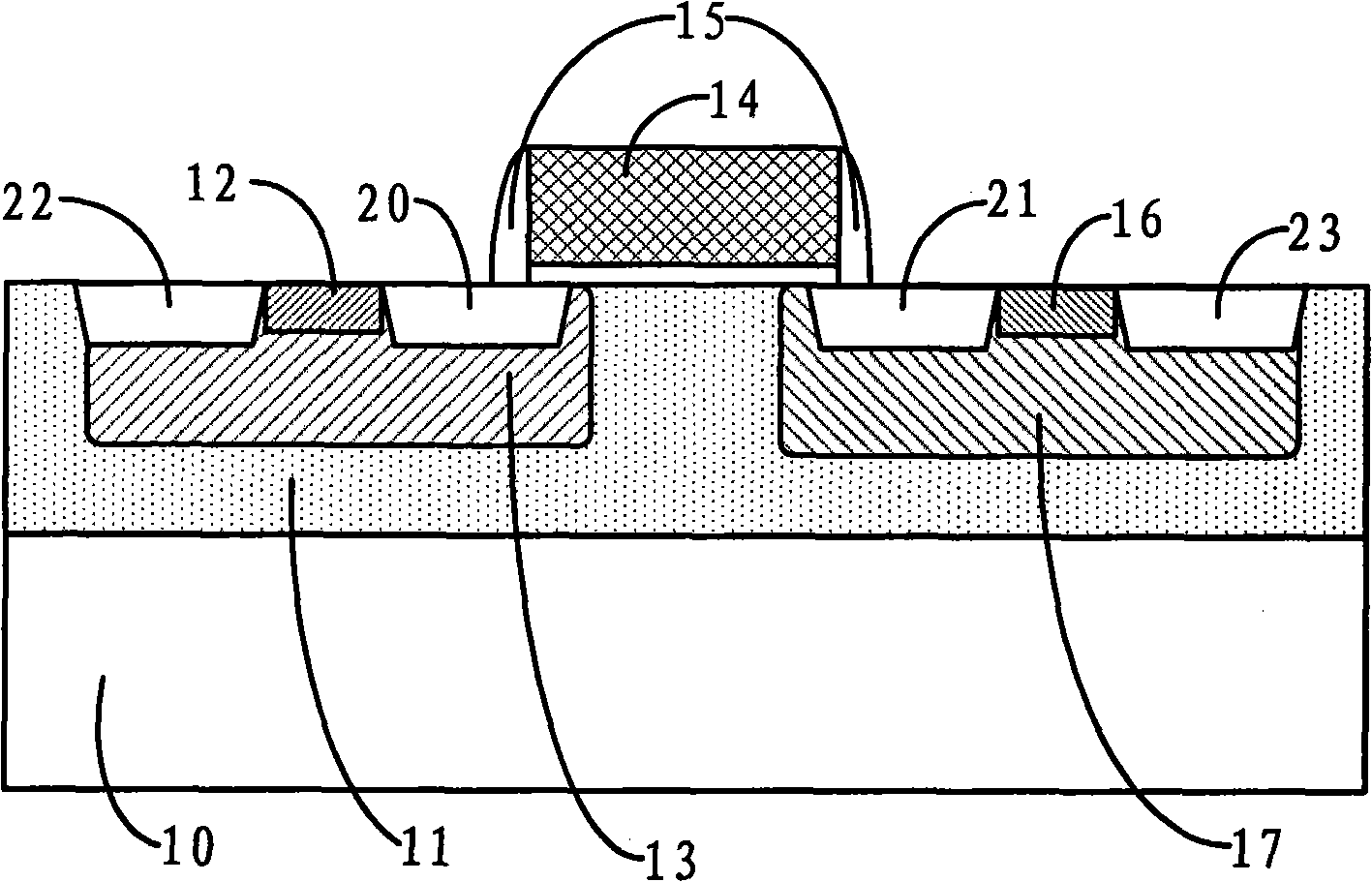

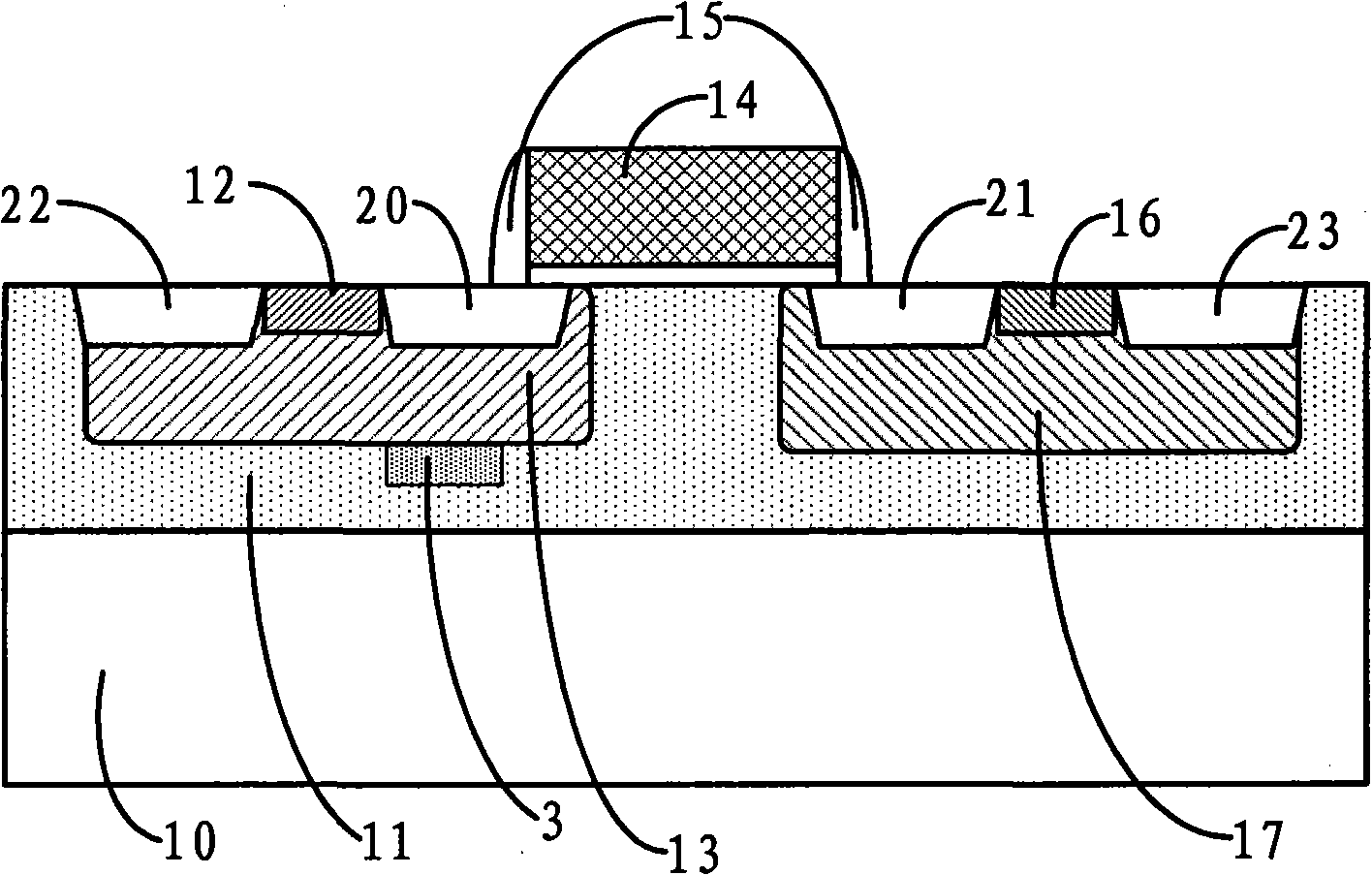

[0025] see image 3 , the LDMOS device of the present invention that can improve bounce performance includes a silicon substrate 10, a high voltage well 11, a source 12, a source drift region 13, a gate 14, a gate spacer 15, a drain 16, and a drain drift region 17. Near-gate trench isolation structures 20 and 21 , far-gate trench isolation structures 22 and 23 , and drag reducing block 3 . Each component of the LDMOS device capable of improving snapback performance of the present invention will be described in detail below.

[0026] The high voltage well 11 is formed in the silicon substrate 10, the source drift region 13 and the drain drift region 17 are formed in the high voltage well 11 and arranged on both sides of the gate 14, the source 12 and the drain 16 are respectively formed in the source drift region ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More