Chip statistical data management method and device

A technology of statistical data and management methods, applied in the fields of electrical digital data processing, data exchange network, computing, etc., can solve problems such as bank access conflicts, and achieve the effect of improving processing capacity and reducing access conflicts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

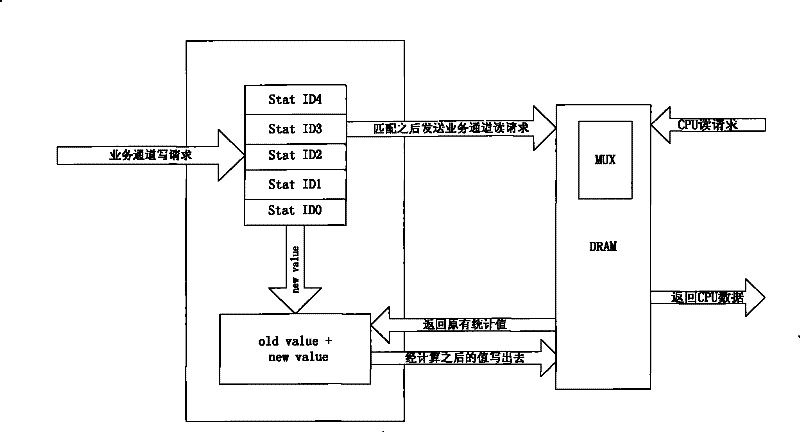

[0035] This embodiment all uses off-chip DRAM to store statistical data. The schematic diagram of the principle of a chip statistical data management method provided by this embodiment is as follows figure 1 As shown, the specific process is as follows figure 2 shown, including the following steps:

[0036] Step 21. Input the statistical data into the FIFO (First in First Out) memory provided in the chip.

[0037] After the service channel obtains the statistical data that needs to be written into the off-chip DRAM, the service channel transmits the statistical data to the chip, and the chip stores the statistical data in a specific FIFO memory set in the chip. In the embodiment of the present invention, since the delay ratio between the requesting end and the sending end is 3:1, the depth value of the specific FIFO memory may be selected to be greater than 4.

[0038] The depth of the FIFO refers to how many N bits of data the FIFO can store (if the width is N). Such as a...

Embodiment 2

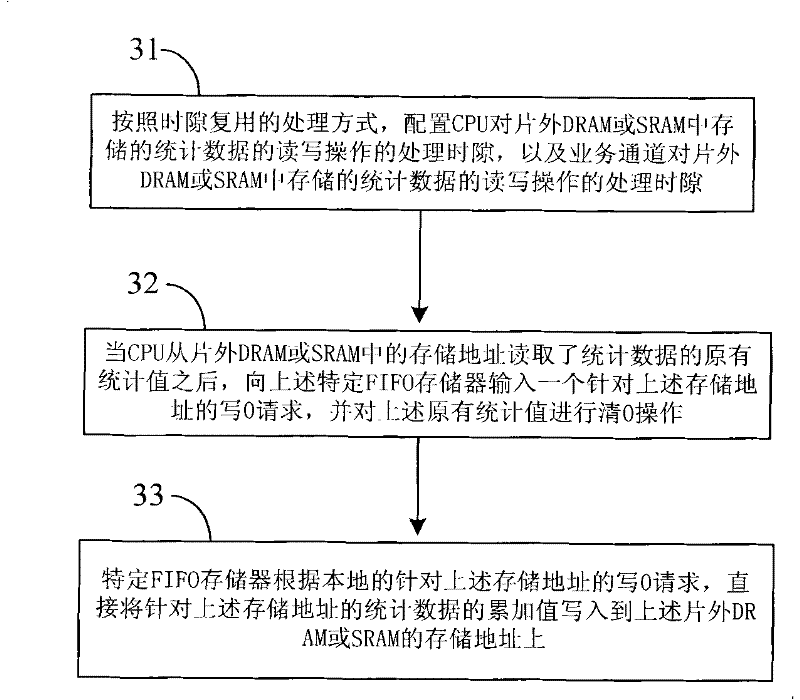

[0050] The processing flow of a method for performing bypass processing between the read and write operations of the CPU and the service channel on statistical data provided by this embodiment is as follows: image 3 As shown, the following processing steps are included:

[0051] Step 31, according to the time slot multiplexing processing method, configure the processing time slot for the CPU to read and write the statistical data stored in the off-chip DRAM, and the processing of the service channel for the read and write operations of the statistical data stored in the off-chip DRAM time slot.

[0052] According to the processing mode of time slot multiplexing, this embodiment configures the processing time slots for the CPU to read and write the statistical data stored in the off-chip DRAM, and the processing of the service channel for the read and write operations of the statistical data stored in the off-chip DRAM time slot. When the CPU has no read and write operations...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More