Method for anti-interference encryption in bus expansion

A bus and function technology, applied in the field of anti-interference encryption of bus expansion, can solve the problems of weak anti-interference ability, high parallel bus speed, single-board design, etc., achieve high-reliability design, improve reliability, and improve anti-interference. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

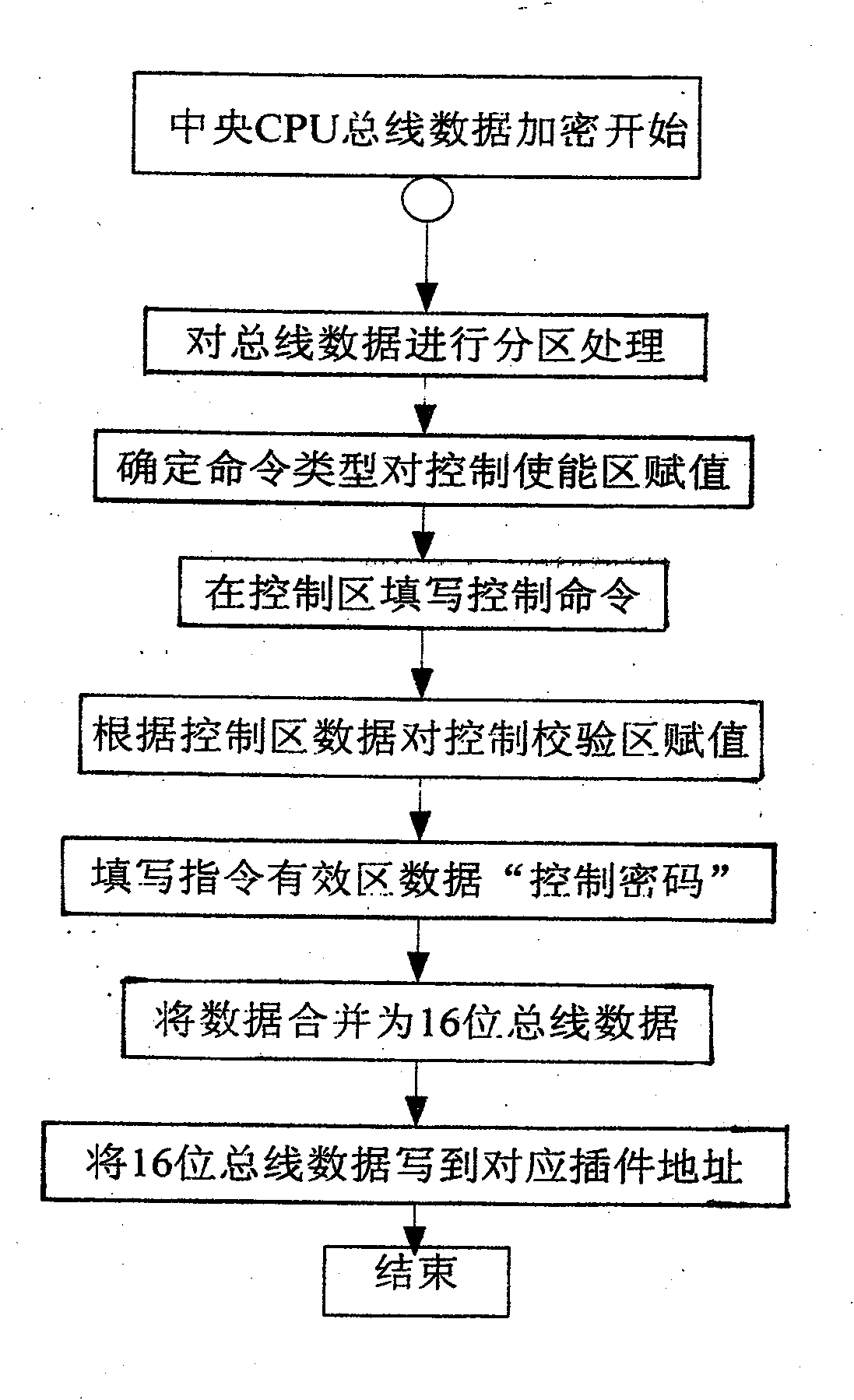

[0024] The present invention will be described in detail below. Firstly, the data bus is divided into regions, and the functions of each partition are specifically defined. In this case, a 16-bit bus is taken as an example for illustration. The 16-bit parallel bus data is divided into four areas: control enable area, instruction effective area, control area and control check area (also called "bus bit-wise partition encryption method"). The 16-bit data bus partition is shown in the following table:

[0025]

[0026] Among them, the control enable area: the code Bit15~Bit12 can be set to 0101, which corresponds to the general enable command of the function plug-in hardware controlled, and the code should correspond to the function and number of the function plug-in.

[0027] Instruction effective area: Bit11~Bit8 can be fixedly coded as 0101, which is used as the central CPU instruction enable password, indicating that the control instruction is effectively given by the CPU....

Embodiment 2

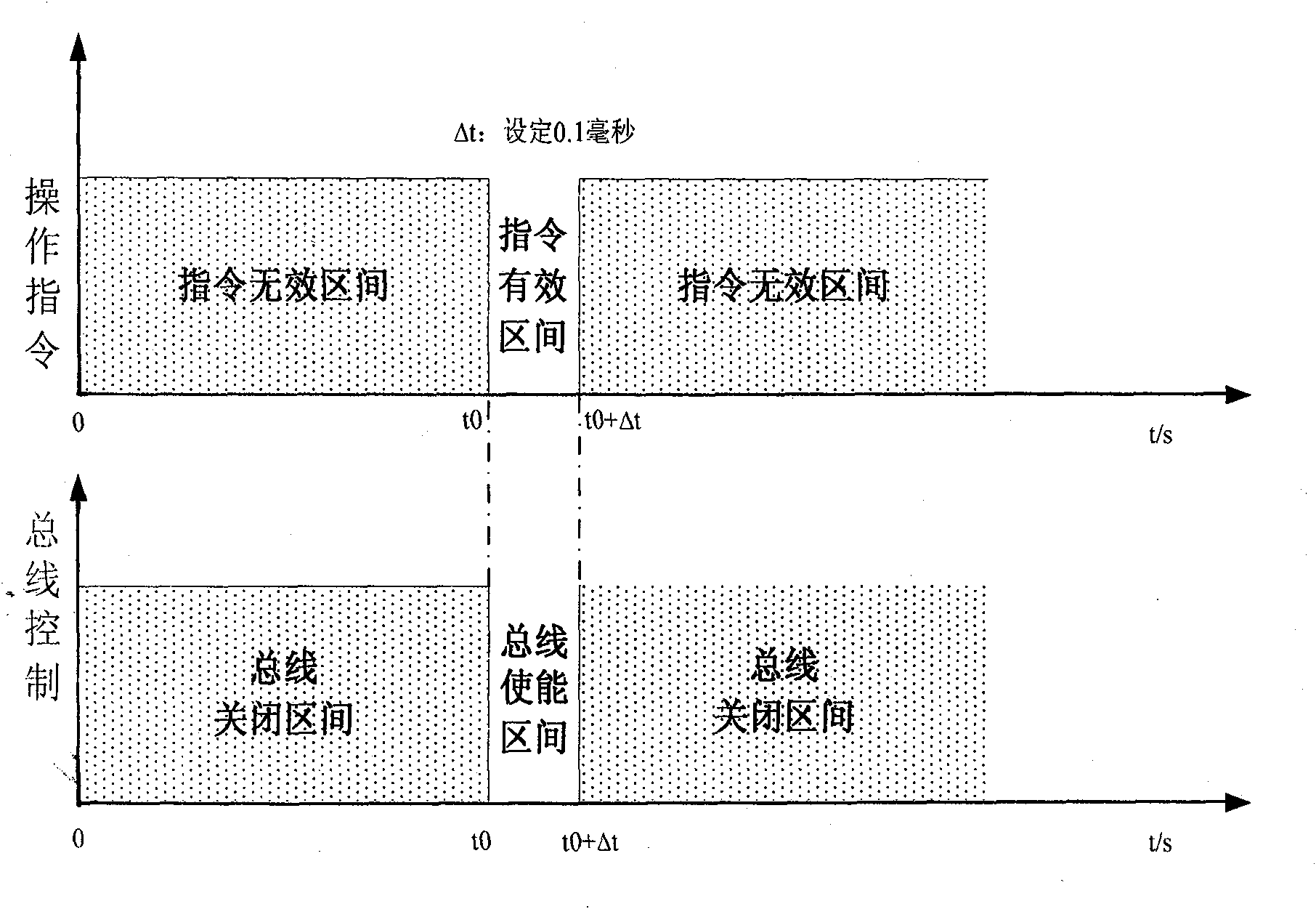

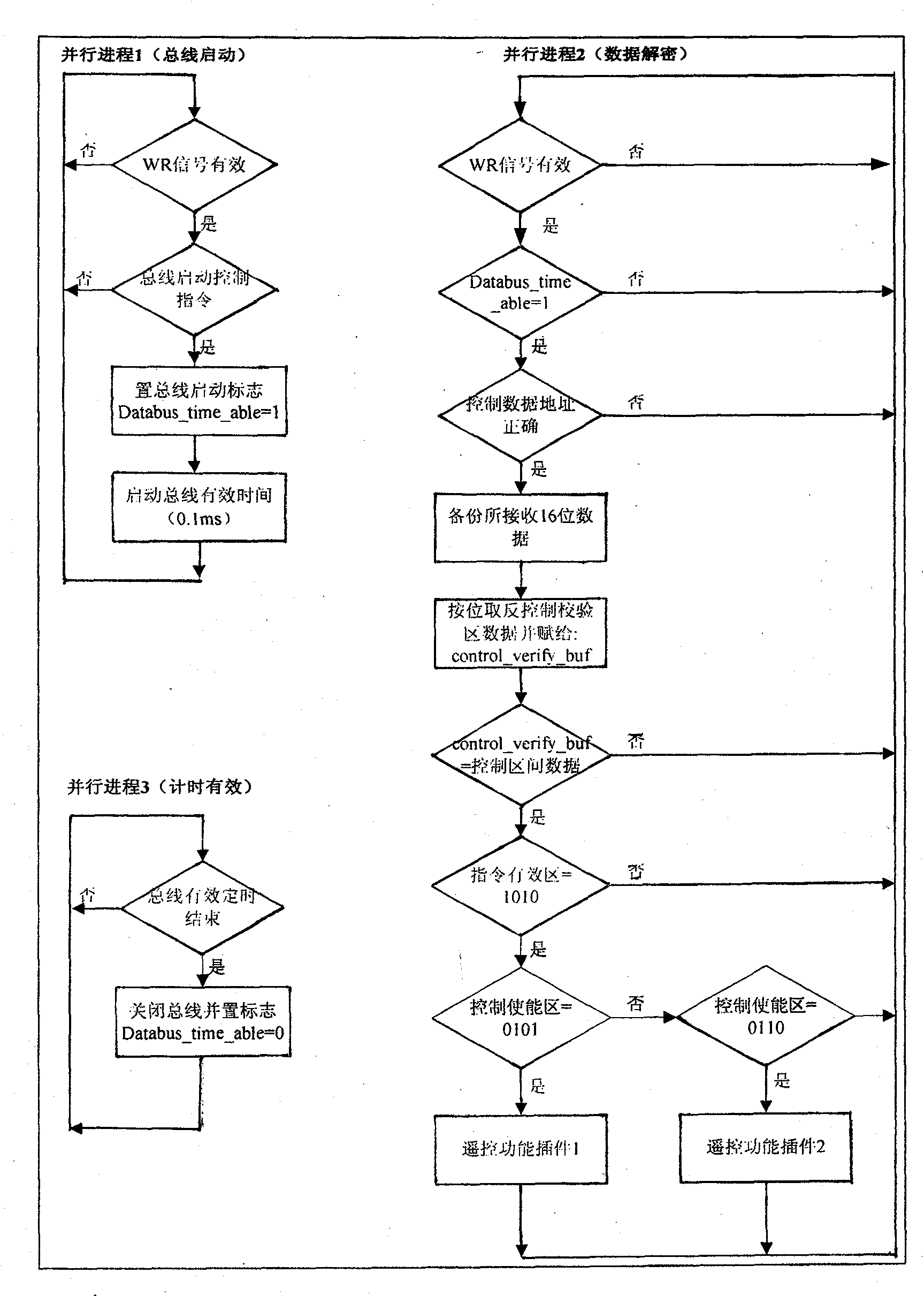

[0039] On the basis of the bus space encryption in the first embodiment above, a time-sharing dual instruction verification mode is adopted to realize bus time encryption. Such as figure 2 As shown, the principle is that before the central CPU issues the bus control command, it first issues the valid bus enable command. After the functional plug-in correctly receives the valid bus enable command, the functional plug-in starts to receive the bus control command and continues to receive the waiting time. 0.1ms (this time can be set according to the bus speed), if the function plug-in receives the control command conforming to the bus space encryption within this time, it will control out, if it exceeds 0.1ms, the function plug-in will refuse to receive the bus control command, that is, the central The CPU considers this control failure. The time encryption instruction format may be the same as the space encryption format. The specific timing diagram is as follows, Δt is the r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More