System on chip adopting ARINC 659 rear panel data bus interface chip

A backplane data bus and interface chip technology, applied in the field of computer communication, can solve problems such as no bus products, and achieve the effect of improving reliability, strong reliability and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

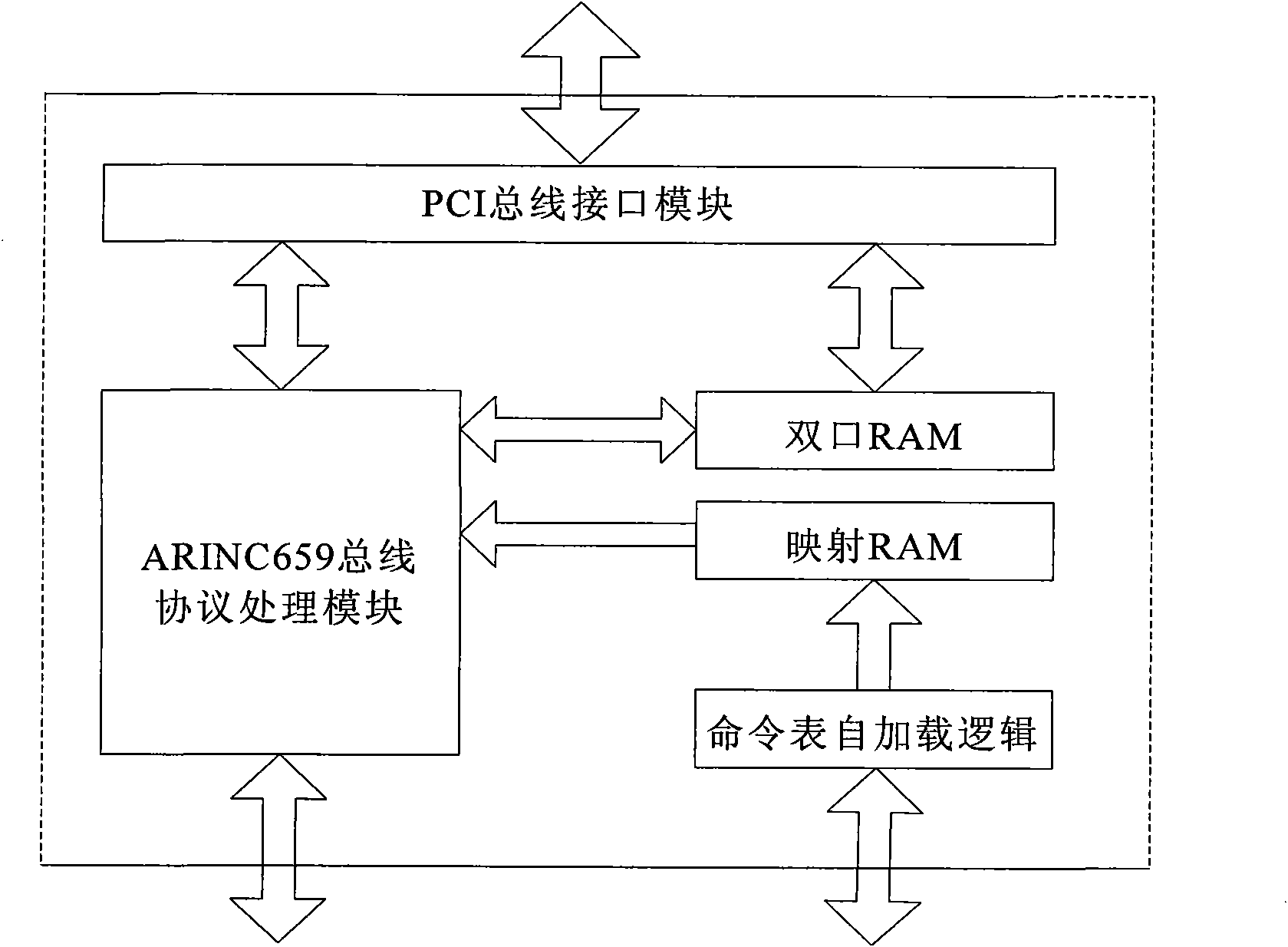

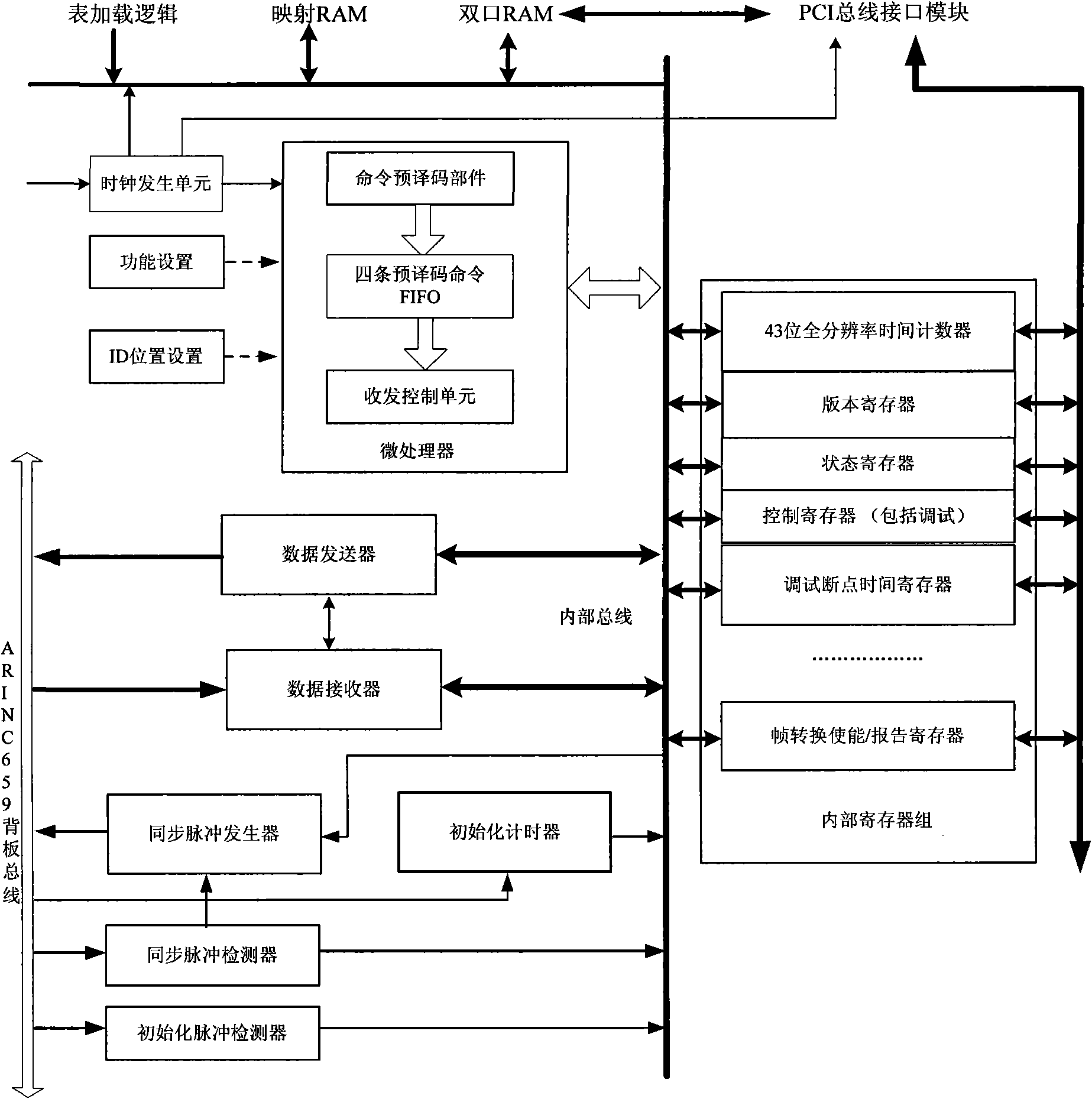

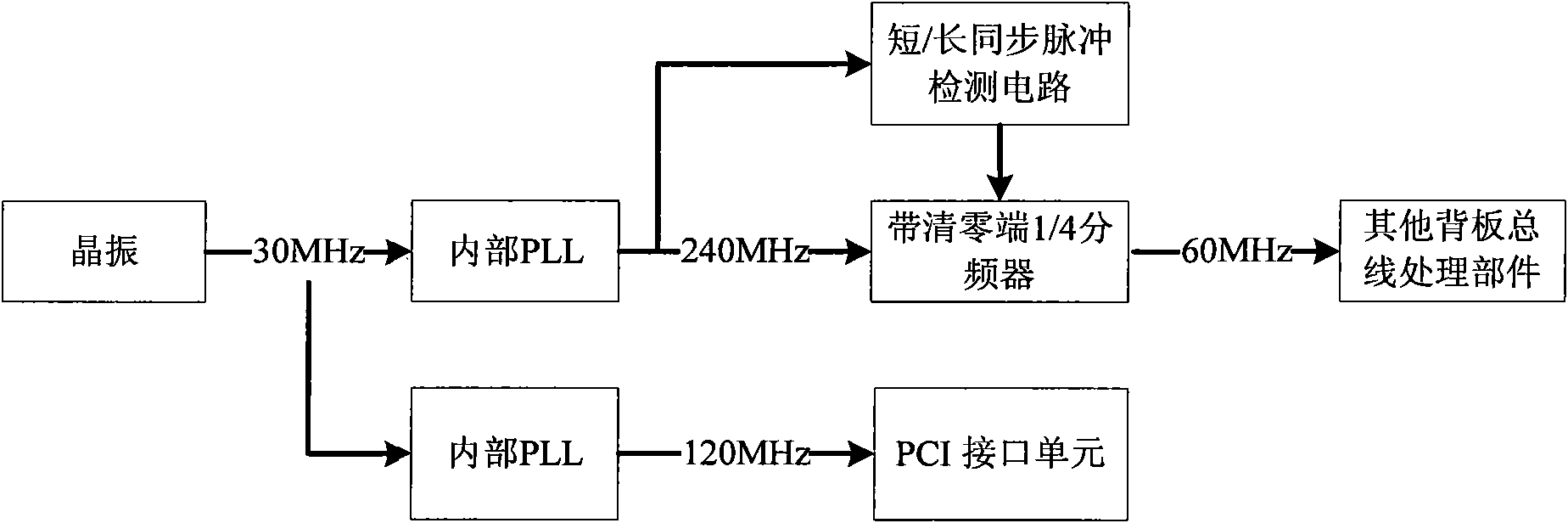

[0030] see figure 1 The present invention provides an ARINC 659 backplane data bus interface chip system-on-chip. The ARINC 659 backplane bus interface chip (abbreviation: interface chip, BIU) interface chip is equipped with a Harvard architecture-specific frame description language (FDL) microprocessor. The on-chip system of the command processor, BIU mainly includes five parts: PCI bus interface module, dual-port RAM, bus command table mapping memory (abbreviation: mapping RAM), command table self-loading function module and protocol processing function module; command table The self-loading function module is electrically connected to the ARINC 659 bus protocol processing module through the bus command table mapping memory; the PCI bus interface module is electrically connected to the ARINC 659 bus protocol processing module through a dual-port RAM; the PCI bus interface module is connected to the ARINC 659 bus protocol processing module The modules are electrically connect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More