Semiconductor packaging structure and semiconductor packaging process

A packaging process and packaging structure technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of space occupation and cannot be effectively used, and achieve the effect of improving contact density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

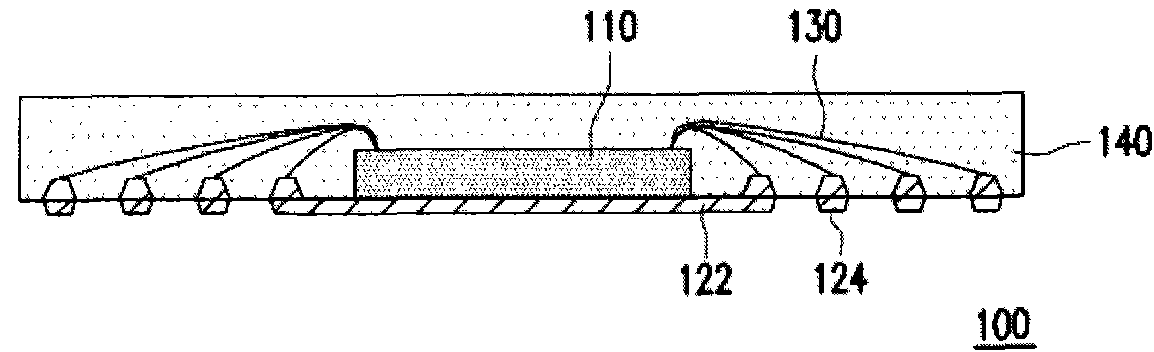

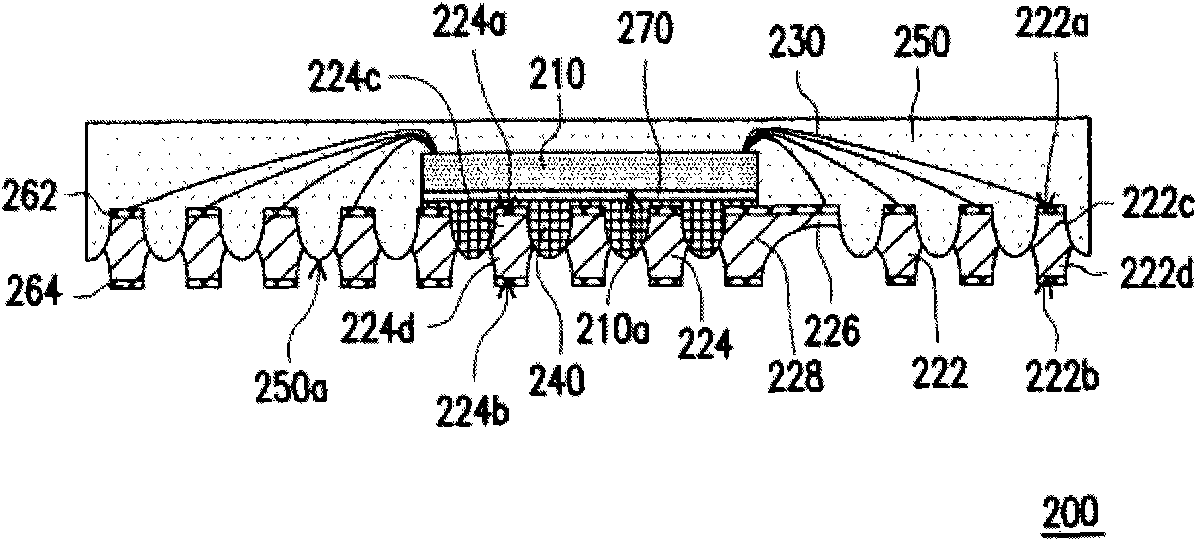

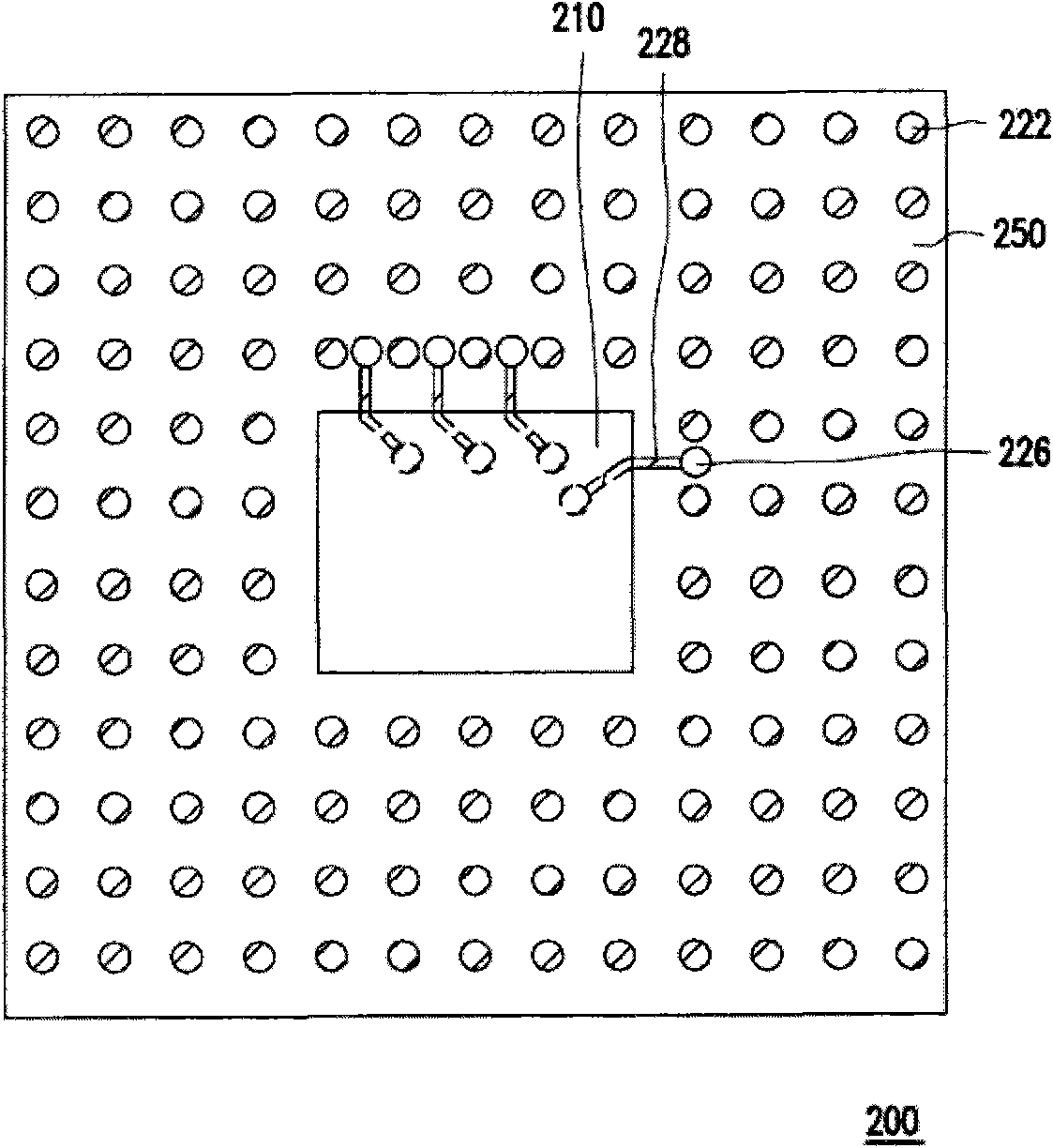

[0075] Reference will now be made in detail to some embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings and this specification to refer to the same or like parts.

[0076] definition

[0077] Some or all of the following definitions apply to the embodiments described below.

[0078] As noted hereinafter, the singular forms "a", "an" and "the" include plural referents unless the context clearly dictates otherwise. For example, "a depression" may actually include multiple depressions.

[0079] As described hereinafter, the term "adjacent" means close to or adjacent to. Adjacent components may be spaced apart from each other or may be in actual or direct contact with each other. In some cases, adjacent components may be connected to each other or may be integrally formed with each other.

[0080] As described below, terms such as "inside", "top", "bott...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com