Video synchronization pixel clock generating circuit

A pixel clock and circuit generation technology, applied in television, electrical components, image communication, etc., can solve problems such as video data jitter, image cannot be displayed stably and effectively, line length jitter, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

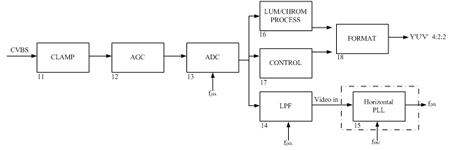

[0020] Such as figure 2 Shown is a block diagram of a video decoding circuit combined with the present invention. The video signal CVBS signal (or S-Video signal) is first clamped by the CLAMP module 11 to restore the DC level of the video signal, and then passes through the AGC module 12 to construct a video signal that meets the quantization range of the ADC, and then passes the ADC module 13 to convert the analog video The signal is quantized into a digital video signal, and then the video data is subjected to bright color processing through the LUM / CHROM PROCESS module 16 to separate the brightness information Y and the chrominance information C, and the brightness information Y is further peaked to generate Y', and the chrominance information C is decomposed The U', V' signals generated after comb filtering are adjusted and combed, and the contro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More