STI forming method

A technology of mask pattern and hard mask layer, which is applied in the field of STI formation, can solve the problem of etching barrier layer falling off, and achieve the effect of reducing the possibility of falling off and high planarization efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

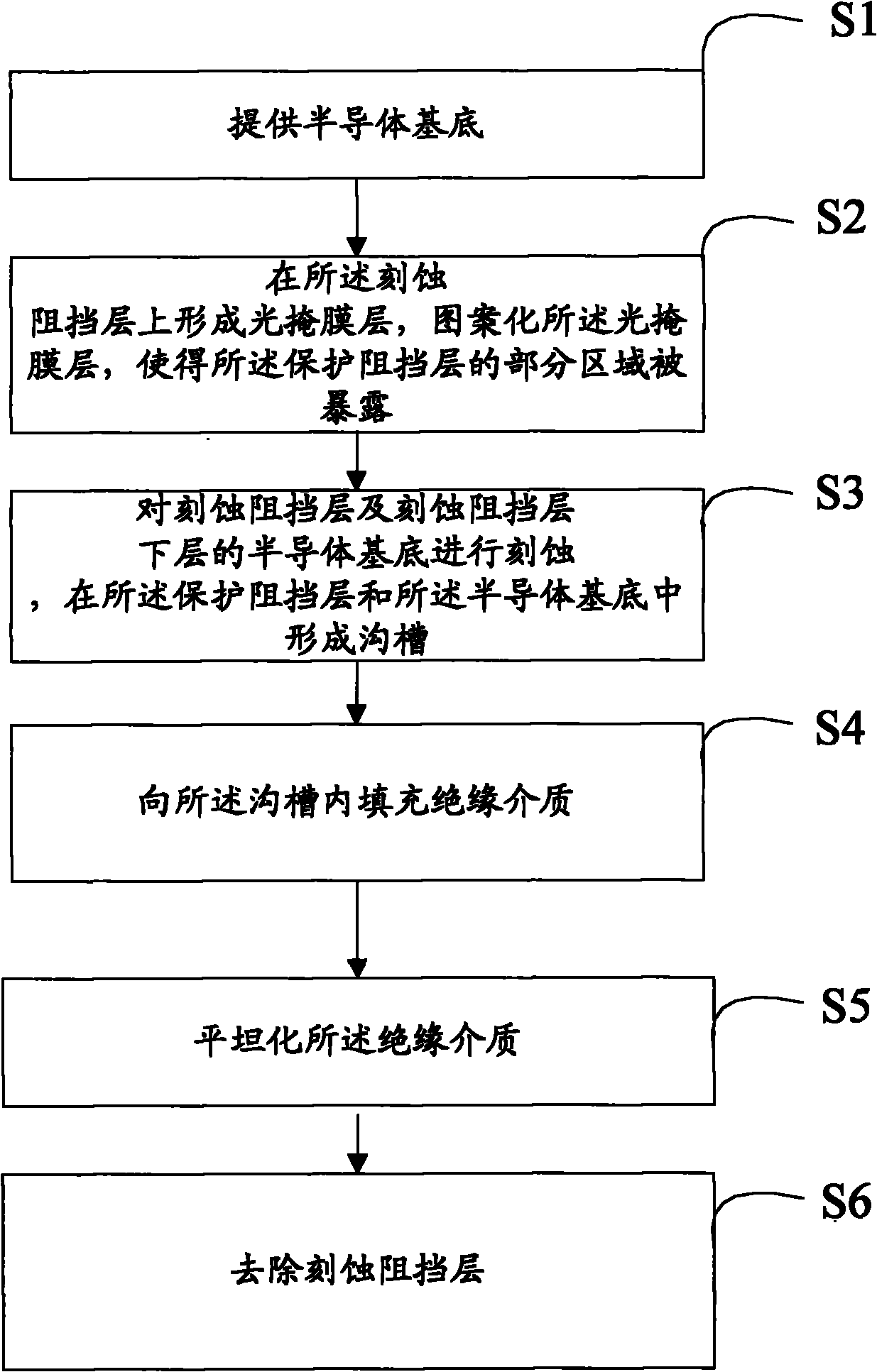

[0026] It can be seen from the background technology that in the formation process of STI, a layer of etch stop layer is usually formed on the semiconductor substrate; then a mask layer with an opening pattern is formed on the etch stop layer; and then etched at the opening of the mask layer A trench is formed in the semiconductor substrate and the etch barrier layer; then an insulating medium is filled into the trench; then the insulating medium is planarized; finally, the etch barrier layer is removed to form an STI.

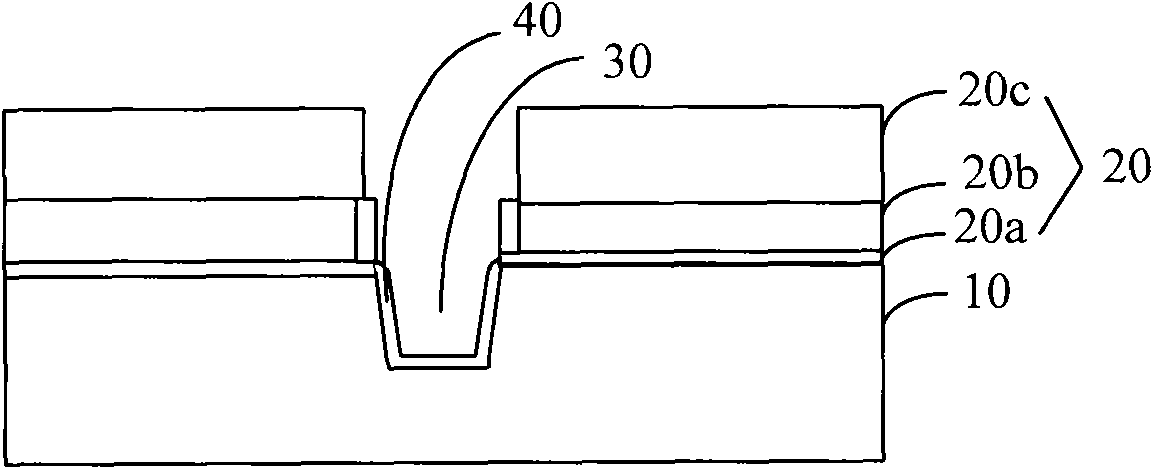

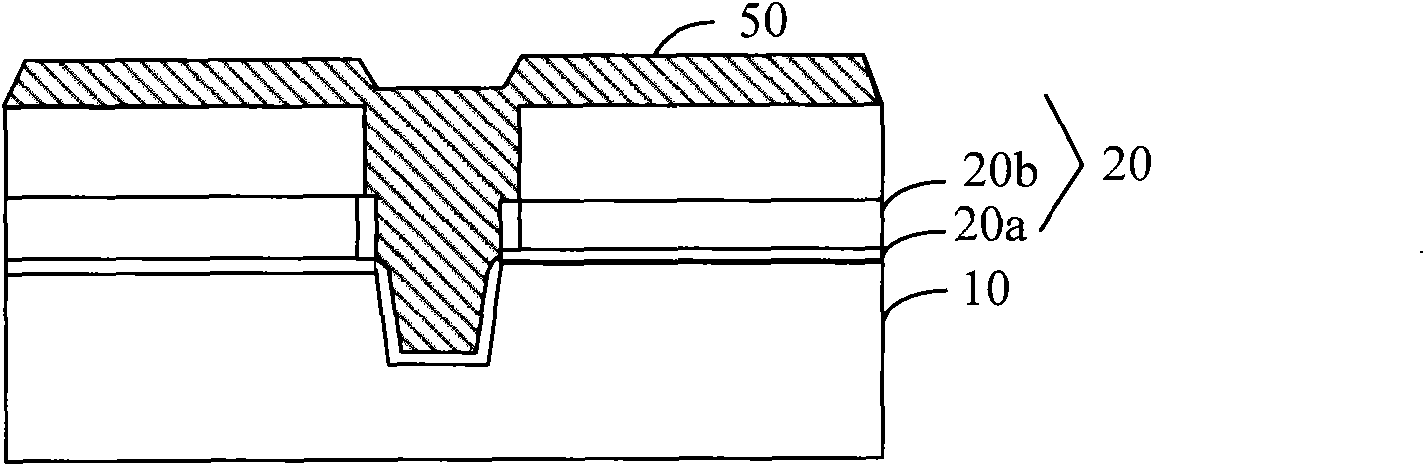

[0027] However, using the existing technology, after etching the semiconductor substrate and forming the groove in the etching barrier layer, it is found that there are some peelings of the etching barrier layer on the substrate. The inventor of the present invention thinks after research: The stacked structure of silicon nitride and polysilicon is used as an etching barrier layer, wherein the silicon nitride layer is used as a hard mask layer of the semiconduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More