Complementary metal oxide semiconductor (CMOS) input/output interface circuit

A technology of input and output interfaces and circuits, applied in the direction of logic circuits, electrical components, pulse technology, etc., to achieve the effect of eliminating leakage current and avoiding leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

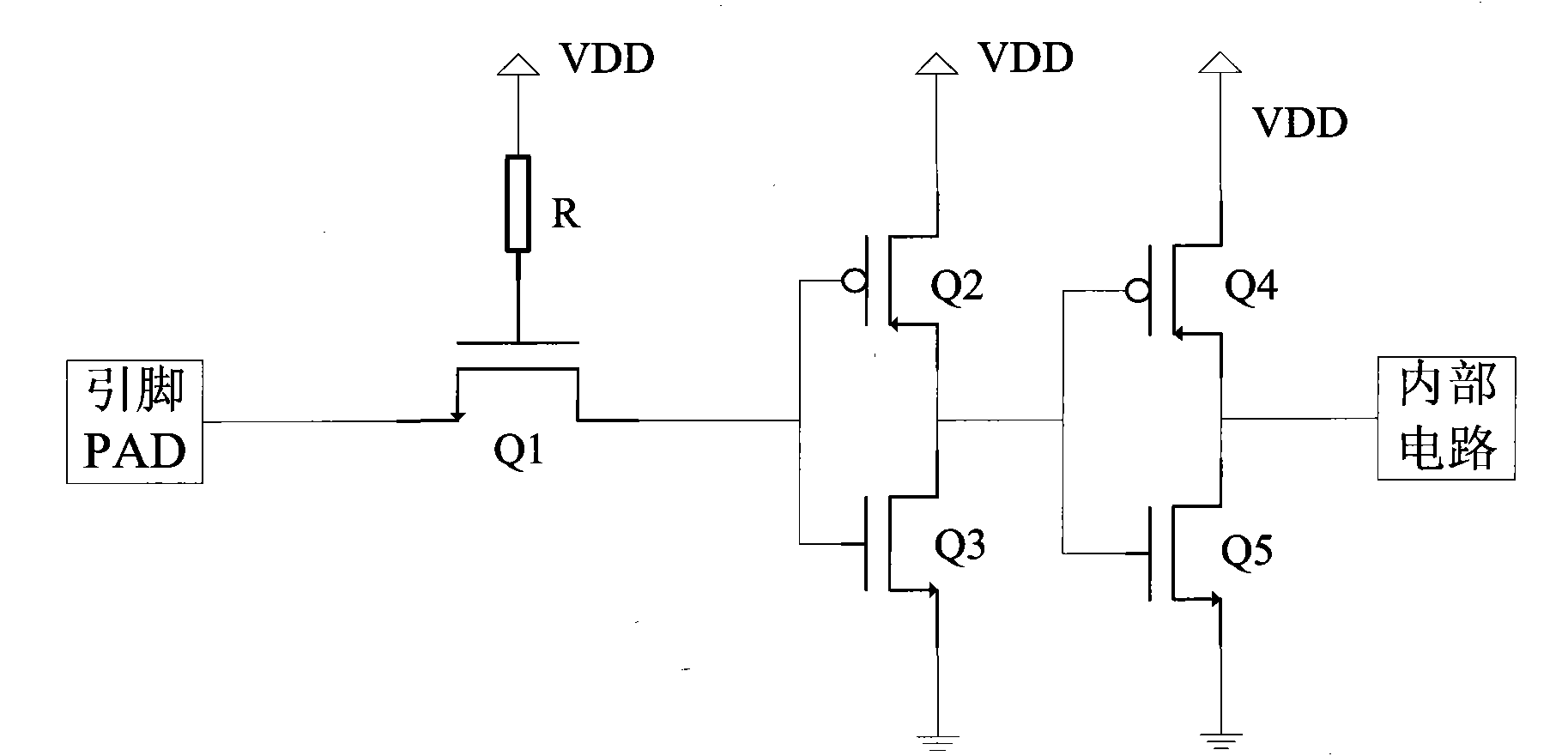

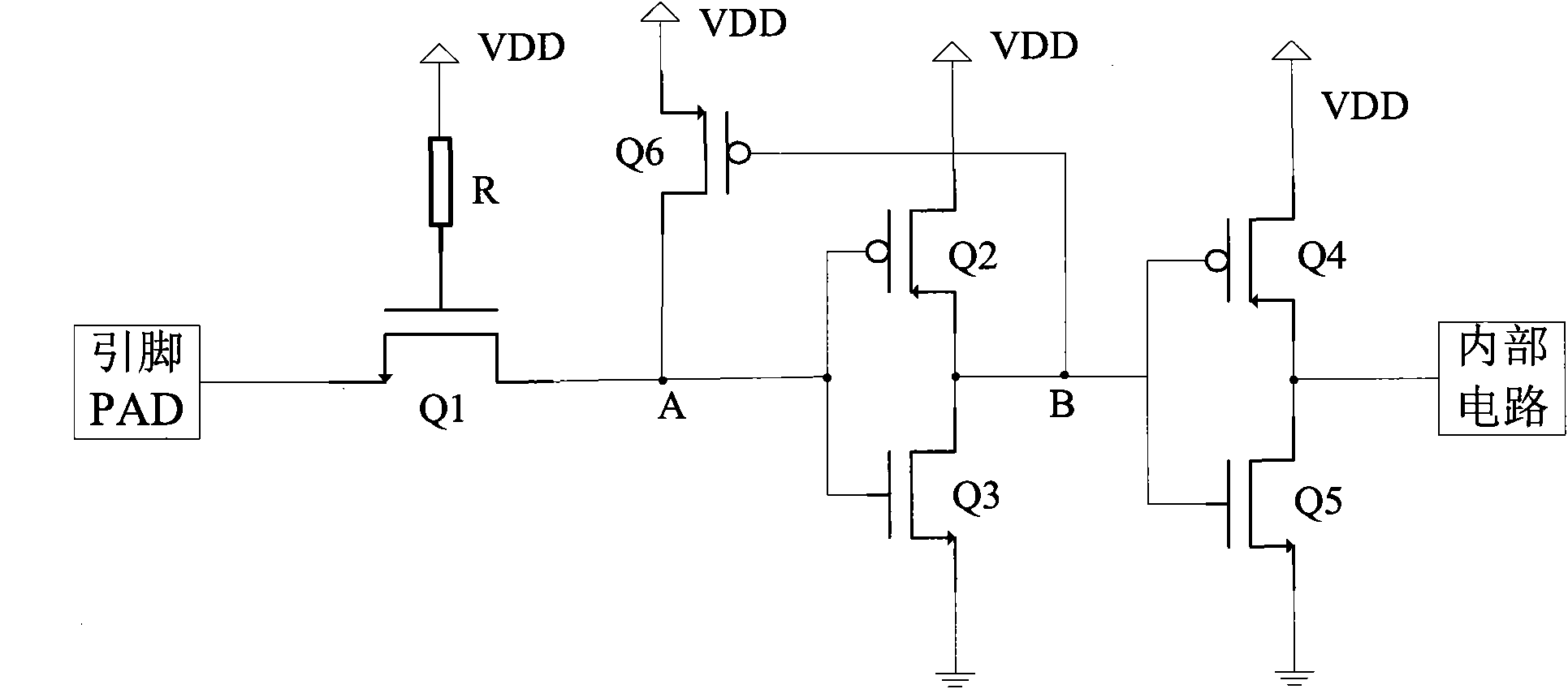

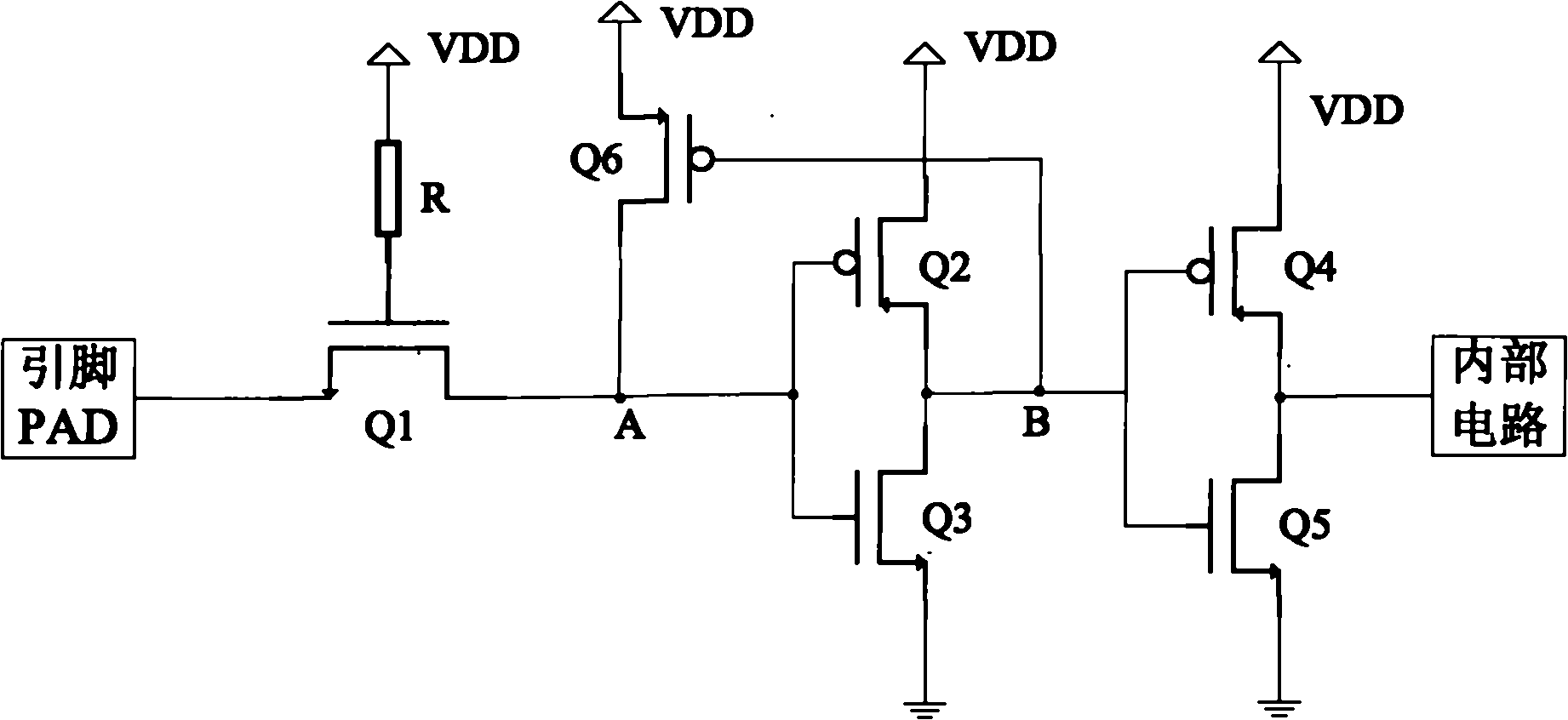

[0011] An embodiment of the CMOS input-output interface circuit of the present invention is as figure 1 As shown, it includes a first NMOS transistor Q1, a second PMOS transistor Q2, a third NMOS transistor Q3, a fourth PMOS transistor Q4, a fifth NMOS transistor Q5, a sixth PMOS transistor Q6, and a resistor R. The first NMOS transistor Q1 The gate is connected to the power supply VDD through the resistor R, the source is connected to the pin, the drain is connected to the gates of the second PMOS transistor Q2 and the third NMOS transistor Q3, the drain of the second PMOS transistor Q2 is connected to the power supply VDD, and the third NMOS transistor Q3 The source of the second PMOS transistor Q2 and the drain of the third NMOS transistor Q3 are connected to the gates of the fourth PMOS transistor Q4 and the fifth NMOS transistor Q5, and the drain of the fourth PMOS transistor Q4 is connected to the power supply VDD. The source of the fifth NMOS transistor Q5 is grounded, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More