Method for simulating cores of multi-core processor by adopting time division multiplex

A multi-core processor, time division multiplexing technology, applied in machine execution devices, concurrent instruction execution, etc., can solve the problems of long hardware programming development cycle, low flexibility and applicability, and high programming and debugging difficulty, and improve hardware integration. , avoid problems and the effect of consistency, saving hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The specific implementation manners of the present invention will be described in further detail below in conjunction with the accompanying drawings and examples. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

[0029] The present invention uses an N-segment pipeline to simulate the core of a multi-core processor. Different from the pipeline of the processor itself, the purpose of using the pipeline here is mainly to improve the integration and ensure the flexibility of the simulated processor when it is compatible with other instruction sets.

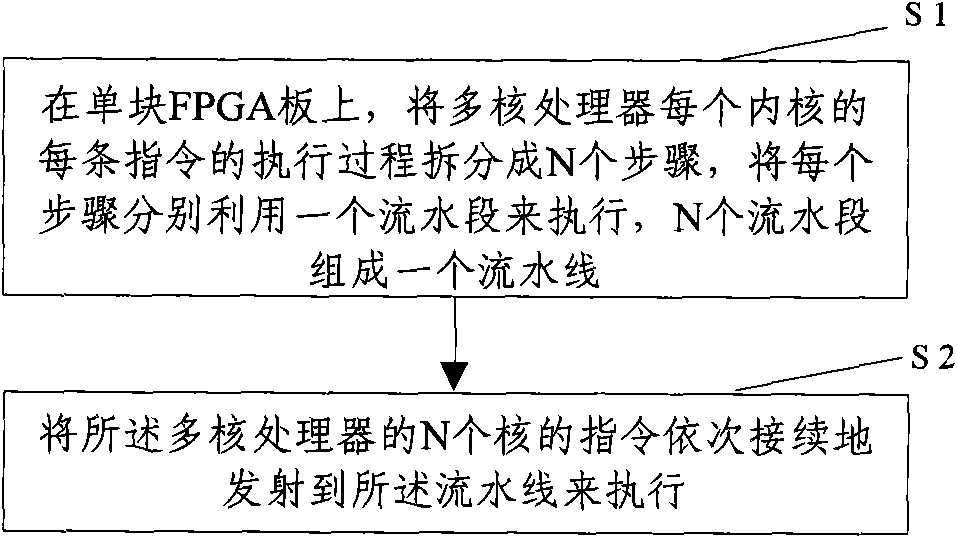

[0030] Such as figure 1 Shown, method of the present invention comprises the following steps:

[0031] S1. On a single FPGA board, the execution process of each instruction of each core of the multi-core processor is divided into N steps, and each step is executed using a pipeline segment, and N pipeline segments form a pipeline;

[0032] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More