IGBT (Insulated Gate Bipolar Translator) device structure and preparation method thereof

A device structure and device technology, applied in the field of trench IGBT device structure and preparation, can solve problems such as poor anti-latch-up characteristics, narrow safe working area, and increased series resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

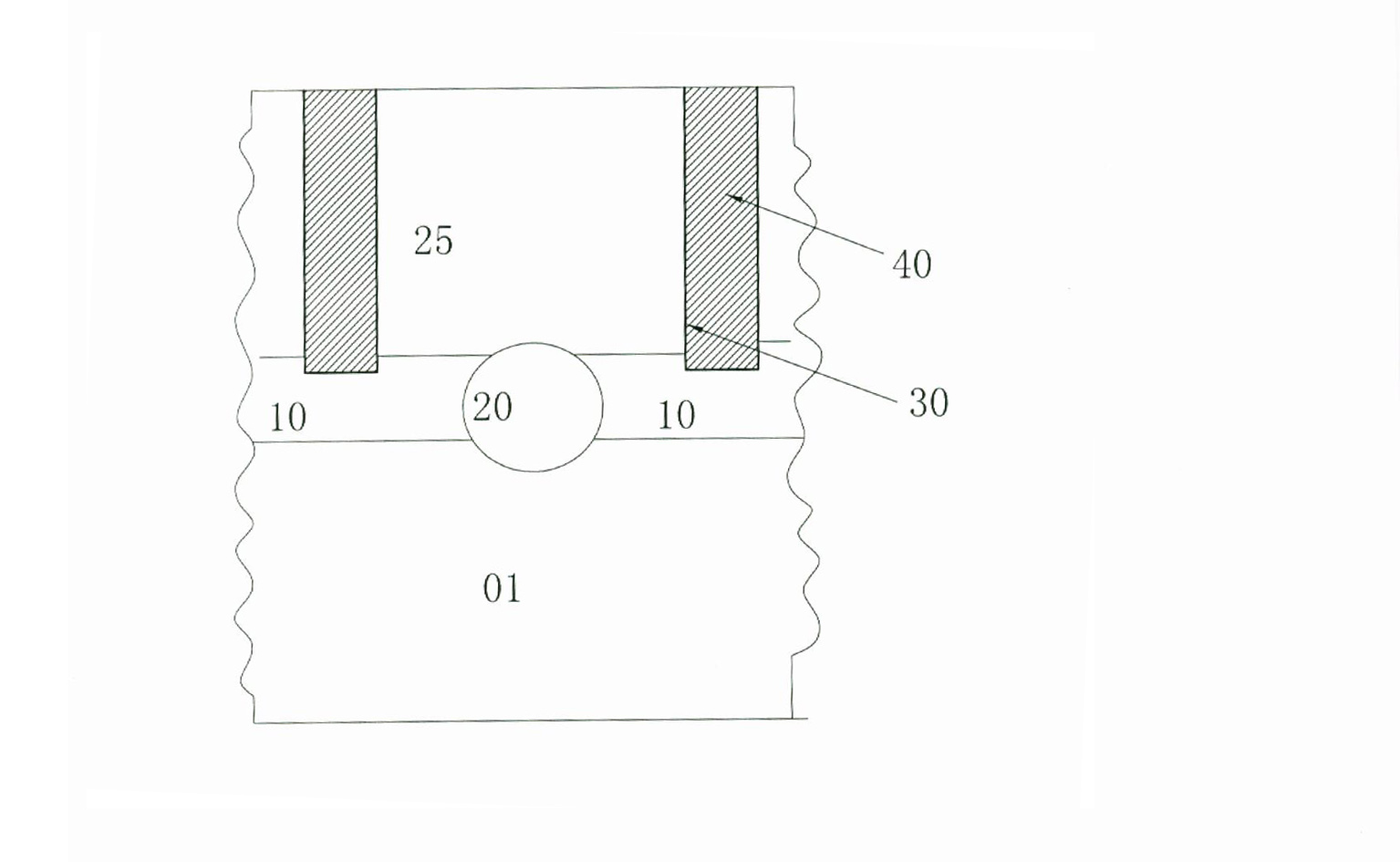

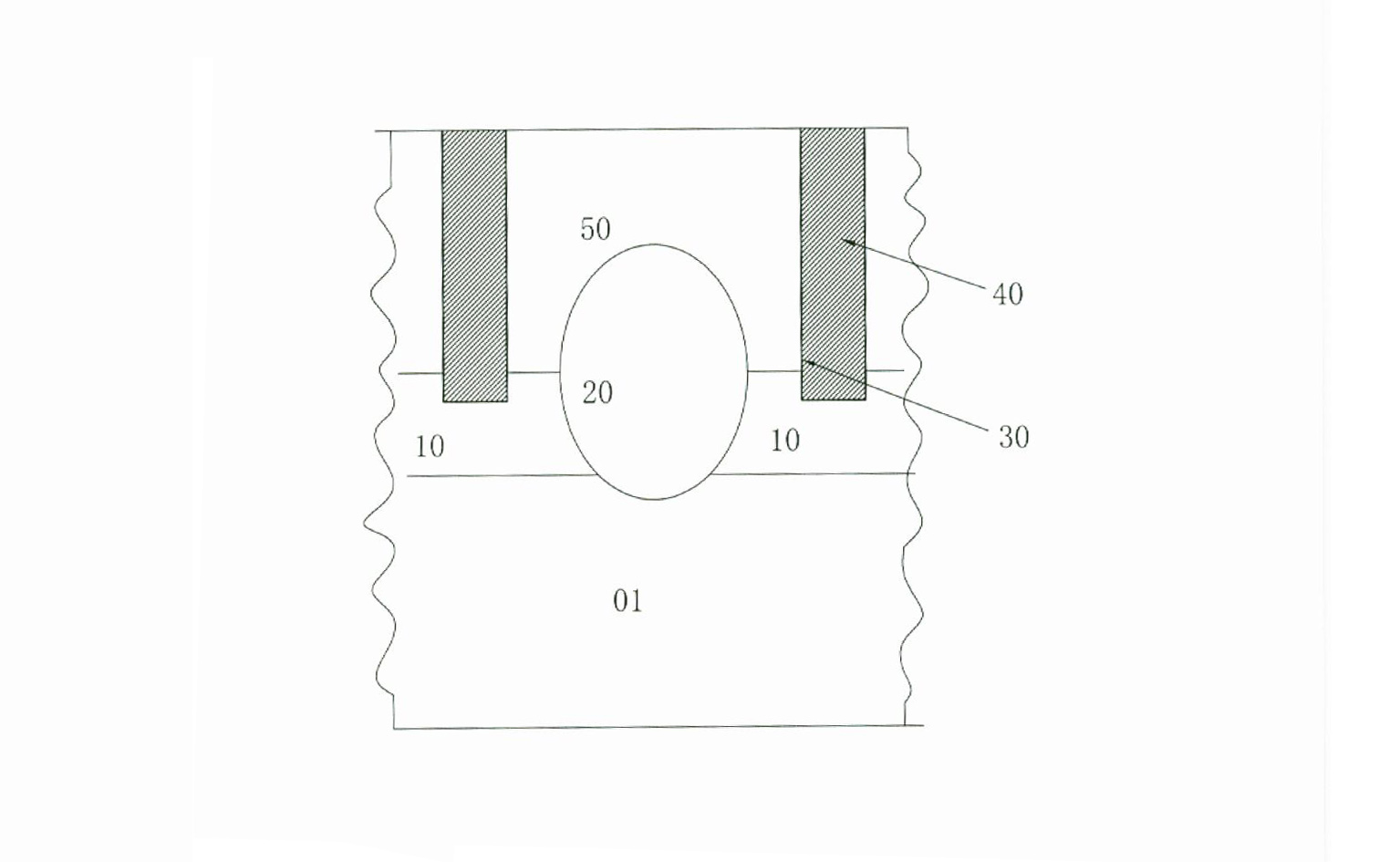

[0033] A method for preparing a trench type IGBT device structure with high latch-up resistance as described in the present invention, the preparation method includes the following steps: the first step is to provide a high-resistance N-type silicon substrate, and use the N-type Ion implantation introduces a medium-concentration N-type doped region (as an N-type well) with a higher concentration than the substrate in the device active region of the silicon substrate, and carries out high-temperature diffusion advancement; the second step, using a photolithography mask and boron Ion implantation introduces higher-doped P-type regions into the above-mentioned N-type wells at intervals as P-type deep wells, and anneals to activate; the third step is to grow a certain thickness of high-resistivity N-type epitaxial silicon on the silicon substrate by epitaxy. The fourth step is to use photolithography and etching technology to etch deep trench arrays in the active area of the ...

Embodiment

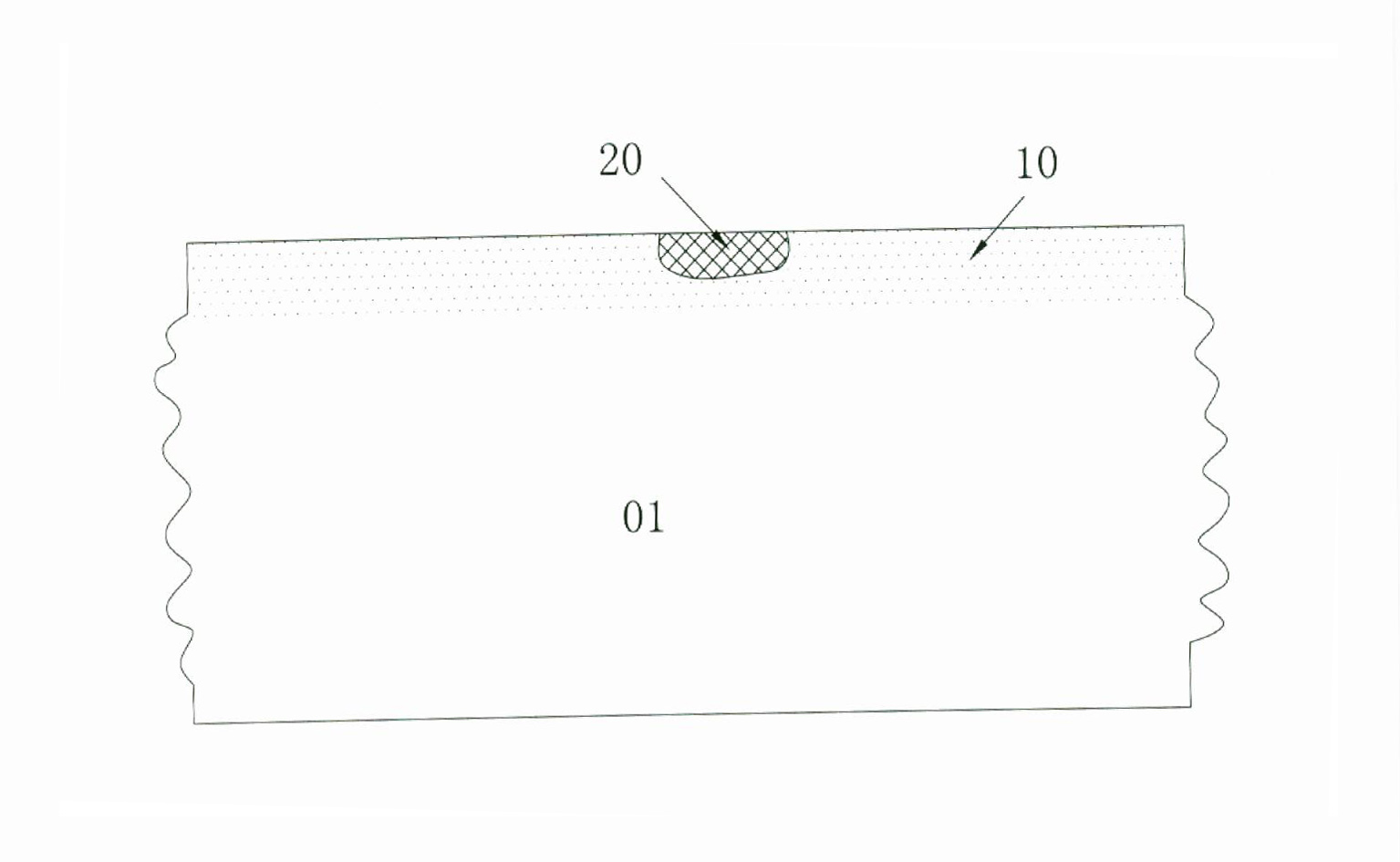

[0040] Example: see figure 1 , the first step and the second step of a manufacturing method of a highly latch-up resistant trench IGBT device with a P+ deep well of the present invention, on an N-type high-resistivity region melting type or epitaxial silicon substrate 01, using N-type ion implantation introduces a medium-concentration N-type doped region higher than the substrate concentration in the device active region of the silicon substrate. The impurity is usually phosphorus or arsenic, and the implantation dose is 5e11 / cm 2 to 5e13 / cm 2 The implantation energy is between 25keV and 1MeV; then carry out high-temperature diffusion and advance to form an N-type deep well 10; use a photolithography mask and boron ion implantation to introduce a P-type highly doped buried layer at intervals in the above-mentioned N-type doped region area, the boron ion implantation dose is 5e13 / cm 2 up to 1e15 / cm 2 Between, the implantation energy is between 30keV and 1MeV, and annealing i...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap