Flash memory wear balance method

A technology of wear leveling and dynamic wear leveling, which is applied in the direction of memory system, memory architecture access/allocation, memory address/allocation/relocation, etc. It can solve the problems affecting the read and write performance of the wear leveling algorithm system and improve the read and write performance and longevity effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0069] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention.

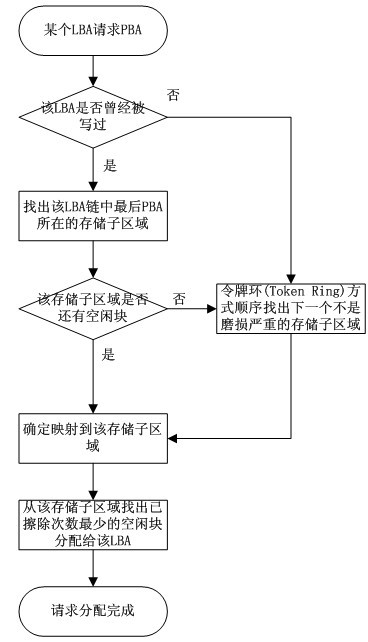

[0070] The wear leveling method of a kind of flash memory of the present invention adopts the method for dividing and conquering to flash memory (as solid state disk), specifically comprises the following steps:

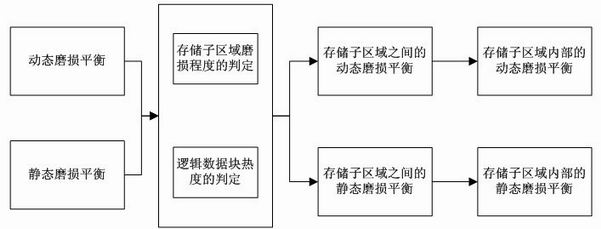

[0071] The total storage area is divided into N storage sub-areas, and two levels of dynamic / static wear balance are implemented for the interior of the storage sub-area and the storage sub-area.

[0072] The system maintains an erased count table (Erase Count Table), which records the number of erased times of all physical blocks in the storage system. If a physical block is erased once, the data item corresponding to the physical block plus 1.

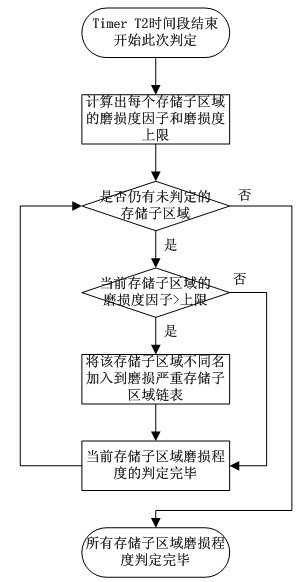

[0073] The system checks the wear condition of each physical block through the statistics table of the number of times era...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More