Blocking-rendering based generation of anti-aliasing line segment in GPU

A line segment and scan line technology, applied in the field of line segment anti-aliasing, can solve the problems of frequent memory access, low efficiency of graphics chips, and not allowing pixels, etc., and achieve the effect of fast generation speed, increased speed, and reduced number of memory accesses

Active Publication Date: 2011-06-15

CHANGSHA JINGJIA MICROELECTRONICS

View PDF2 Cites 7 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

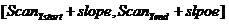

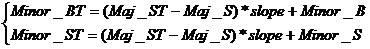

The traditional graphics drawing pipeline is a fixed pipeline (FixedPipeline) architecture, but this architecture has frequent access to memory, resulting in low efficiency of the graphics chip. In order to reduce the number of memory accesses, a GPU implementation technology based on block rendering is proposed. This The technique is to divide the drawing area into several blocks of equal size, and then render in units of blocks. Then, during the drawing process of a certain block, the pixels in other blocks are not allowed to enter the rendering. When the anti-aliasing line segment is generated, a line segment It may span several blocks. In order to achieve block-by-block drawing of anti-aliasing line segments, it is necessary to calculate the drawing range of the line segment in the block to ensure that when a certain block is drawn, pixels in other blocks will not be generated.

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

The invention discloses a blocking rendering algorithm based generation technology of a sawtooth line segment in a GPU, which is carried out after finishing blocking of the line segment. The generation technology comprises the following steps of determining left and right (or up and down) intersection points of the line segment in a block according to the block where the line segment is located and a line segment generation direction; writing intersection point data in a memory; generating a coordinate which has the width of 1 after taking out the line segment from the memory; expanding the coordinate according to the width of the line segment; shearing according to a block boundary and the like. The realization mode can be matched with the blocking rendering algorithm to finish rapid generation of the sawtooth line segment.

Description

Generation of Anti-aliased Line Segments in GPU Based on Block Rendering technical field The invention mainly relates to the field of anti-aliasing of lines in graphics chip design, in particular to the realization of anti-aliasing of lines in GPU based on block rendering. Background technique In the raster display system, since the graphics signal is continuous, but in the rasterization process, the pixels represented are discrete, and when discrete pixels are used to represent continuous graphics, distortion will occur, which is also called aliasing. Research to eliminate or The technology to weaken the aliasing phenomenon is called anti-aliasing technology, and the anti-aliasing of line segments has always been an important content in the design of graphics chips. The traditional graphics drawing pipeline is a fixed pipeline (FixedPipeline) architecture, but this architecture has frequent access to memory, resulting in low efficiency of the graphics chip. In order to r...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G06T11/20G06T1/60

Inventor 焦永陈宝民龙斌

Owner CHANGSHA JINGJIA MICROELECTRONICS