DSP Builder-based time-varying delay hyperchaos digital circuit design method and circuit

A digital circuit and design method technology, applied in the field of digital random sequence cryptography, can solve problems such as analysis and explanation not given, and achieve the effect of simple structure, ensuring complexity and robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

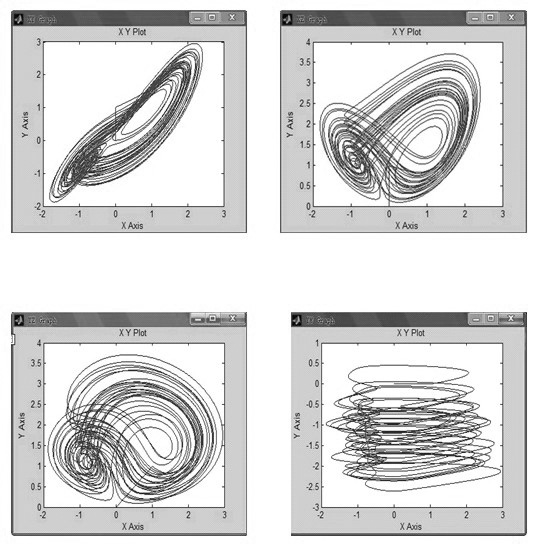

[0062] Example 1: Design and implement hyperchaos System digital circuit

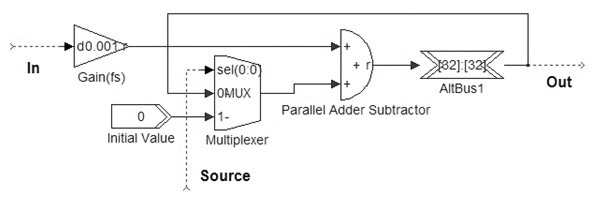

[0063] The invention carries out the digital circuit design of the hyperchaotic system based on the optimized discretization equation group. Using the first-order difference formula (5) to convert hyperchaos The differential equations of system (2) are discretized, and the optimized iterative equations are obtained as follows:

[0064] (7)

[0065] In (7) the sampling frequency The linear term and nonlinear term that can act on the chaotic system at the same time will become a global gain in the next digital circuit design, thereby optimizing the circuit design and facilitating signal control and amplitude limitation. It becomes a global gain module and does not directly perform multiplication operations with each vector, reducing the use of modules such as multipliers, thereby improving the calculation accuracy of the nonlinear te...

Embodiment 2

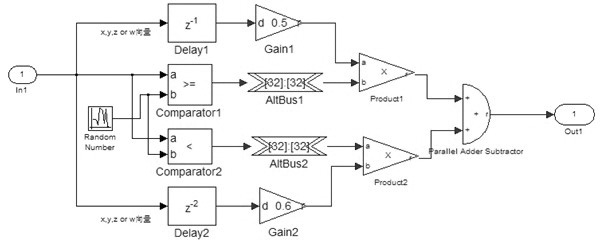

[0070] Example 2: Design and implement hyperchaos with variable time delay System digital circuit

[0071] in four dimensions The time-delay disturbance term is introduced into the mathematical model of system (2):

[0072] (8)

[0073] Introduced in the above formula is vector of lags, variable is the delay gain, is the time lag. Correspondingly, the following is introduced in the discrete system (7) sequence lag

[0074] (9)

[0075] where the variable is the delay gain of the time-delay system, is the time lag, and its proper assignment can make the new system enter the chaotic state. For a discretized system, the time lag must be an integer multiple of the reciprocal of the sampling frequency, that is, . introduce N The value before sampling time is fed back to the system as the time-delay control quantity, so that the dynamic behavior of the system can be adjusted and controlle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More