Video component data information acquiring and extracting method

A video data and video signal technology, applied in the field of video component data information acquisition and extraction, can solve the problems of low processing efficiency, large memory processing bandwidth, large resource consumption, etc., and achieve the effect of reducing time delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

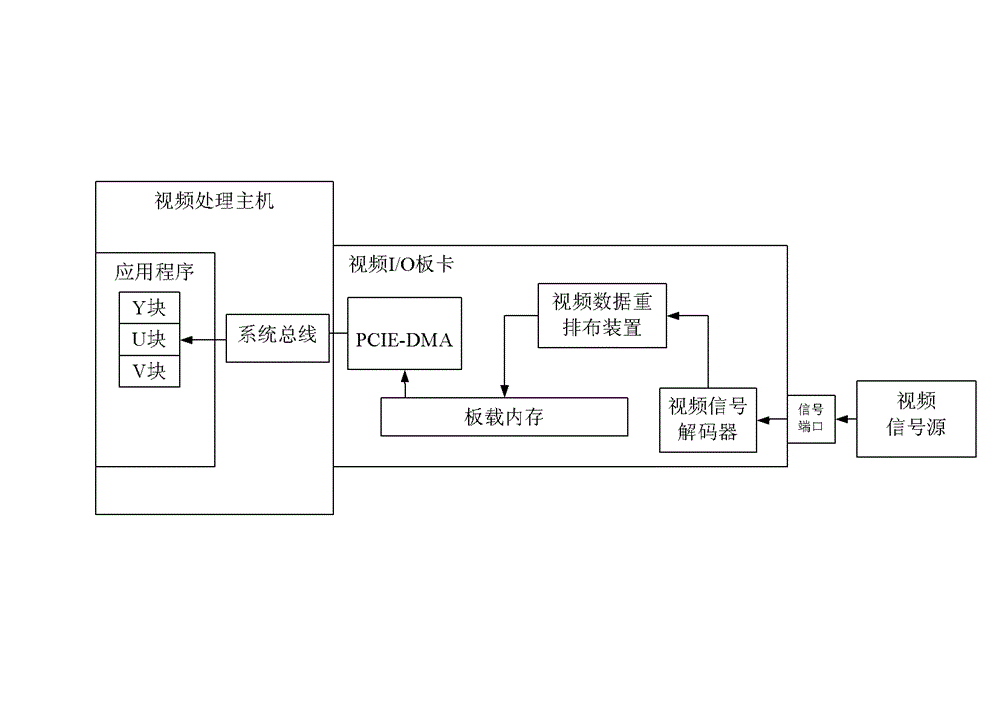

[0037] This embodiment is a method for acquiring video data component information. The system used in the method described in this embodiment is as figure 1As shown, including: a video data processing host with application programs, a system bus, a video I / O board with a board driver plugged into the video data processing host, and a video I / O board installed on the video I / O board On-board video signal decoder, video data rearrangement device, onboard memory, PCIE-DMA controller.

[0038] The main processing chip used in this embodiment is the Virtex5 series programmable logic gate array (FPGA) of Xilinx, the model is XC5VSX50T, the main logic module of hardware function includes: video signal decoder, video data rearrangement device, on-board memory, The PCIE-DMA controller and so on are realized through hardware programming of FPGA. In addition, the current mainstream DDRII memory particles in the market are used as the onboard memory of the video I / O board for data inter...

Embodiment 2

[0083] This embodiment is an improvement of the first embodiment, and it is a refinement of the steps of the first embodiment related to video data rearrangement. The video data rearrangement device and system used in this embodiment are as follows: Figure 7 As shown, including: Y cache, IO-DMA_Y, U cache, IO-DMA_U, V cache, IO-DMA_V. This embodiment adopts the direct storage method to arrange the interleaved video data into block video data, and the detailed steps of the step of rearranging the video data are as follows, and the process is as follows Figure 8 Shown:

[0084] The video signal decoder obtains the width W and height H of the input video according to the standard information of the input video, and decodes the input video. When the video signal decoder decodes the video signal, it distinguishes whether it is the Y component, the U component, or the V component. , enter the following corresponding steps according to different components.

[0085] If it is fou...

Embodiment 3

[0089] This embodiment is an improvement of the second embodiment, which is about the refinement of the SGL table in the second embodiment. The step of transmitting block video data described in this embodiment is to transfer a complete frame of block video data from the onboard memory to the memory of the video data processing host in the environment of the direct storage method, using the SGL table to express the data The source address and destination address of handling, the generation process of described SGL table comprises the steps:

[0090] The following three steps are parallel steps.

[0091] For the Y data block, use Address_Y and the memory address provided by the application for storing the Y component data as the first entry to generate SGLItem1, and the length of the transmitted data is the width W of the video input multiplied by the height H words of the video input Festival.

[0092] For the U data block, use Address_U and the memory address provided by th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More