Semiconductor module

A technology of semiconductors and substrates, applied in the field of semiconductor modules

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

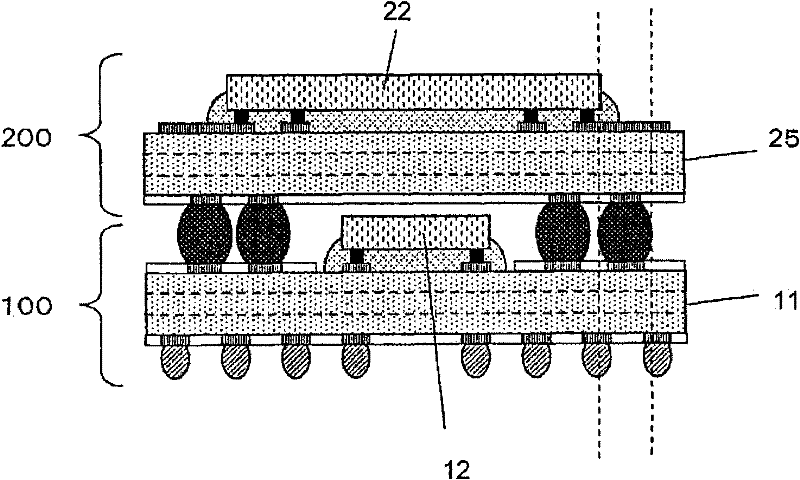

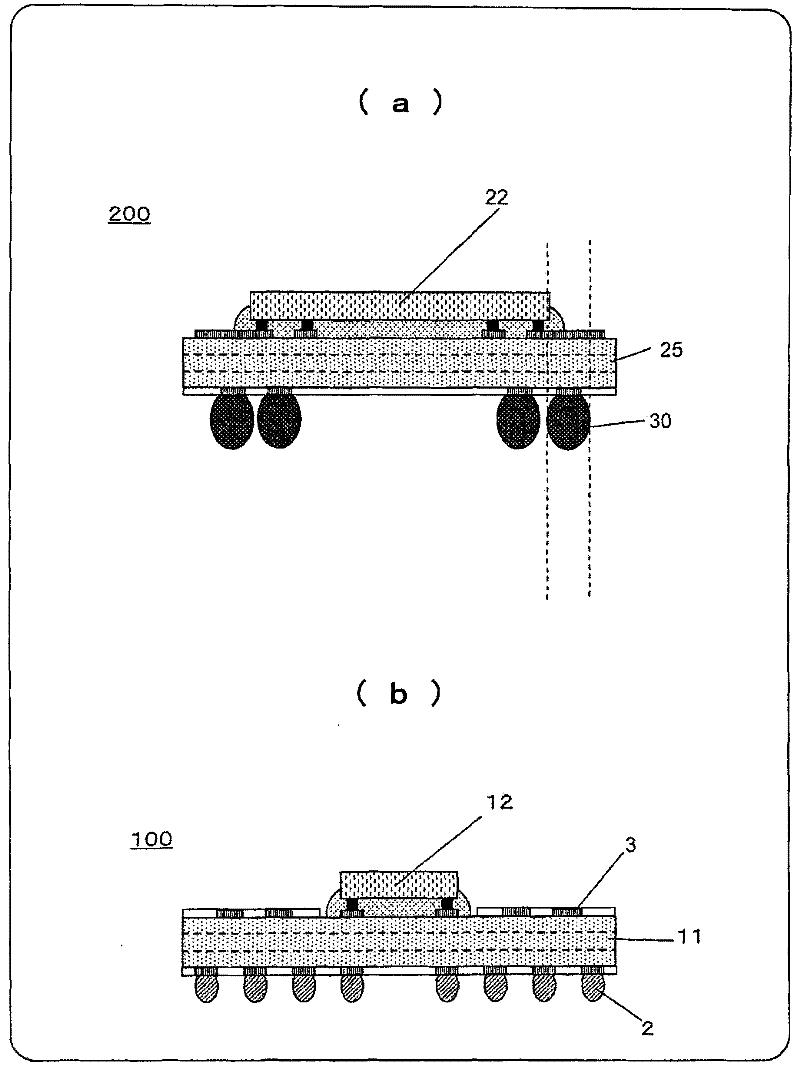

[0051] The semiconductor module of the embodiment of the present invention is in image 3 The semiconductor package 100 shown is mounted on a stack with figure 2 (a) The semiconductor package 200 shown.

[0052] The semiconductor module 100 is composed of a substrate 11 and a semiconductor chip 12 mounted on the upper surface of the substrate 11 . Connection terminals 2 for external connection are mounted on the lower surface of the substrate 11 .

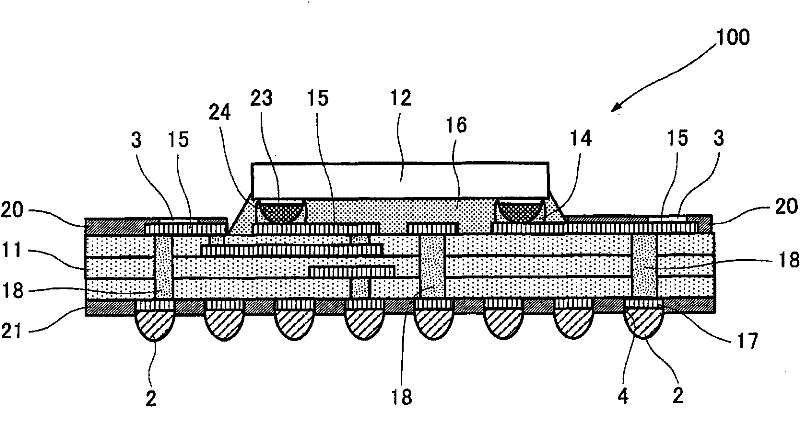

[0053] exist image 3 The details of the semiconductor package 100 are shown in .

[0054] In the semiconductor chip 12 , an integrated circuit formation region (not shown) in which semiconductor elements are formed is provided in the central portion of a chip substrate having a rectangular planar shape, and a plurality of chip terminals 23 are arranged outside it. The chip terminals 23 are formed of the same metal as that used to form the wiring of an integrated circuit, and are formed of aluminum, copper, or a laminated mate...

Embodiment approach 2

[0088] -Relationship between the inter-substrate joint portion 30 and the connection terminal 2-

[0089] exist Figure 11 to Figure 14 In , a cross-sectional view of the semiconductor package 100 on the lower side of the semiconductor module, a cross-sectional view of the semiconductor module, a top view of the transmission inspection, a detection example of a poor bonding state, and a detection example of a normal bonding state are shown as modifications of the present embodiment.

[0090] can also be like Figure 11 In that way, the diameter center of the pad 15 exposed from the opening 3 is deviated from the center of the connection terminal 2 , and the connection terminal 2 is hidden (included) under the pad 15 exposed from the opening 3 .

[0091] The inter-substrate joint portion 30 is exposed from the connection terminal 2 when seen through from above in a state mounted on the lower semiconductor package before melting.

[0092] In addition, in Figure 12 In the lam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More