Integrated panel type grid drive circuit applicable for charge sharing pixel

A gate drive circuit and gate technology, applied in static memory, instruments, static indicators, etc., can solve the problems of complex circuit structure and large layout area of shift register, and achieve the effect of simple circuit structure and simple circuit layout.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

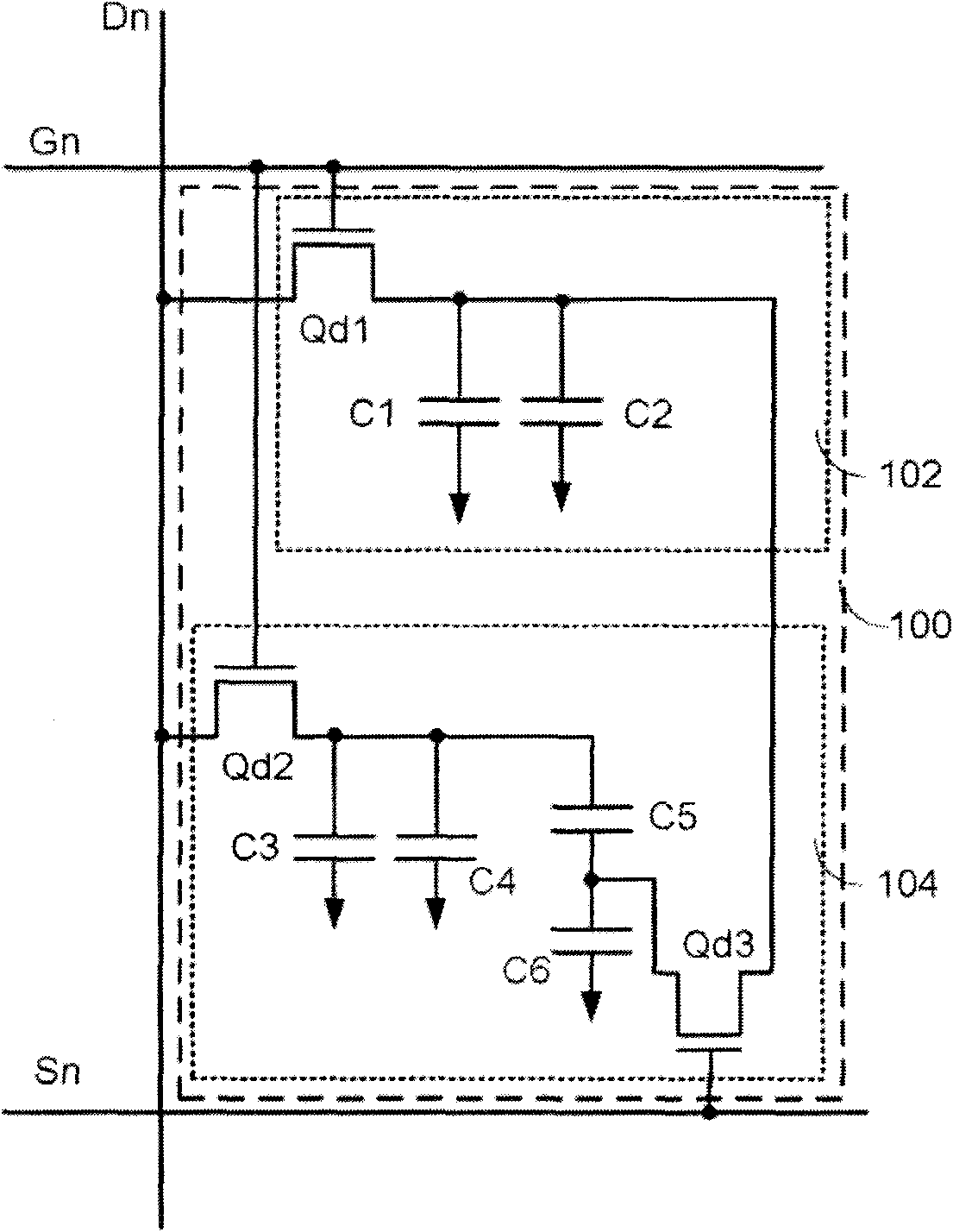

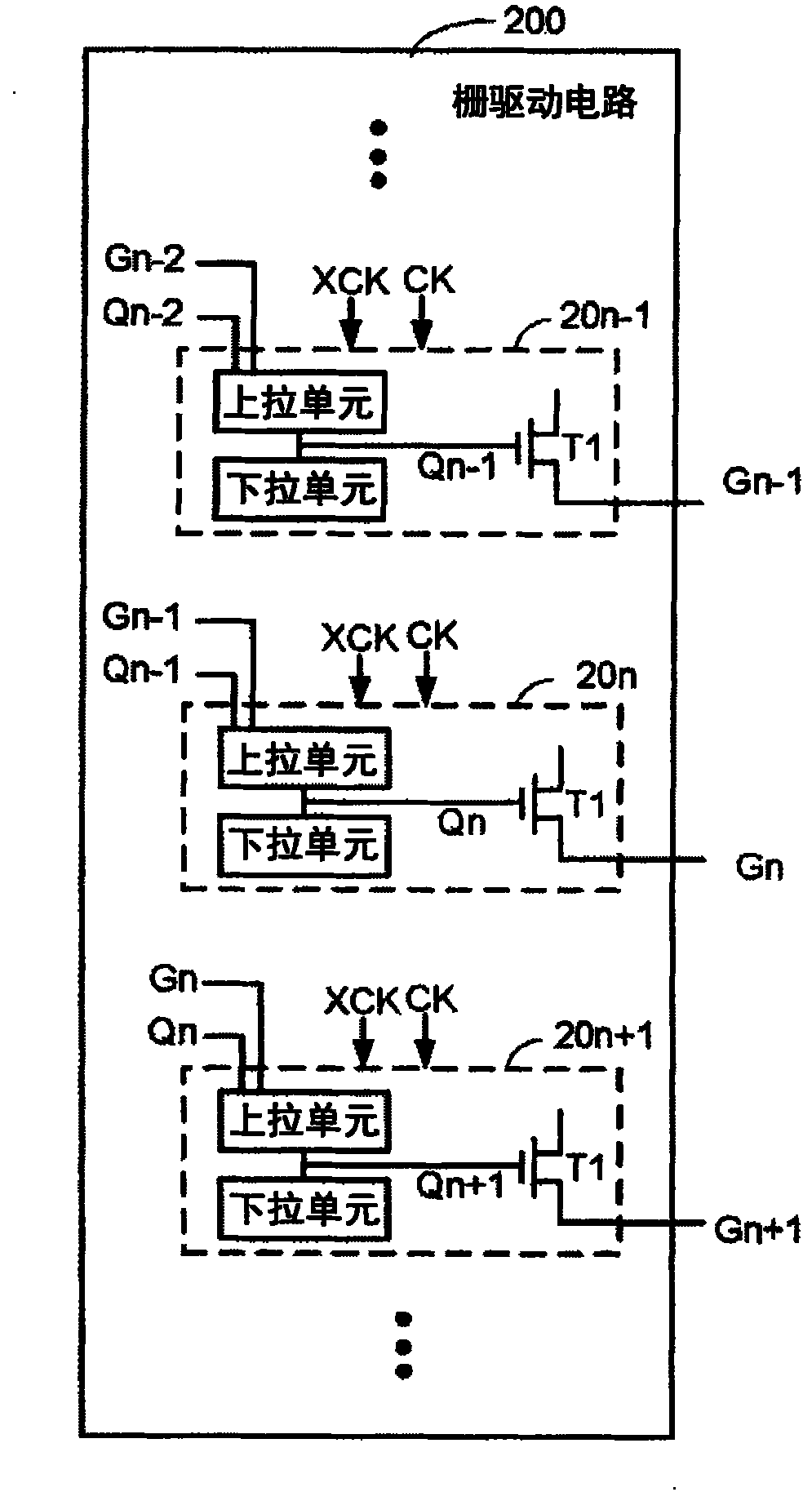

[0066] According to an embodiment of the present invention, the present invention proposes an integrated panel-type gate driving circuit applied to a charge-sharing pixel. The gate drive circuit on the GOA panel includes a plurality of shift registers, and each shift register can output a main gate drive signal and a sub gate drive signal that do not overlap with each other.

[0067] First, the present invention needs to generate 6 clock pulse signals, all of which have a duty cycle of 1 / 3. Furthermore, the phase difference between each clock pulse signal is 60 degrees. The six clock pulse signals are named as HC1, HC2, HC3, HC4, HC5, HC6 according to the phase sequence. Such as Figure 5 Shown is the phase relationship between the six clock pulse signals.

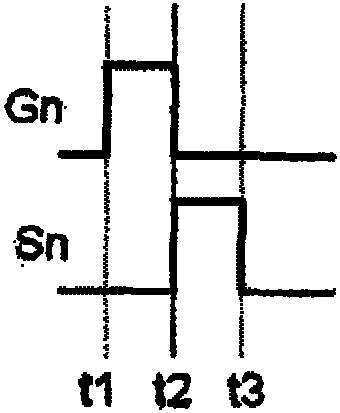

[0068] Please refer to Figure 6A and Figure 6B , which is a schematic diagram of the first embodiment of the shift register in the gate driving circuit of the present invention and its related signals. The nth shif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More