Package structure

A packaging structure and chip technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of severe heat dissipation, low thermal conductivity, and low heat dissipation of three-dimensional integrated circuits, and achieve reduced possibility and low stress Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The manufacture and use of the embodiments of the present invention are described below. It should be readily appreciated, however, that the embodiments of the invention provide many suitable inventive concepts that can be implemented in a wide variety of specific contexts. The specific embodiments disclosed are only used to illustrate the making and use of the present invention in specific ways, and are not intended to limit the scope of the present invention.

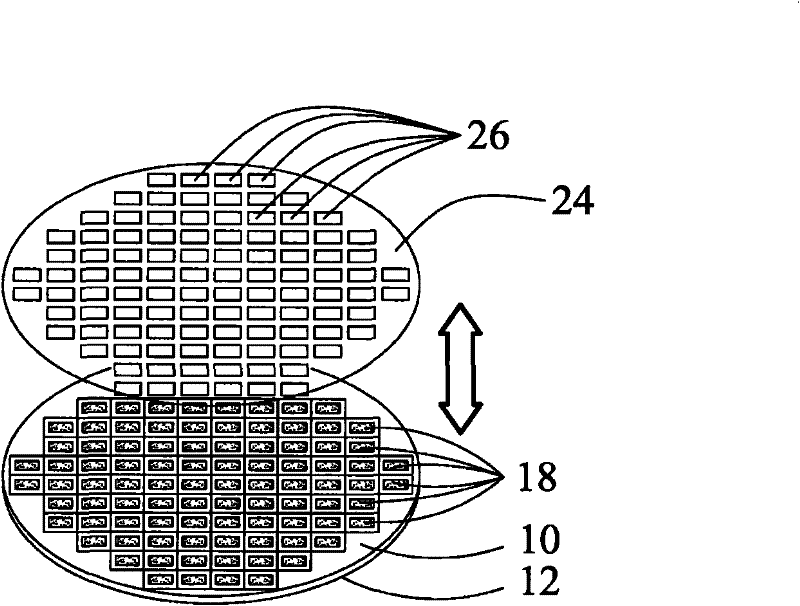

[0049] A new packaging structure and its manufacturing method are described below. Illustrates intermediate fabrication stages of an embodiment and details variations of the embodiments using diagrams. In different embodiments, the same reference numerals are used to refer to the same components.

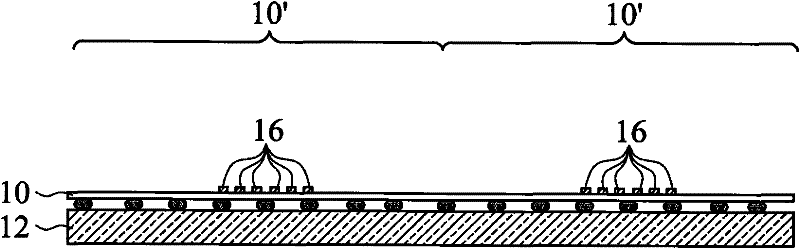

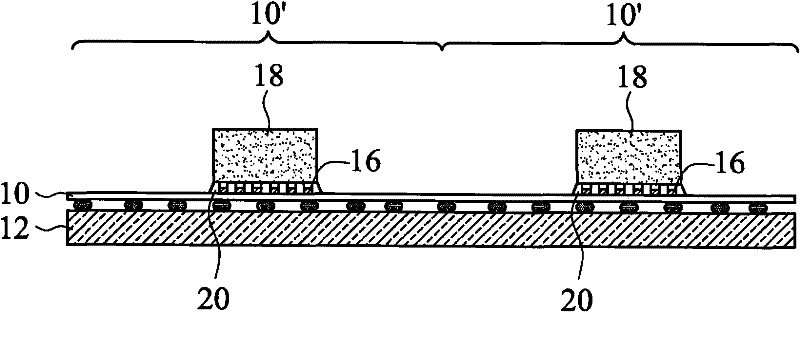

[0050] Please refer to figure 1 , a base chip 10 is assembled on a carrier chip 12 . The underlying wafer 10 may include integrated circuits (not shown), such as complementary metal-oxide-semiconductor (CMOS) tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More