Multi-ring-arranged double-integrated circuit (IC) chip packaging piece and production method thereof

A technology of chip package and production method, which is applied in the field of multi-circle arrangement carrierless double IC chip package, to achieve the effect of avoiding cross wire and open circuit, short heat conduction distance and reducing influence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

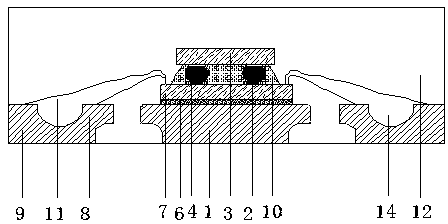

Embodiment 1

[0061] (1), wafer thinning

[0062] Using 8-inch to 12-inch thinning machine, adopts rough grinding, fine grinding and polishing anti-warping process, the wafer with bump chip is thinned to 250μm, rough grinding speed: 6μm / s, fine grinding speed: 1.0μm / s; the thickness of the wafer without bumps is 100μm, the rough grinding speed is 2μm / s, the fine grinding speed is 0.8μm / s, and the chip warpage prevention process is adopted.

[0063] (2), scribing

[0064] Wafers ≤8 inches use DISC 3350 double-knife dicing machine, and wafers from 8 inches to 12 inches use A-WD-300TXB dicing machine, and the scribing speed is controlled at ≤10mm / s.

[0065] (3), one-time loading

[0066] IC chips 7 with a carrier frame and no bumps are used for one-time chipping, and conductive adhesive 5 is used for one-time chipping. The equipment and process used for chipping and baking are the same as those of ordinary QFN.

[0067] (4), pressure welding

[0068] Carry out wire bonding for the ...

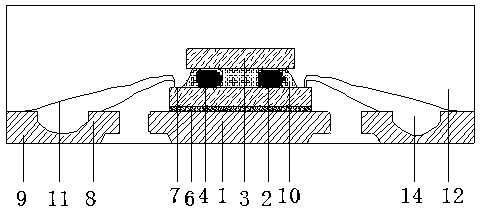

Embodiment 2

[0088] (1), wafer thinning

[0089] Using 8-inch to 12-inch thinning machine, using rough grinding, fine grinding and polishing anti-warping process, the wafer with bump chip is thinned to 250μm, rough grinding speed: 3μm / s, fine grinding speed: 0.6μm / s; the thickness of the wafer without bumps is 100 μm, the rough grinding speed is 4 μm / s, the fine grinding speed is 0.4 μm / s, and the chip warpage prevention process is adopted.

[0090] (2), scribing

[0091] Wafers ≤8 inches use DISC 3350 double-knife dicing machine, and wafers from 8 inches to 12 inches use A-WD-300TXB dicing machine, and the scribing speed is controlled at ≤10mm / s.

[0092] (3), one-time loading

[0093] Adopt QFN adhesive film (6) and IC chip (7) without concave and convex points, use a core loading machine with adhesive film (6) bonding process, and use a flip chip loading machine for the secondary core of the double chip. The bumps (4) of the IC chip (3) with bumps are dipped with solder (2) and plac...

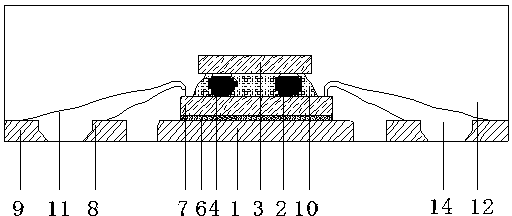

Embodiment 3

[0115] (1), wafer thinning

[0116] Using 8-inch to 12-inch thinning machine, using rough grinding, fine grinding and polishing anti-warping process, the wafer with bump chip is thinned to 250μm, rough grinding speed: 3μm / s, fine grinding speed: 0.6μm / s; the thickness of the wafer without bumps is 100 μm, the rough grinding speed is 4 μm / s, the fine grinding speed is 0.4 μm / s, and the chip warpage prevention process is adopted.

[0117] (2), scribing

[0118] Wafers ≤8 inches use DISC 3350 double-knife dicing machine, and wafers from 8 inches to 12 inches use A-WD-300TXB dicing machine, and the scribing speed is controlled at ≤10mm / s.

[0119] (3), one-time loading

[0120] IC chips 7 with a carrier frame and no bumps are used for one-time chipping, and conductive adhesive 5 is used for one-time chipping. The equipment and process used for chipping and baking are the same as those of ordinary QFN.

[0121] (4), pressure welding

[0122] With embodiment 1.

[0123] (5), t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More