Fault Diagnosis Method for Analog Circuits Based on Echo State Network Synchronous Optimization

An echo state network, a technology for simulating circuit faults, applied in genetic models, measuring electricity, measuring electrical variables, etc., can solve problems such as low diagnostic accuracy, achieve high diagnostic accuracy and improve adaptability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

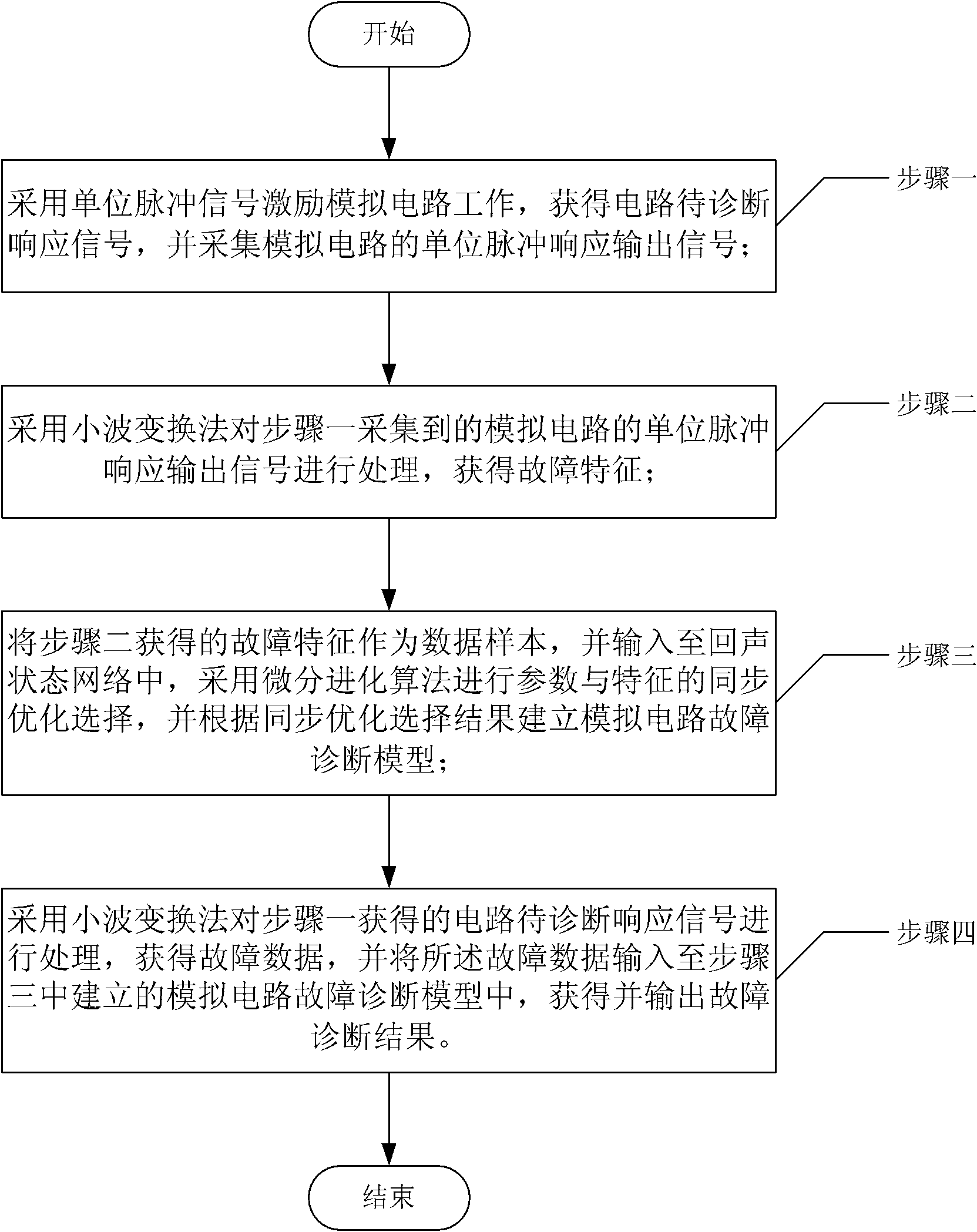

[0047] Specific implementation mode 1. Combination figure 1 Illustrate this specific embodiment, the analog circuit fault diagnosis method based on echo state network synchronous optimization, it is realized by the following steps:

[0048] Step 1, using a unit pulse signal to stimulate the analog circuit to work, obtaining a diagnostic response signal of the circuit, and collecting a unit pulse response output signal of the analog circuit;

[0049] Step 2, using the wavelet transform method to process the unit impulse response output signal of the analog circuit collected in step 1 to obtain fault characteristics;

[0050] Step 3. The fault characteristics obtained in step 2 are used as data samples, and input into the echo state network, and the differential evolution algorithm is used for synchronous optimization selection of parameters and features, and an analog circuit fault diagnosis model is established according to the synchronous optimization selection results;

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More