Method for forming and correcting TSV (through silicon via)

A pattern and oxide layer technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as sidewall insulation failure, affecting TSV interconnect characteristics, etc., to reduce difficulty and reduce the possibility of failure Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

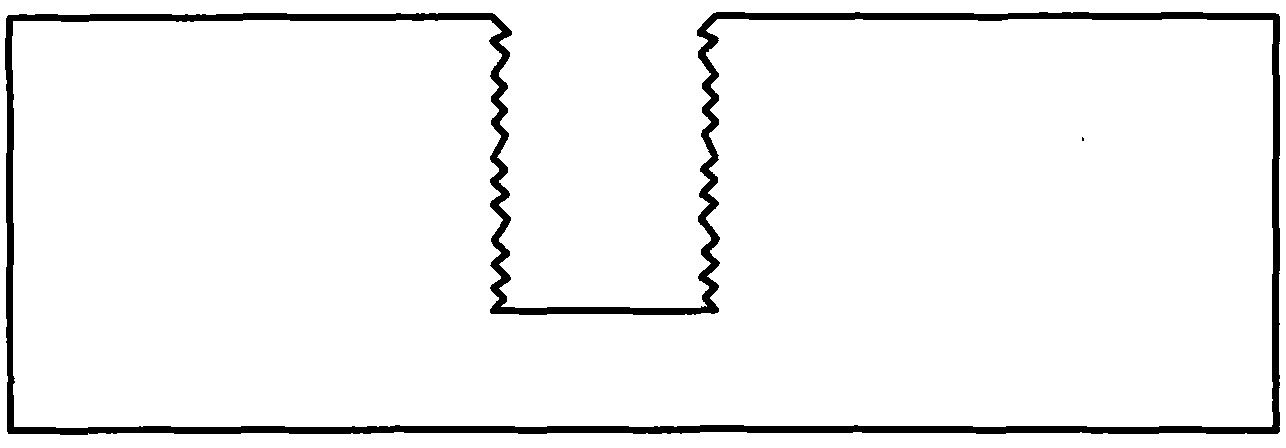

[0026] Since the semiconductor substrate usually has a considerable thickness, the process for forming the through hole is a plasma etching process, usually a Bosch etching technique (Bosch process), and Bosch etching can form a vertical via hole with a relatively high aspect ratio. , but the through hole formed by the existing process has a scallop shape, which makes the interconnection characteristics of the subsequent TSV low.

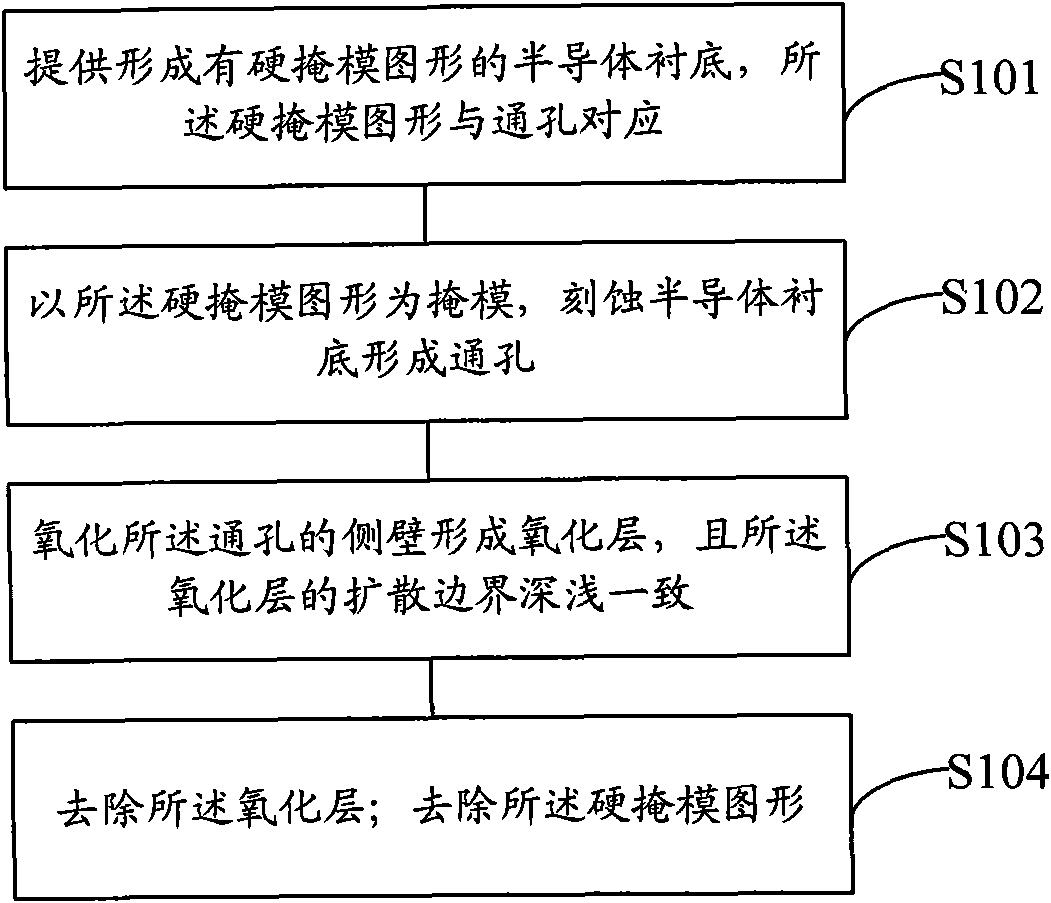

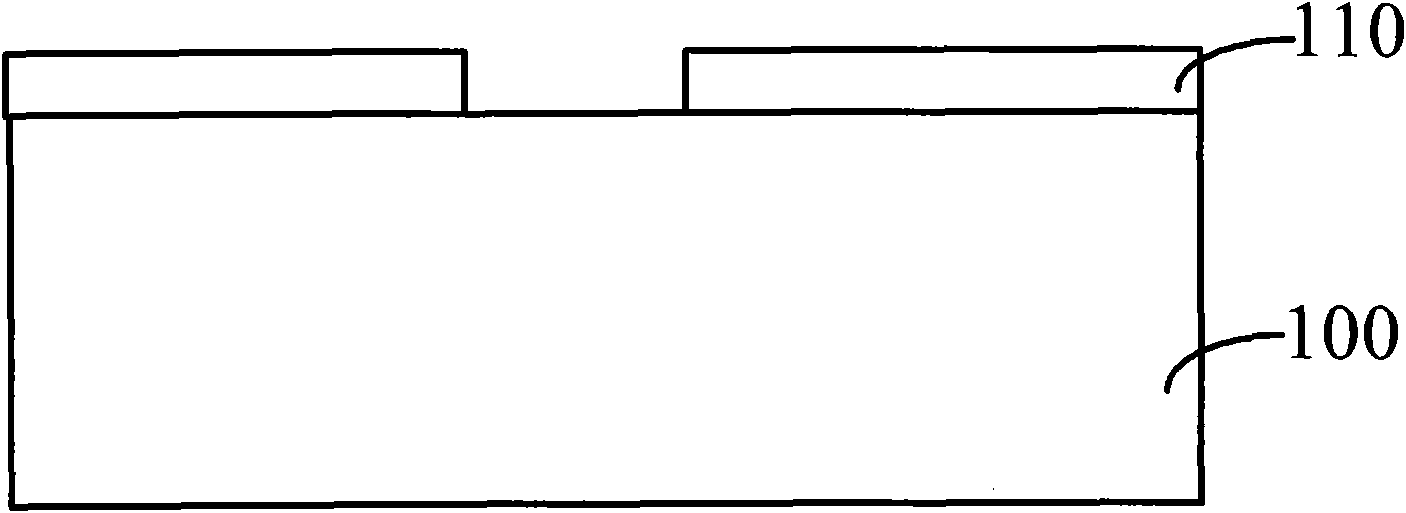

[0027] To this end, the present invention provides a method for forming a TSV through hole, comprising: providing a semiconductor substrate formed with a hard mask pattern, the hard mask pattern corresponding to the through hole; using the hard mask pattern as a mask , etching the semiconductor substrate to form a through hole; oxidizing the sidewall of the through hole to form an oxide layer, and the diffusion boundary of the oxide layer is uniform in depth; removing the oxide layer; removing the hard mask pattern.

[0028] The method for forming t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More