Semiconductor element packaging structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

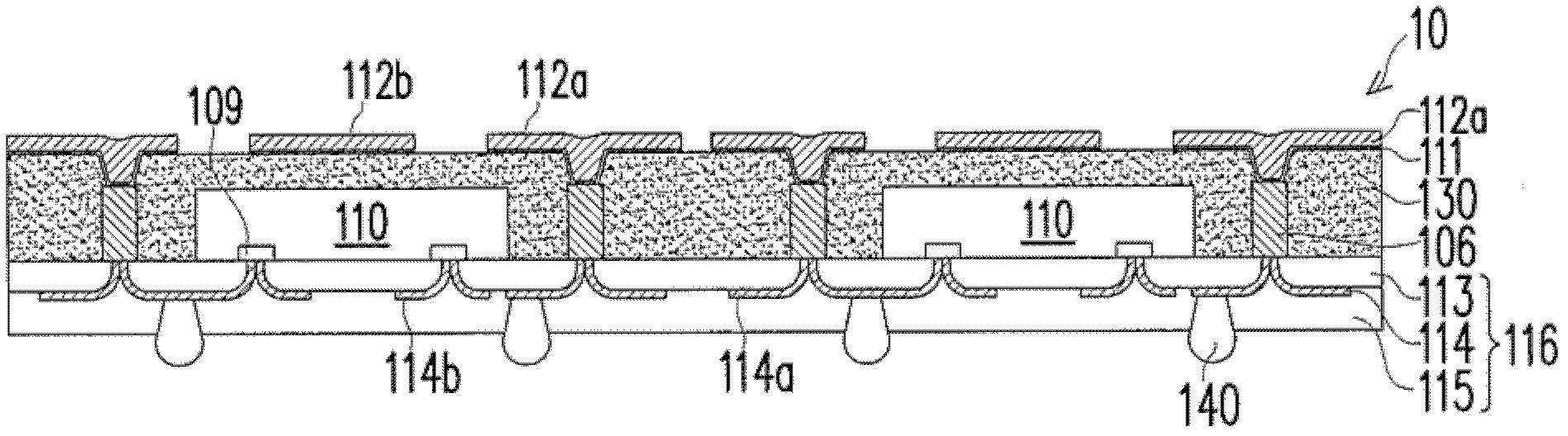

[0039] figure 1 A Wafer Level Packaging (WLP) 10 according to an embodiment of the present invention is described. The packaging structure 10 at least includes a chip (also called a die) 110, an encapsulant 130 covering the chip 110, a plurality of posts 106 embedded in the encapsulant 130, and an interconnect pattern 112a connected to the posts 106. and a trace pattern 112 b and a redistribution layer (RDL) 116 . The redistribution wiring layer 116 includes a first dielectric layer 113 , a conductive layer 114 and a second dielectric layer 115 . In other embodiments, the redistribution wiring layer 116 may be a single-layer structure (only including the conductive layer 114 ).

[0040] The WLP structure 10 may include forming a seed layer 111 between the interconnect pattern 112 a and the encapsulant 130 , between the interconnect pattern 112 a and the pillars 106 , and between the wire pattern 112 b and the encapsulant 130 . Through the interconnection pattern 112a, other...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More