Packaging method and structure of chip

A packaging method and packaging structure technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of sharing large-area pins on the same substrate, poor temperature performance, and inability to have thermal conductivity, etc., to achieve Good heat dissipation protection, high package stability, and the effect of avoiding package deformation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

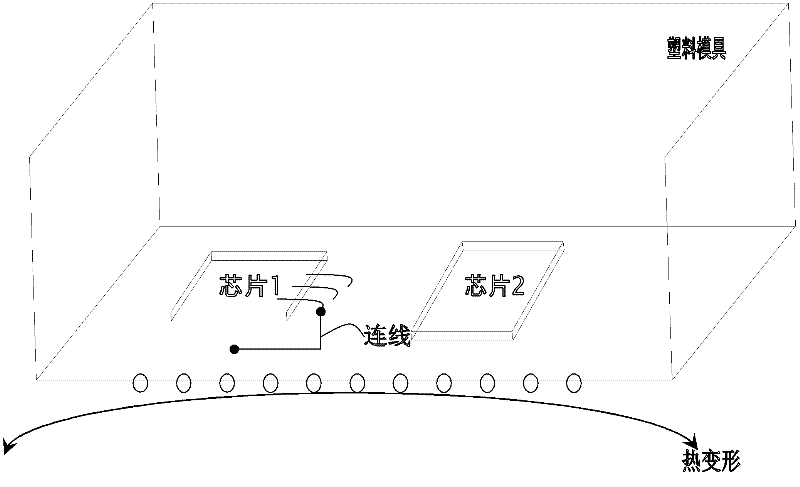

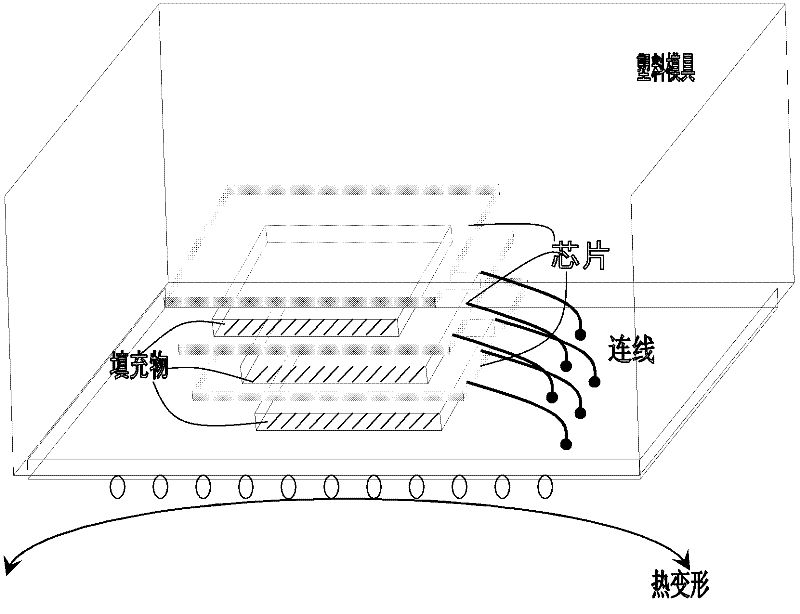

[0038] The invention provides a chip packaging method, the method comprising the following steps:

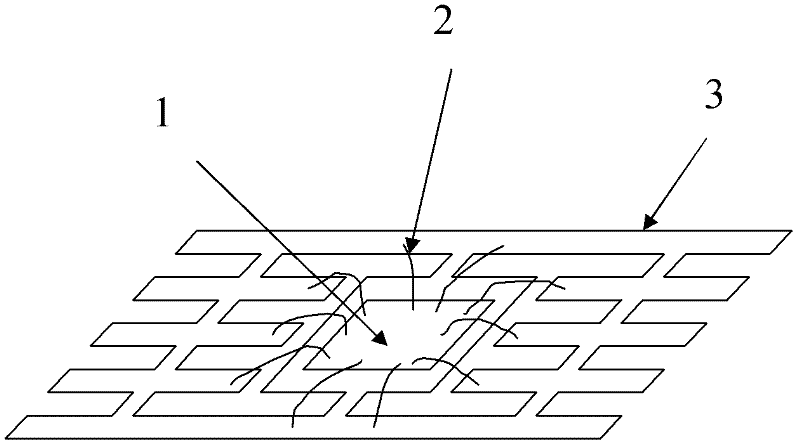

[0039] 1) Chip 1 is mounted on a separate chip lead frame or substrate (lead frame 3 or substrate 4);

[0040] 2) Connect one side of the chip lead frame or substrate obtained in step 1) to the external packaging substrate 6, one or more chip lead frames or substrates.

[0041] The chip lead frame or substrate is directly used as an external package pin through the metal pins arranged on the chip lead frame or substrate through the pin hole provided on the package substrate, or the chip lead frame or substrate is connected to the soldering part of the external package through wiring. Ball 5 on.

[0042] 3) Compound filling is performed on the chip lead frame or the substrate in step 2).

[0043] When there are multiple chip lead frames or substrates, the chip lead frames or substrates are placed vertically on the plane of the external package; multiple chip lead frames or subs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More