Consistency maintenance device for multi-kernel processor and consistency interaction method

A multi-core processor and maintenance device technology, applied in the computer field, can solve problems such as difficulty in reducing the delay of consistent interaction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

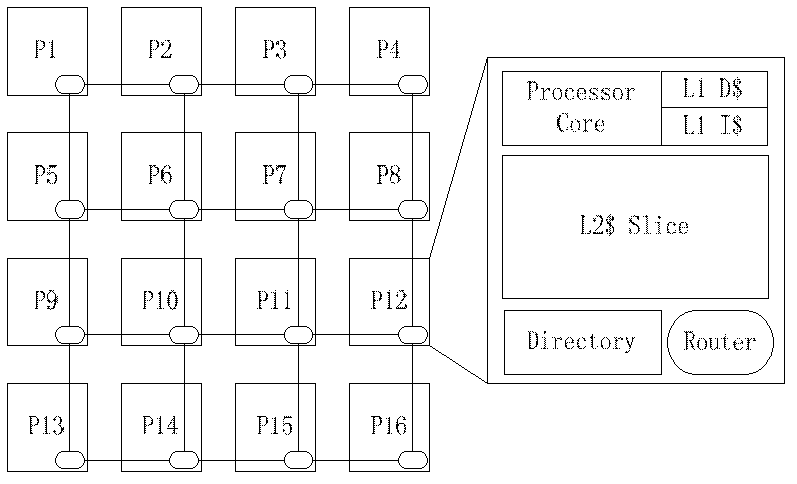

[0070] see Figure 1 to Figure 15 As shown, the present invention is a consistency maintenance device for a multi-core processor, including a global directory, a node directory, a directory controller, a node prediction cache, a node shared historical information cache, a last written node pointer, and a node suspension pointer. Including the following aspects:

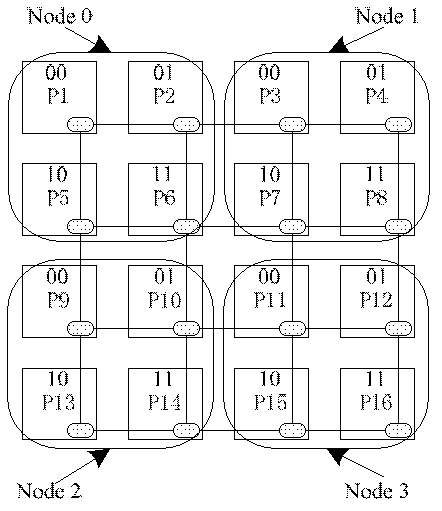

[0071] (a) Node division method

[0072] All cores on-chip are divided into multiple nodes, each node contains 2 n (n≥1) cores, assuming there are N cores on the chip (N is 2 n Integer multiples of ), then the processor contains nodes and N cores form a 2-D MESH array. 2 within a node n The kernels use n-bit binary numbers to encode indexes within the node. For example, when n=2, the four kernels in the node are coded as 00, 01, 10, and 11, respectively. There is a parallel relationship between multiple nodes at the same level, such as figure 2 .

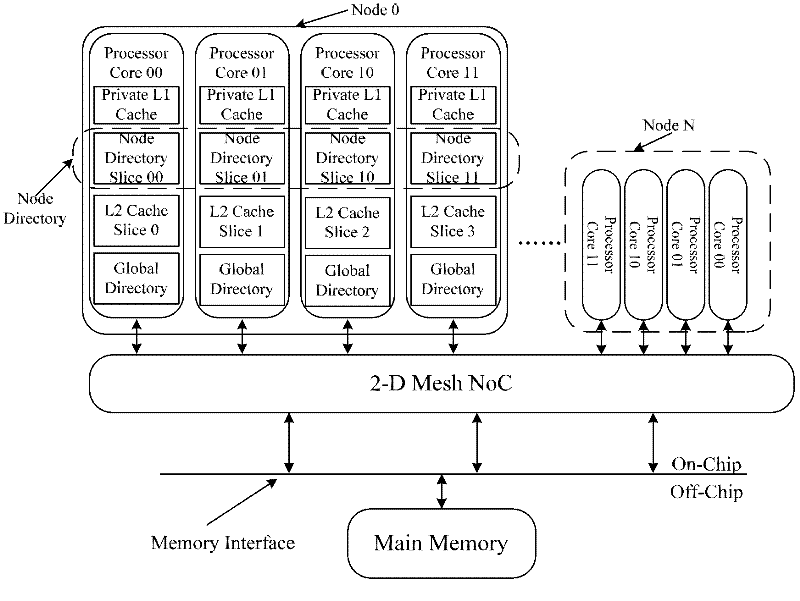

[0073] (b) Double directory structure

[0074] Such as im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More