FPGA (Field Programmable Gate Array) configuration circuit structure

A technology for configuring circuits and circuits, applied to logic circuits using specific components, logic circuits using basic logic circuit components, etc., can solve the problems of uncertain frame length, unfavorable device scale expansion, etc., to reduce design complexity and shorten Configuration time, easy to scale effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

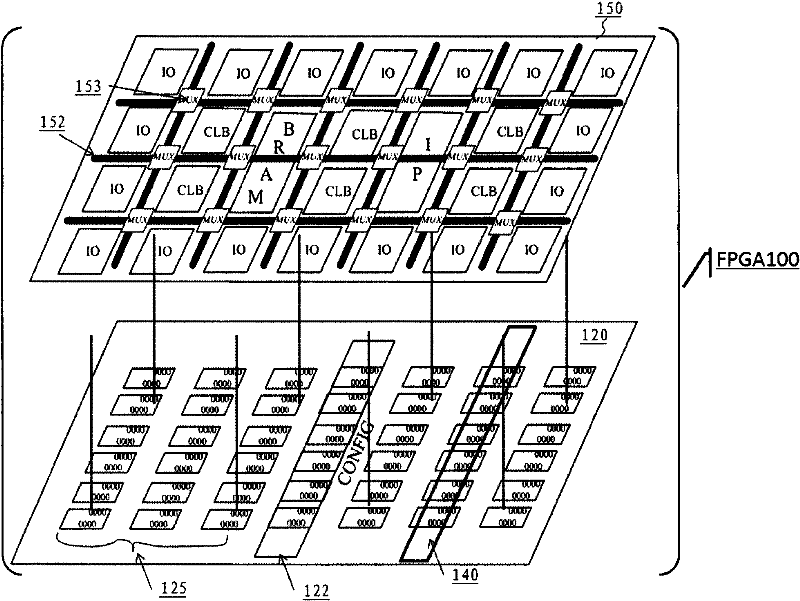

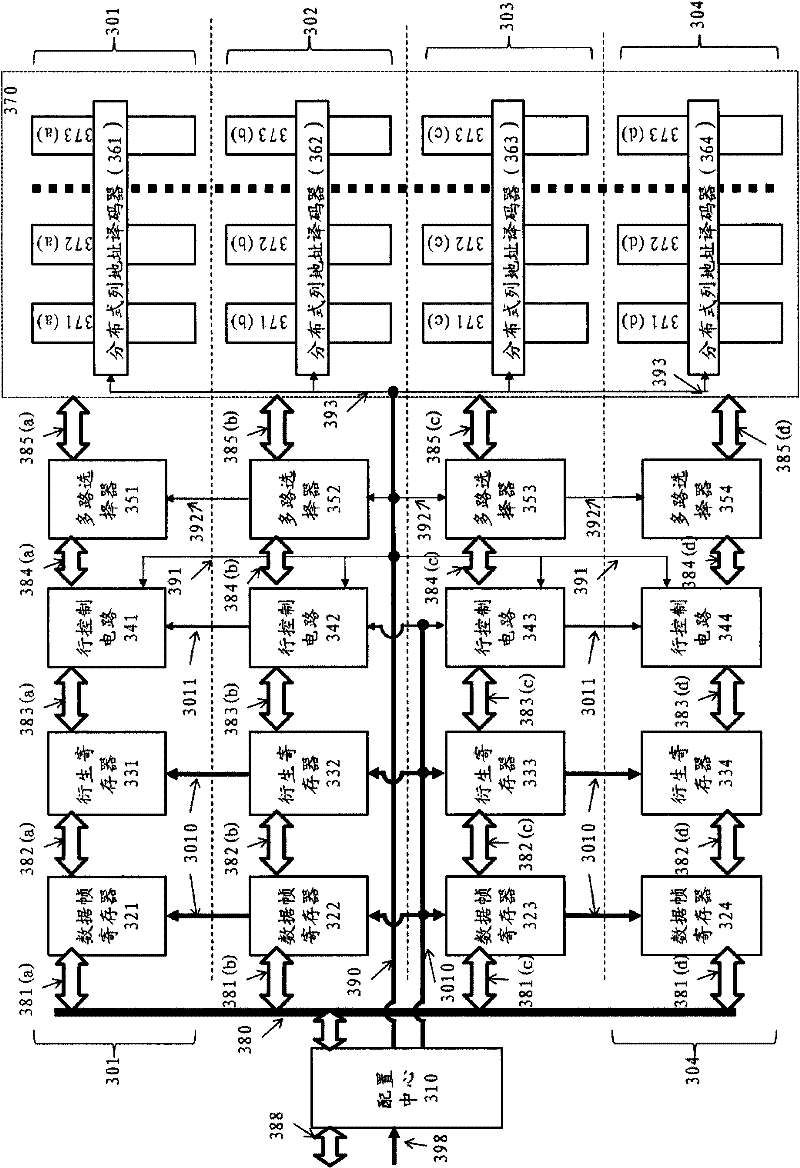

[0034] The present invention is an FPGA configuration circuit architecture, which specifically includes: a configuration memory, a configuration center, a distributed column address decoder, a frame data register, a derivative register, a row control circuit and a multiplexer. exist image 3 The relationship between these circuit modules can be seen in,

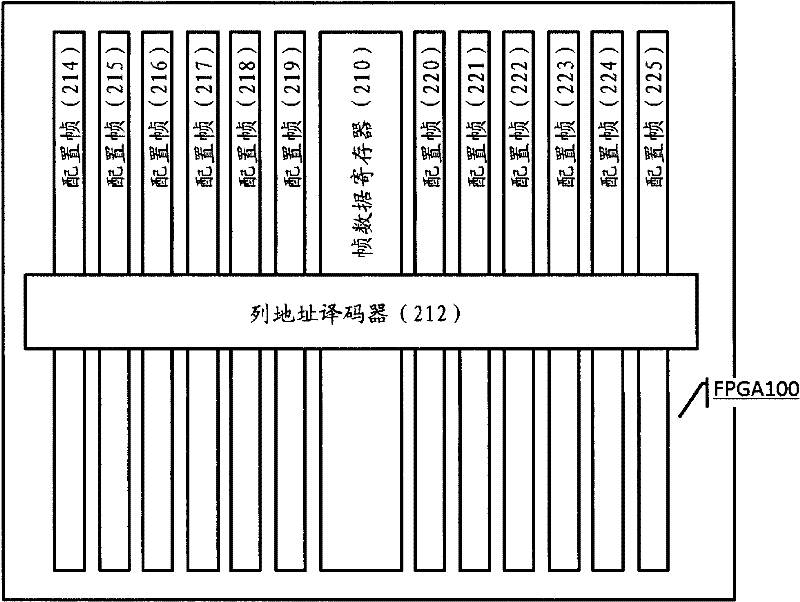

[0035] Configuration memory: used to store user configuration data and control the programmable logic circuit in the FPGA to realize the logic function designed by the user according to the configuration data; the configuration memory is divided into several rows and several columns, and each column is further divided into multiple configurations Storage cell matrix; the configuration memory adopts row address, column address and auxiliary address to address and locate the configuration storage cell matrix; the auxiliary address is the address for configuring the storage cell matrix;

[0036] The distributed column address d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More