Dual programmable subtraction frequency divider

A frequency divider and subtraction technology, applied in the field of microelectronics, can solve the problems of increased circuit complexity and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

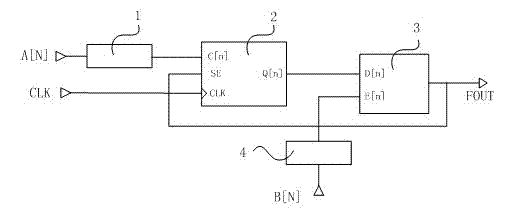

[0023] Such as figure 1 As shown, a dual-programmable subtraction divider includes a preset minus-1 counter 2, a logic comparator 3 and two registers 1 and 4.

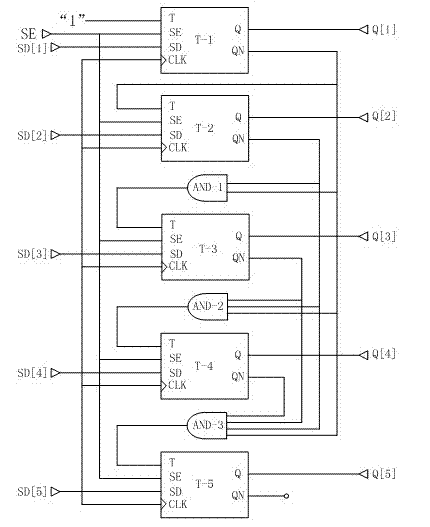

[0024] Such as figure 2 As shown, the preset decrement counter 2 includes five-stage presettable T flip-flops T-1~5 and three-stage AND gates AND-1~3.

[0025] Presettable T flip-flops T-1~5 include data input port T, clock input port CLK, enable signal input port SE, preset number input port SD, non-inverting output port Q, and inverting output port QN; When the input port SE is valid, under the action of the clock signal, the signal of the preset number input port SD is directly output to the same-phase output port Q; when the enable signal input port SE is invalid, under the action of the clock signal, the signal of the data input port T is directly output Output to non-inverting output port Q.

[0026] The enable signal input ports SE of the five-stage presettable T flip-flops T-1~5 are connected as the enable ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More