SPICE (Simulation Program with Integrated Circuit Emphasis) testing structure of MOS (Metal Oxide Semiconductor) device

A technology of MOS devices and test structures, which is applied in the field of SPICE test structures, can solve problems such as waste of area, achieve the effects of saving area, avoiding mutual influence, and improving test accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

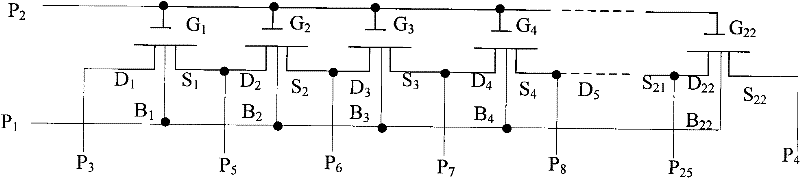

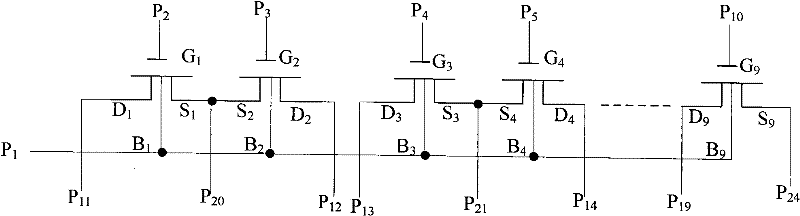

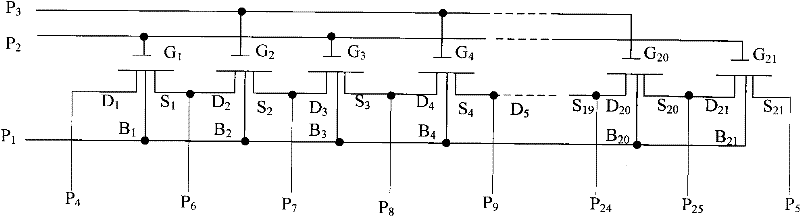

[0026] The SPICE test structure of the MOS device proposed by the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in very simplified form and use imprecise ratios, which are only used for the purpose of conveniently and clearly assisting in describing the embodiments of the present invention.

[0027] The core idea of the present invention is to provide a SPICE test structure of MOS devices, the test structure includes a plurality of MOS devices arranged in sequence and a plurality of pins, the substrates of the plurality of MOS devices are connected together; the arrangement position is The gates of the odd-numbered MOS devices are connected together; the gates of the even-numbered MOS devices are connected together; the source of the previ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More