Semiconductor chip and structure for mounting same

A mounting structure and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problem that conductive particles are difficult to be captured between electrodes, and achieve the effect of suppressing insufficient flow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

[0093]

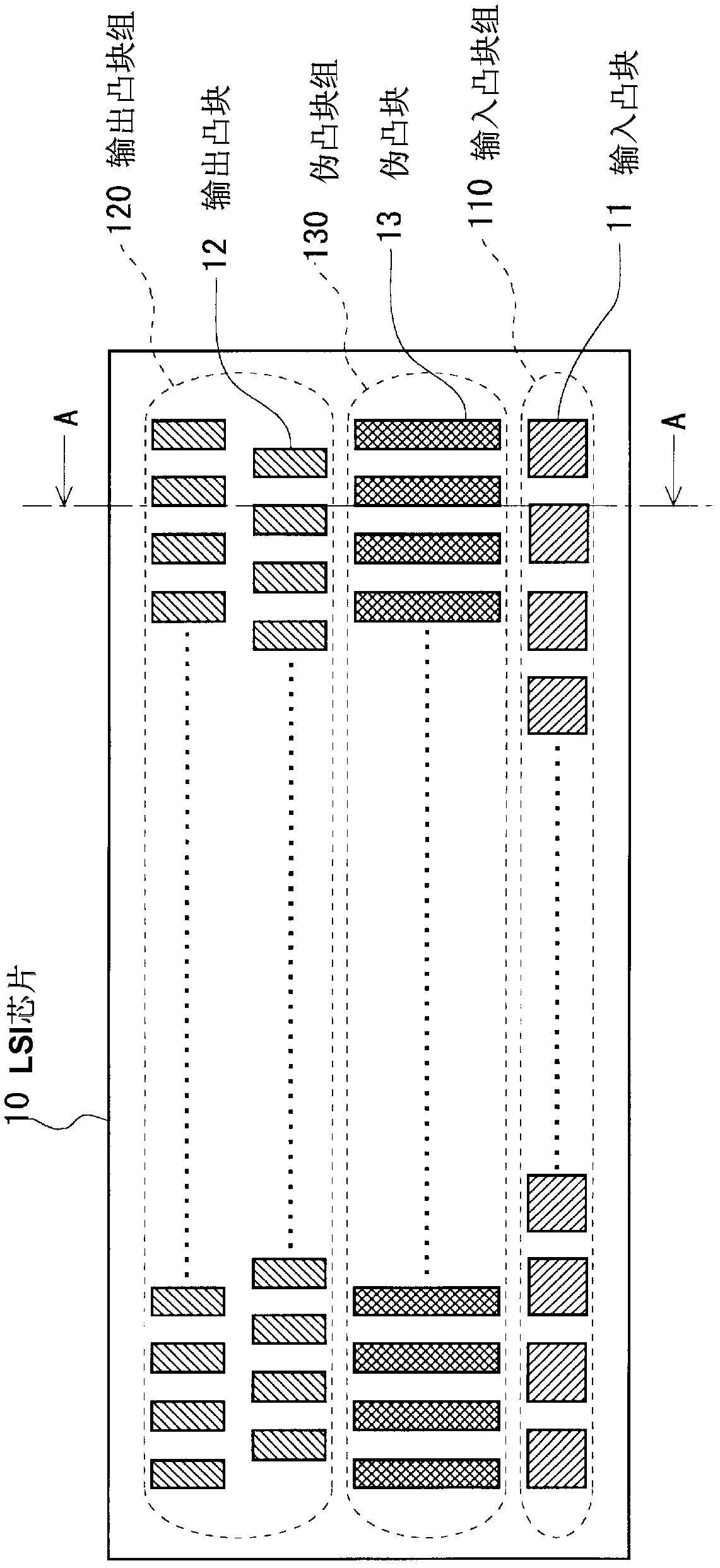

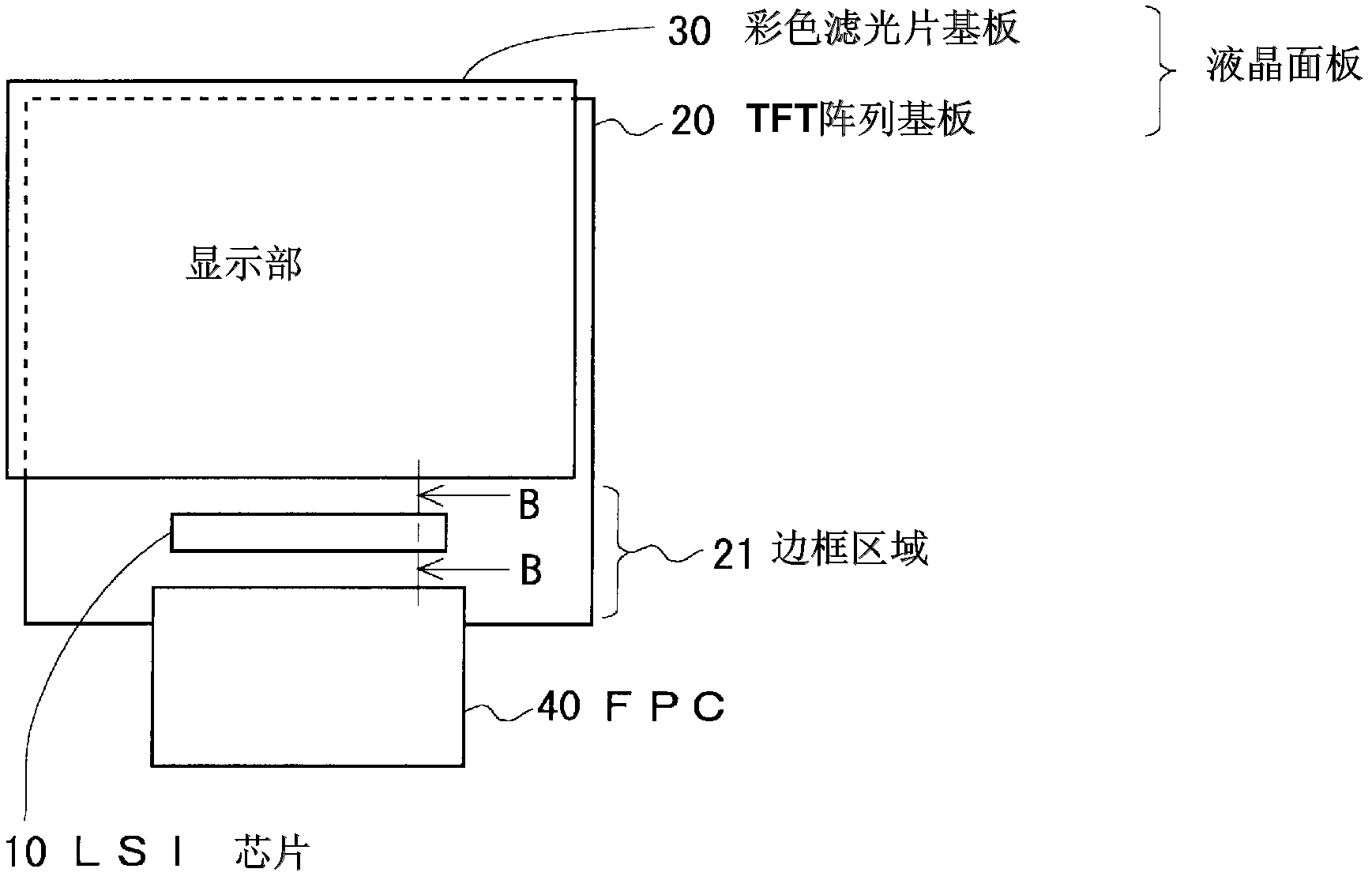

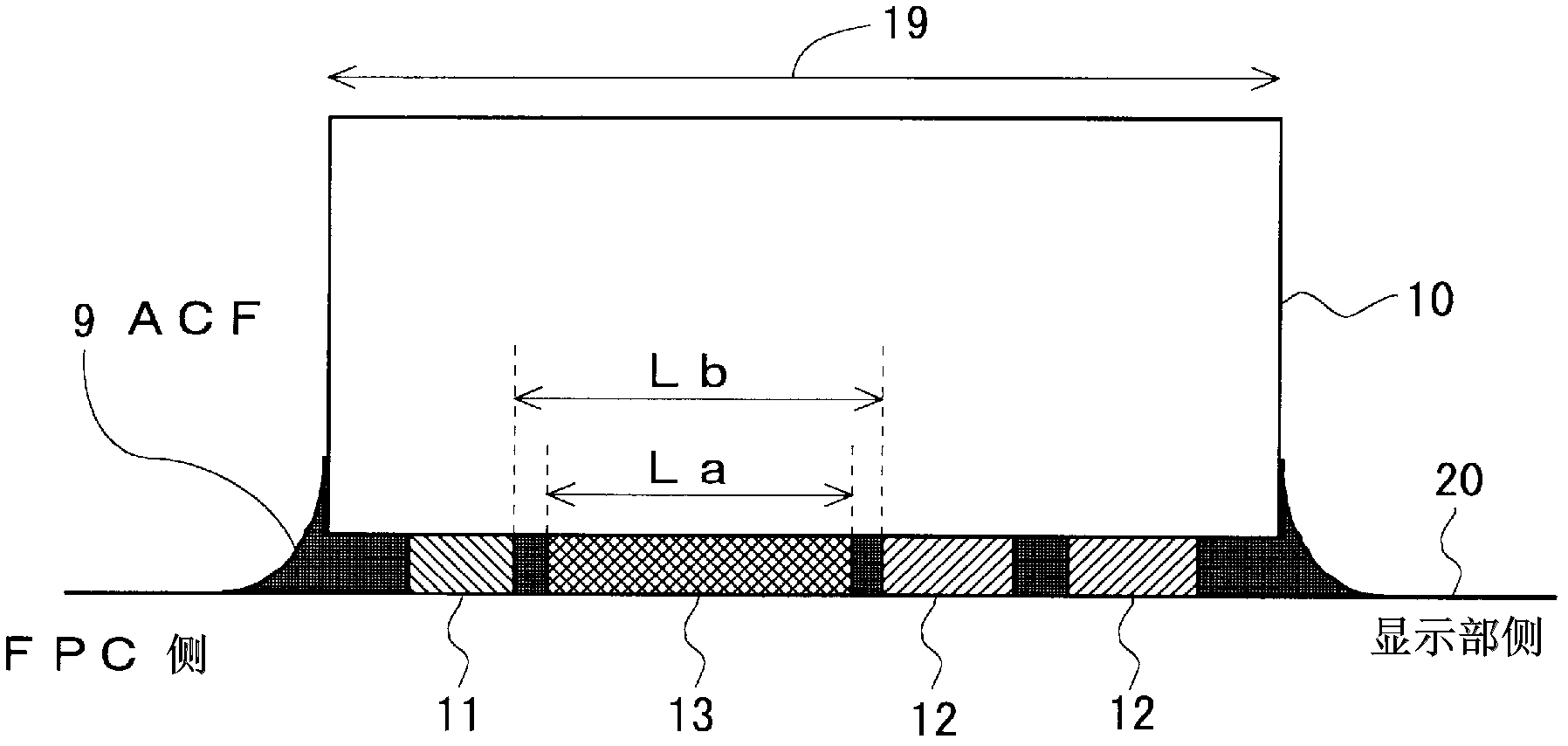

[0094] figure 2 It is a plan view of a liquid crystal module including an LSI chip (semiconductor chip) according to the first embodiment of the present invention. This liquid crystal module includes a liquid crystal panel, an LSI chip 10 and an FPC (Flexible Printed Circuit: flexible printed circuit) 40 . The liquid crystal panel includes: a TFT array substrate 20 that includes pixel electrodes (display electrodes) and is formed with a TFT array; The color filter substrate 30 of the opposite electrode. Both the TFT array substrate 20 and the color filter substrate 30 are glass substrates. Additionally, if figure 2 As shown, the TFT array substrate 20 is larger in plan view than the color filter substrate 30 . A display unit is provided in a region where the TFT array substrate 20 and the color filter substrate 30 overlap in a plan view. The area on the TFT array substrate 20 that is not opposite to the color filter substrate 30 is generally called a "frame"....

no. 2 approach

[0106] Figure 7 It is a bottom view of the LSI chip 10 according to the second embodiment of the present invention. In this embodiment, if Figure 7 As shown, the dummy bumps 13 are provided only near one short side and the other short side of the bottom surface of the LSI chip 10 . That is, the plurality of bumps 13 included in the bump group 130 of the first embodiment described above (refer to figure 1 ) are formed on the bottom surface of the LSI chip 10 on the outermost two bumps 13 . The configuration other than that is the same as that of the above-mentioned first embodiment, so description thereof will be omitted.

[0107] The more dummy bumps 13 that suppress the flow of the ACF resin from the central portion to the short sides are provided in the area between the input bump group 110 and the output bump group 120, the more reliable the connection between the LSI chip 10 and the TFT array substrate 20 will be. The higher the sex. However, the greater the number...

no. 3 approach

[0109] Figure 8It is a bottom view of the LSI chip 10 according to the third embodiment of the present invention. Various restrictions can be imposed on the formation of the bumps on the bottom surface of the LSI chip 10 . For example, the length of the long side of the bump may be limited to a predetermined length or less. In such a case, the distance between the input bump group 110 and the dummy bump group 130 or the distance between the output bump group 120 and the dummy bump group 130 becomes large, and it can be considered that the ACF resin moves from the center to the short side. The large flow on the side is not hindered. Therefore, in this embodiment, if Figure 8 As shown, the dummy bump group 130 is formed as follows: the dummy bumps 13 arranged on one long side of the bottom surface of the LSI chip 10 and the dummy bumps 13 arranged on the other long side of the bottom surface of the LSI chip 10 alternately. configuration. The configuration other than that ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More