Integrated circuit for emulating resistor

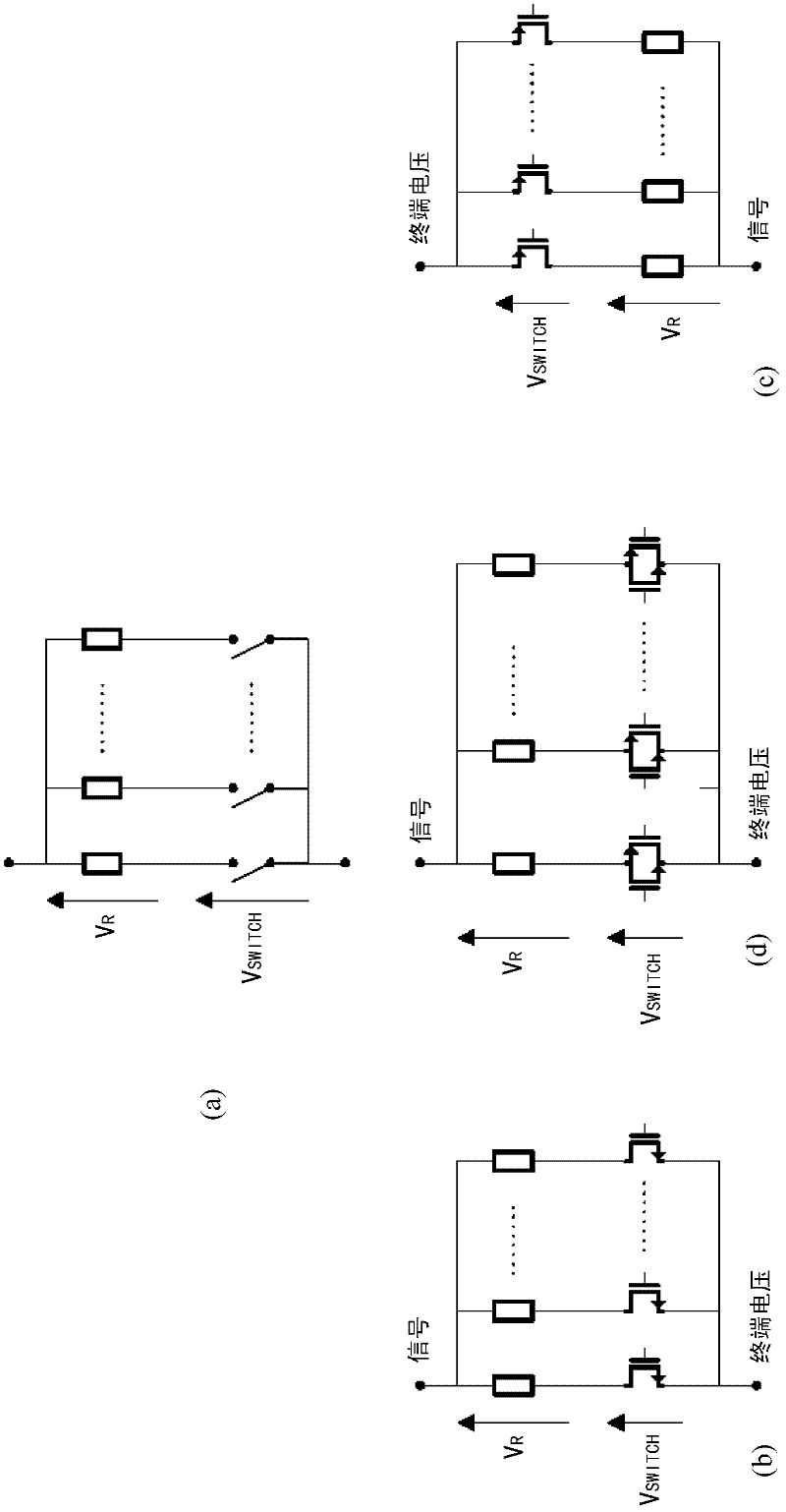

A technology of integrated circuits and simulated resistors, applied in impedance converters, electrical components, impedance matching networks, etc., and can solve problems such as nonlinear current-voltage characteristics and changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

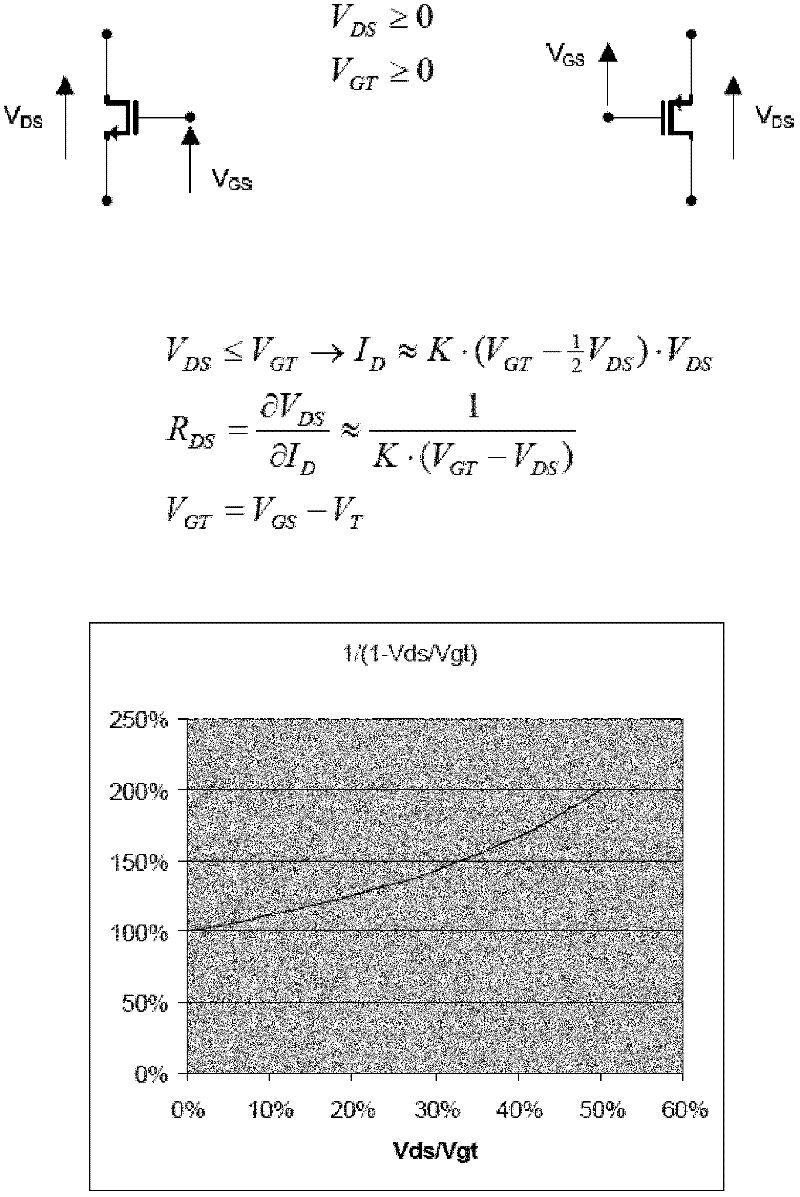

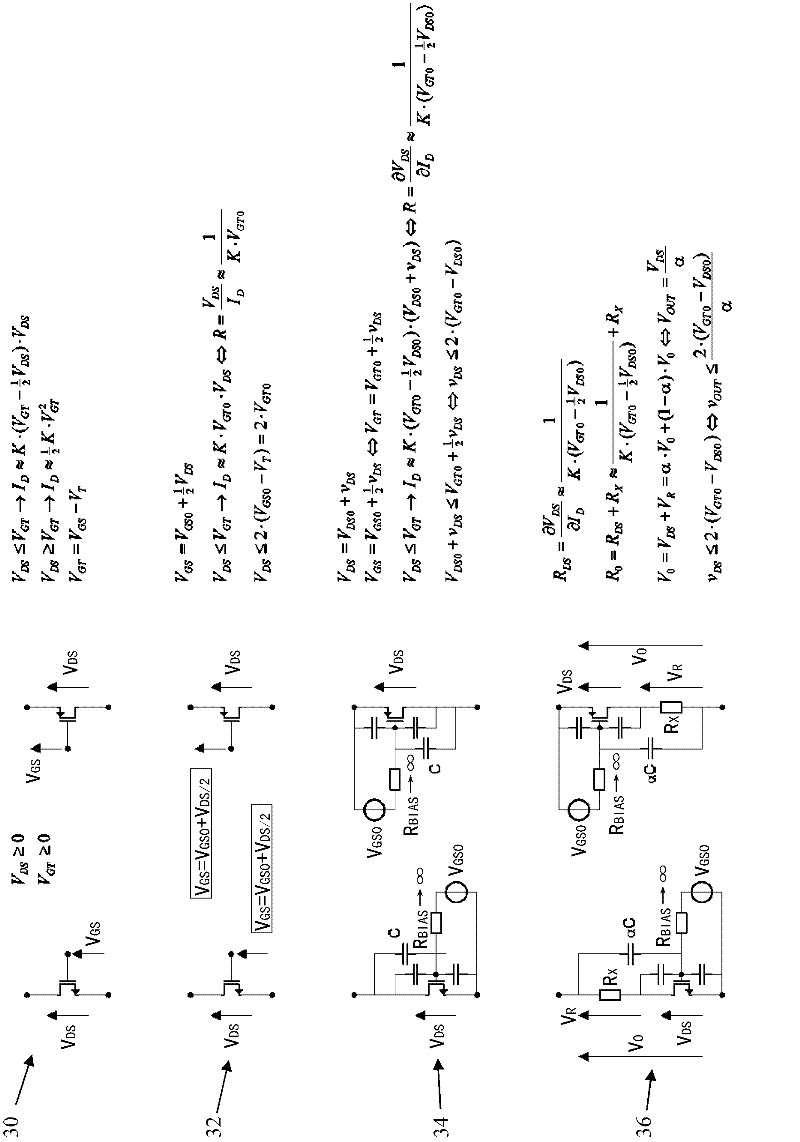

[0066] The present invention provides an integrated circuit for simulating a resistor based on the drain-source resistance of a transistor. The transistor is biased to operate in its linear region and a voltage dependent on the AC source-drain voltage is added to the gate voltage, thereby improving the linearity of the drain-source resistance with respect to the drain-source voltage Spend. Modifications to the gate voltage can be used to alter the transfer function such that the first order part of the dependence of the drain-source resistance on the drain-source voltage is substantially removed.

[0067] Figure 3a It is shown step-by-step how to linearize the resistance of a MOS transistor by superimposing a portion of the signal voltage at its drain to its gate. The equations relate to ideal square-law MOS characteristics.

[0068] Figure 3a Analysis of both NMOS and PMOS structures is shown. for equal to V GSO +v DS / 2V GS , the on-resistance of the MOS transistor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More