Method and system for verifying register transfer level (RTL) of Ethernet exchange chip queue manager

A technology for exchanging chips and verification methods, which is applied in the field of computer networks, can solve the problems of difficult positioning and error checking, low verification efficiency, difficulty in automatic and accurate detection of output traffic, etc., and achieves the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

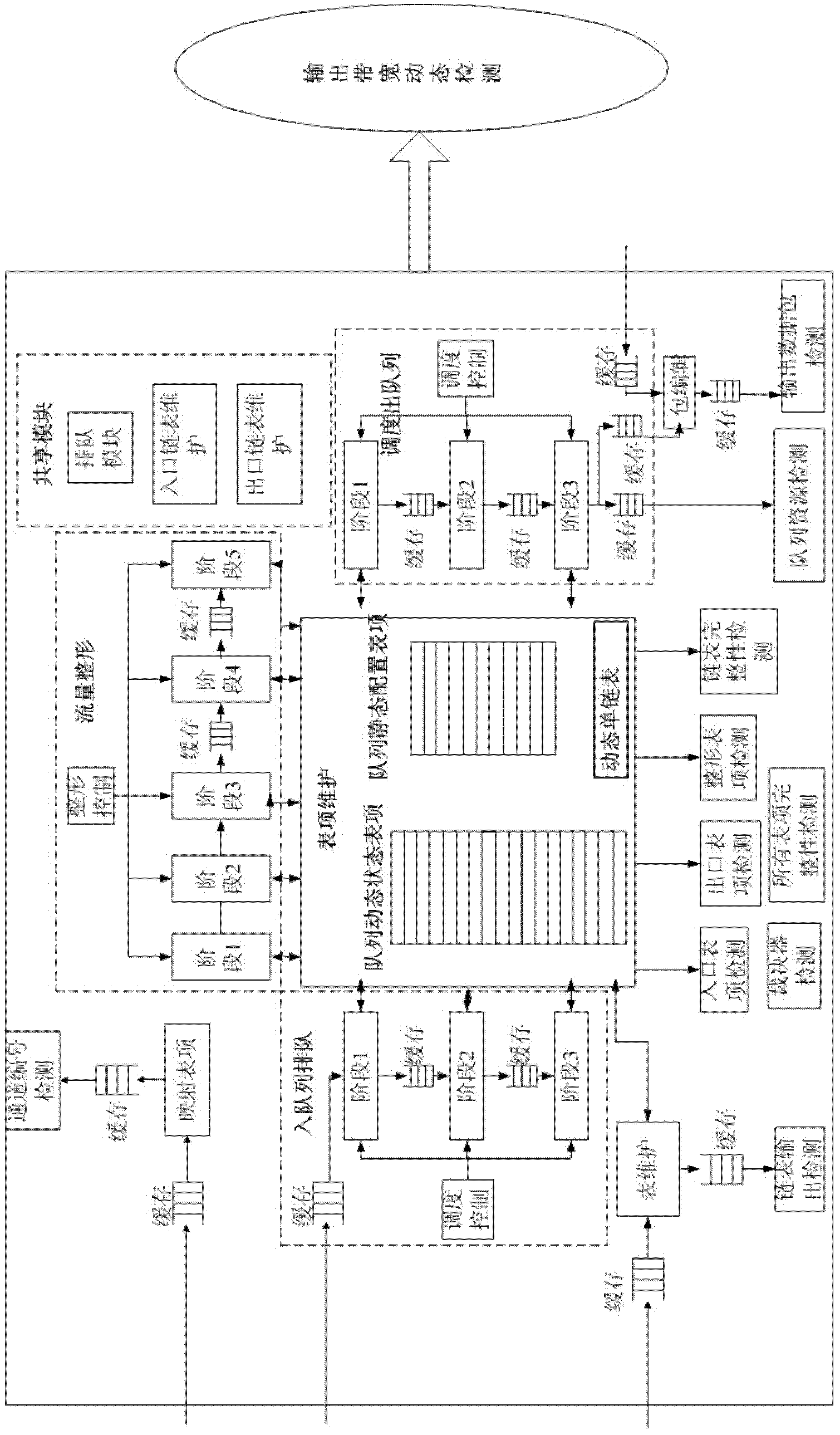

[0029] The technical solutions in the preferred embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings of the present invention.

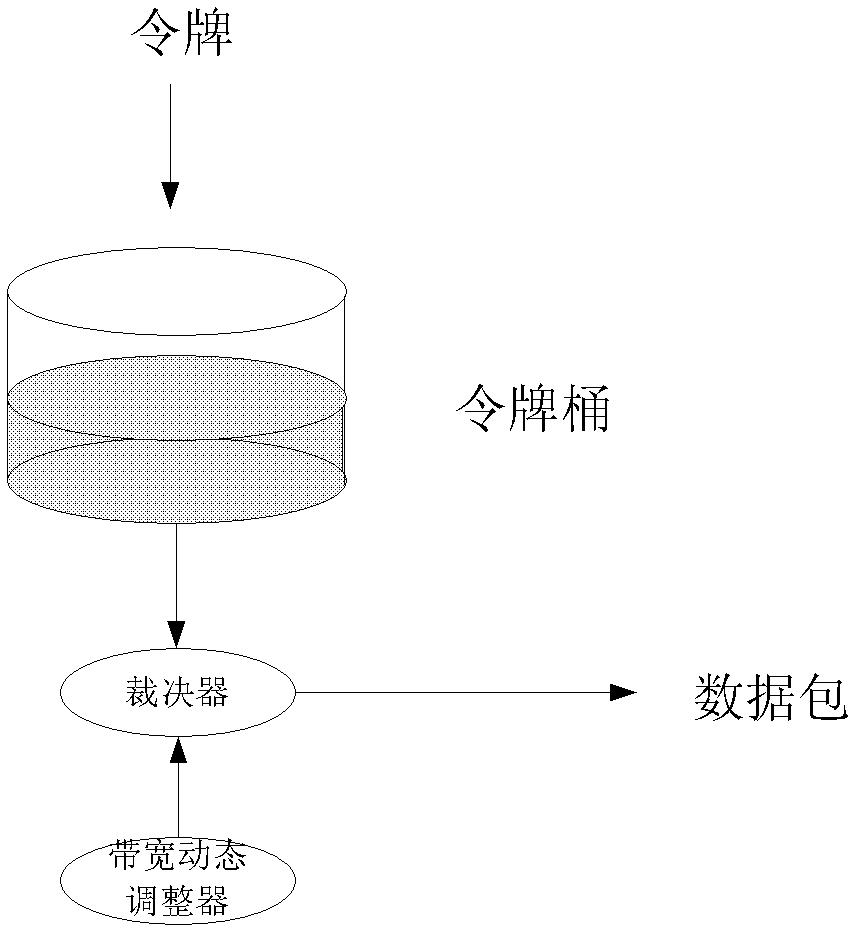

[0030] An RTL-level verification method for an Ethernet switch chip queue manager disclosed by the present invention is used to test and control the quantity, type, sequence and bandwidth of input streams in Ethernet. Before testing, a chip-based RTL verification method must first be built. Level simulation verification environment, and then set up the stimulus for testing and the model for test detection in the simulation verification environment. The simulation verification environment in this embodiment is built with the hardware language verilog.

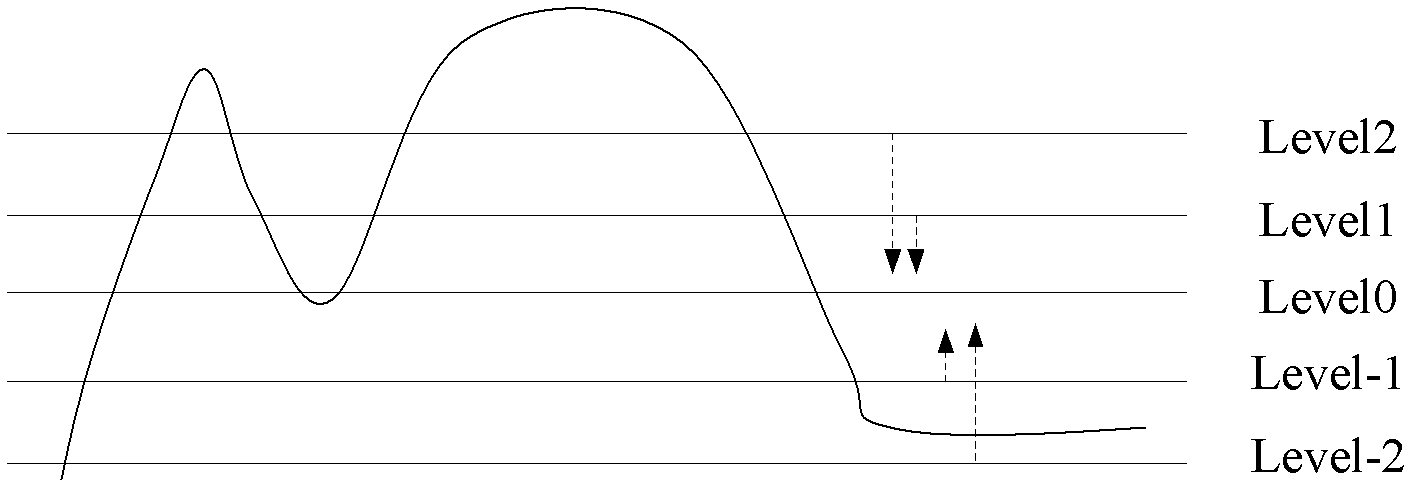

[0031] Test stimuli can generate different types of data flows, each flow contains data packets with different priorities, test stimuli can freely control the number and sequence of data packets, and the bandwidth of each flow ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More