Permanent-fault-tolerant routing control method facing networks on chip

A technology of permanent fault and control method, applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve the problems of reducing communication reliability and stability, affecting NoC performance, etc., to reduce the average transmission delay, improve performance, The effect of reducing peak power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below in conjunction with the accompanying drawings.

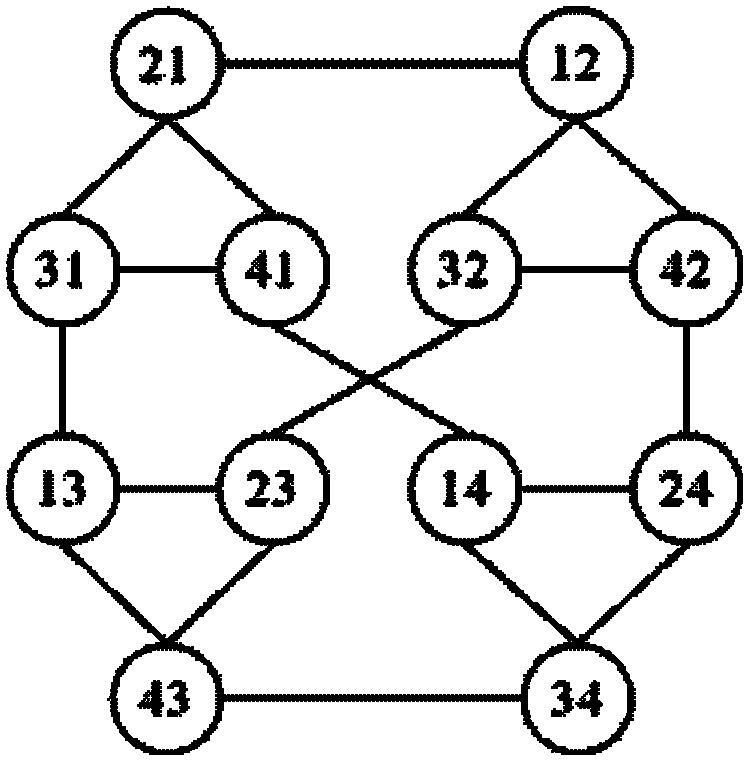

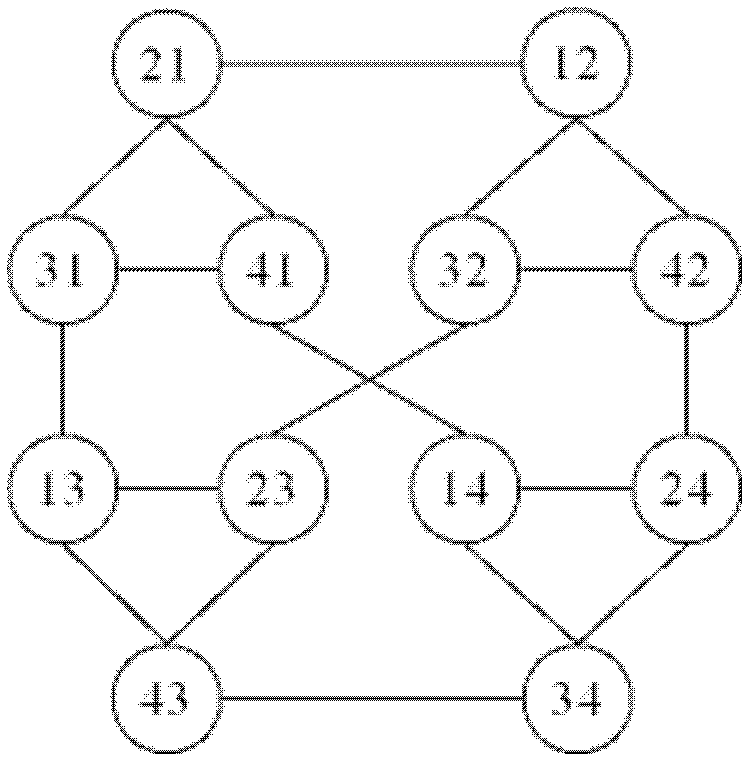

[0024] refer to figure 1 , a permanent fault-tolerant routing control method oriented to a network on chip, the routing control method comprising the following steps:

[0025] 1) Determine the data transmission volume of a communication, and then use the neighbor replacement element priority rule to select the first hop flood route;

[0026] 2) The route selection after the first one utilizes (n, k)-star graph nodes to arrange the priority rules of elements outside the ring to select deterministic routes.

[0027] The priority rules for neighbor replacement elements are as follows: First, the definition of the node element position is given. The internal element position of the node is the arrangement position of the element in the node. There are two types of external elements. When the external element exists in the destination node, its position is defin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More