Digital signal processor (DSP) hardware implementation method of Luby transform (LT) encoding and decoding algorithm

A hardware implementation, encoding and decoding technology, applied in the field of DSP hardware implementation of LT encoding and decoding algorithms, can solve problems such as limited processing capacity and memory space, and achieve the effect of improving random selection, reducing memory space, and improving decoding efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

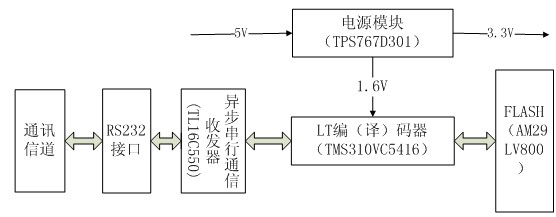

[0022] A DSP hardware implementation method of an LT encoding and decoding algorithm of the present invention will be described below in conjunction with the accompanying drawings.

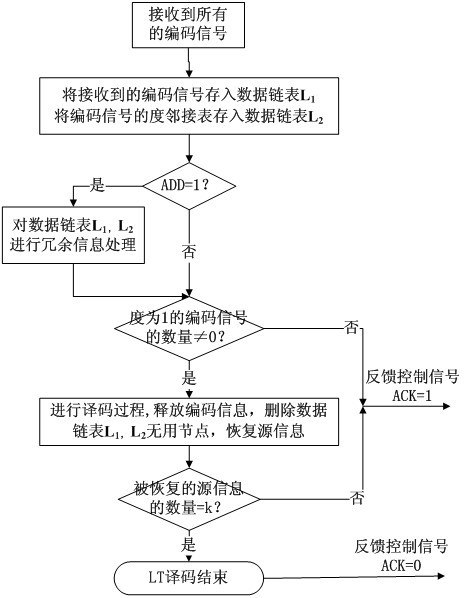

[0023] A DSP hardware implementation method of LT encoding and decoding algorithm, including asynchronous serial communication transceiver, TMS320VC5416 chip, FIASH chip, power regulator chip, LT encoder and decoder, using asynchronous serial communication transceiver to realize asynchronous data Transmission, use the power regulator chip to supply power to the TMS320VC5416 chip, use the FIASH chip to save the encoding and decoding program segment, and the LT decoder decodes after receiving the encoded signal from the asynchronous serial communication transceiver. During the decoding process, the LT decoder passes The communication channel sends feedback information to the LT encoder to control the work of the LT encoder.

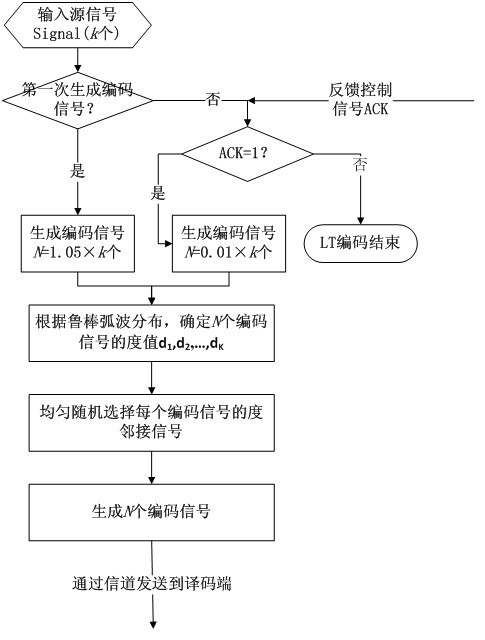

[0024] Such as figure 1 As shown, in the encoder, the source signal is t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More