Layout design used for preventing static electricity from damaging reliability sample

A technology of layout design and electrostatic destruction, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problem that the device samples are susceptible to electrostatic damage, etc., and achieve the effect of reducing the possibility of electrostatic damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

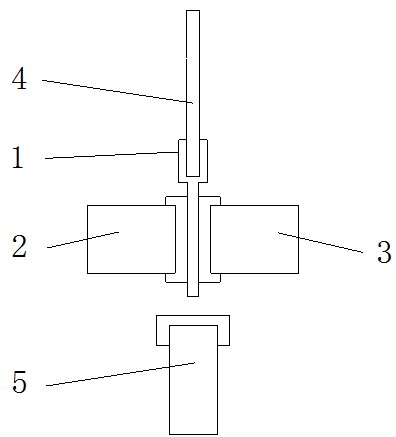

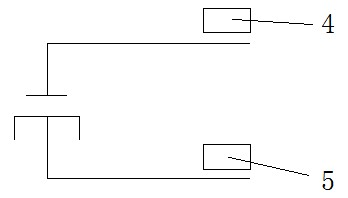

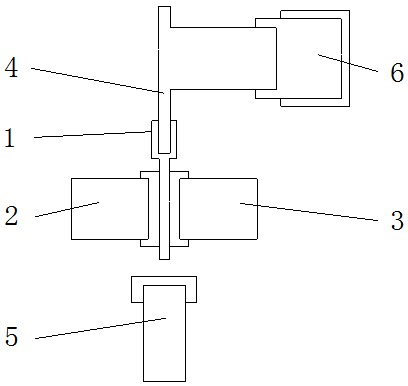

[0018] In the first embodiment of the present invention, please continue to refer to image 3 and Figure 4 shown. The above-mentioned device under test 1 includes a source 2 and a drain 3 , so that the gate capacitance 6 connected in parallel with the gate 4 will not affect the saturation current of the drain 3 of the device 1 .

[0019] In the second embodiment of the present invention, the device under test 1 is also connected in series with a base 5, so that the gate capacitance 6 connected in parallel with the gate 4 is applied to the voltage of each terminal of the device 1 gate 4, base 5, etc. without changing. .

[0020] To sum up, using the layout design of the present invention for preventing static electricity from damaging reliable samples greatly reduces the possibility of electrostatic damage to devices. At the same time, it will not affect the drain current, and normal testing can be performed.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com