Pixel unit, array substrate, liquid crystal panel, display device and manufacturing methods thereof

A technology for pixel units and array substrates, which is applied in semiconductor/solid-state device manufacturing, transistors, electrical components, etc., and can solve the problems of small aperture ratio and inability to meet high-quality display.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

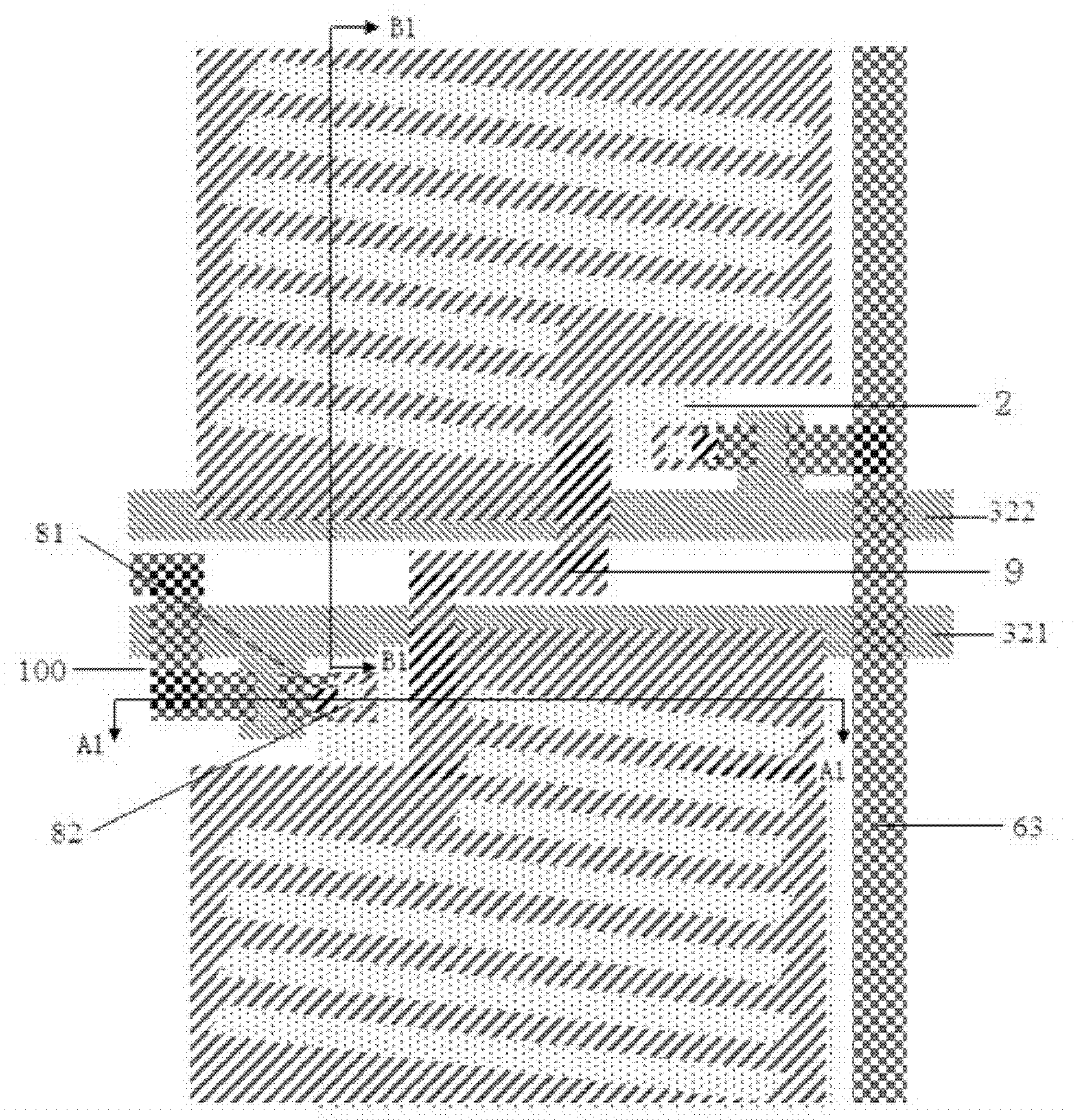

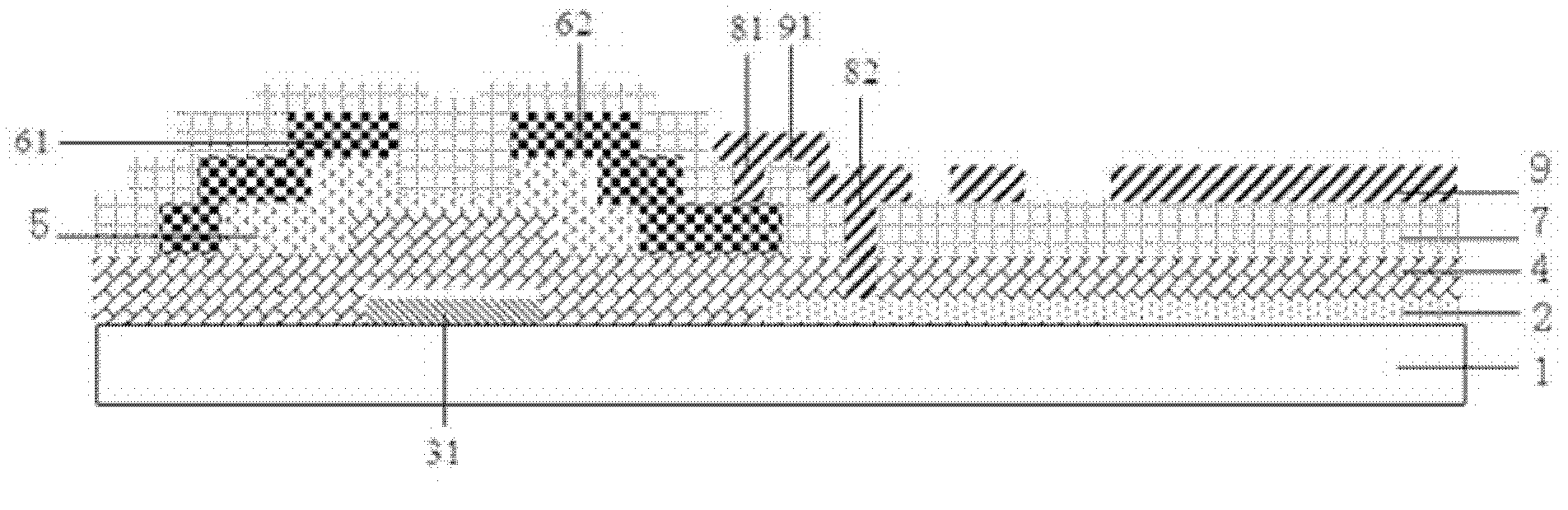

[0088] An embodiment of the present invention provides a pixel unit, the following refers to figure 1 with Figure 1A The structure of the pixel unit in this embodiment will be described. It should be clarified that the pixel unit defined in this embodiment does not include gate lines and data lines. The pixel unit can be used to form a common array substrate or a dual-gate array substrate after the gate lines and data lines are properly arranged.

[0089] figure 1 Shown is a schematic plan view of the pixel unit in the embodiment of the present invention, which selects two pixel units that are adjacent up and down; Figure 1A shown as figure 1 The cross-sectional view in the direction of A1-A1, Figure 1B for figure 1 Schematic diagram of B1-B1 cross-section in middle, that is Figure 1A with Figure 1BIt is a cross-sectional schematic diagram of different cutting directions of a pixel unit. The pixel unit in this embodiment includes a thin film transistor 100, a pix...

Embodiment 2

[0098] This embodiment provides an array substrate, including a substrate, on which a gate line is arranged, a data line is arranged perpendicular to the gate line, a pixel area is defined between the gate line and the data line, and the The pixel area includes the pixel unit described in the first embodiment above (see figure 1 ), wherein the gate of the thin film transistor is connected to the gate line, and the source of the thin film transistor is connected to the data line. It should be pointed out that the array substrate including the above-mentioned pixel units can be called an I-ADS array substrate; compared with the traditional ADS array substrate, the upper and lower positional relationship between the pixel electrode 2 and the common electrode 9 has changed.

[0099] As an array substrate in this embodiment, it may be the following array substrate: on the array substrate, gate lines are arranged above and below a plurality of pixel units in each row, and gate lines...

Embodiment 3

[0107] This embodiment provides a method for manufacturing an array substrate, such as Figure 9 shown, including the following steps:

[0108] S101, forming a pattern including a pixel electrode through a first patterning process, and forming a pattern including a gate line and a thin film transistor gate through a second patterning process;

[0109] Alternatively, the first patterning process is used to form the pattern including the gate line and the thin film transistor gate, and the second patterning process is used to form the pattern including the pixel electrode.

[0110] S102, forming a pattern including a gate insulating layer, an active layer, a data line, and a source electrode and a drain electrode of a thin film transistor through a third patterning process.

[0111] S103, forming a pattern including a passivation layer through a fourth patterning process.

[0112] S104, forming a pattern including a common electrode through a fifth patterning process.

[0113...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More