Method and system for cylindrical surface calculation based on modeling simulation verification language (MSVL) of arithmetic expression

A calculation method and expression technology, applied in the direction of inter-program communication, multi-program device, etc., can solve the problems of narrow application scope, weak description ability and expression ability, etc., and achieve the effect of strong description ability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

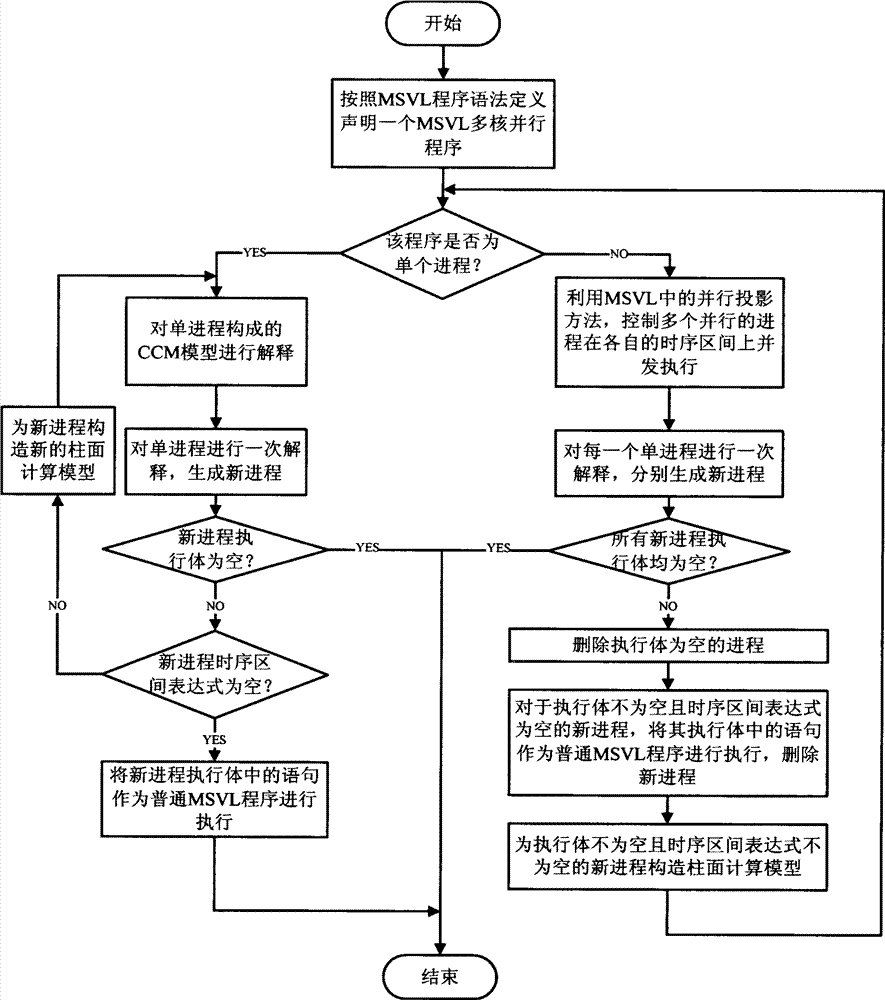

[0062] The invention is an MSVL cylinder calculation method based on an arithmetic expression, which belongs to the technical field of system formal modeling and verification, and performs simulation, modeling and verification of MSVL program process modules. The invention defines multi-core parallel program syntax, based on the The multi-core parallel program syntax and MSVL statements declare a multi-core parallel program. In this multi-core parallel program, different processes execute on their own timing intervals. The execution is controlled by the timing interval expression of the process. The timing interval of the process and the main The time intervals are parallel, and the time series intervals of each process form a cylindrical model around the main time interval in parallel; see figure 1 , the MSVL cylinder calculation process based on arithmetic expressions includes:

[0063] Step 1. Define the multi-core parallel program grammar. A multi-core parallel program may...

Embodiment 2

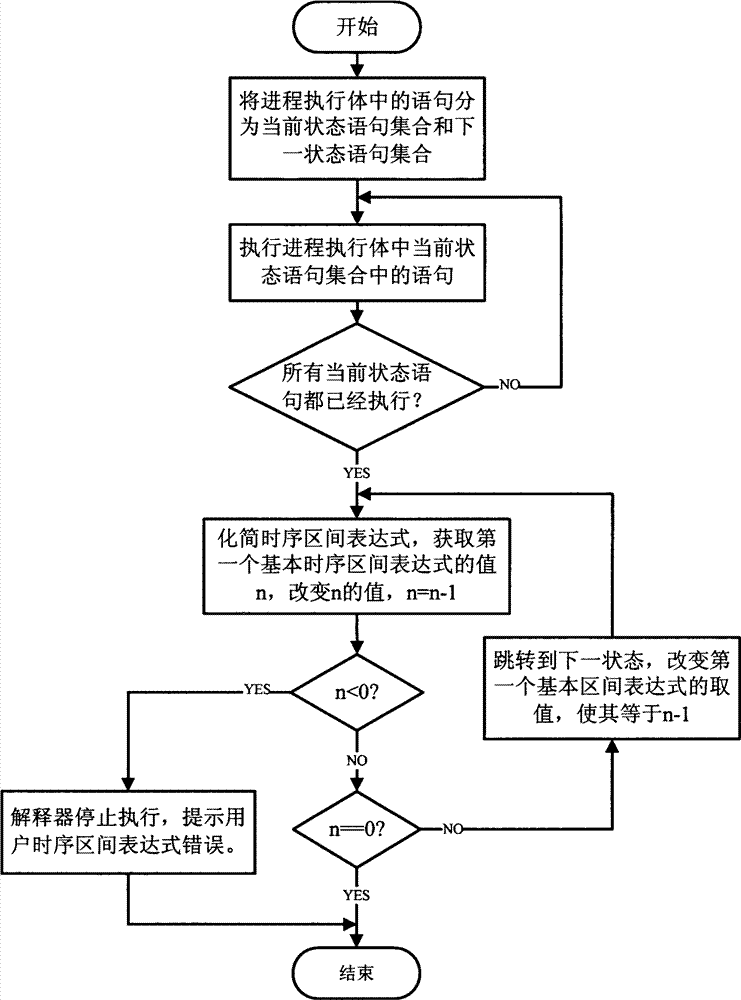

[0109] The calculation method of the MSVL cylinder based on the arithmetic expression is the same as that in Embodiment 1. Step 6 is to explain the process of the simple structure once, so that the execution body of the process of the simple structure is executed in its own time sequence interval state. Refer to image 3 , an interpretation process of a single-structure process includes: firstly, interpreting the process execution body, then interpreting the time series interval expression, and then controlling the duration of the time interval granularity of the interpretation effect of the process by the interpretation result of the time series interval expression.

[0110] First, explain the execution body of the process. For each process, the execution state of each statement in the process executive body is controlled by the time series interval expression of the process. The definition and execution of the program in each process executive body is compatible with the exi...

Embodiment 3

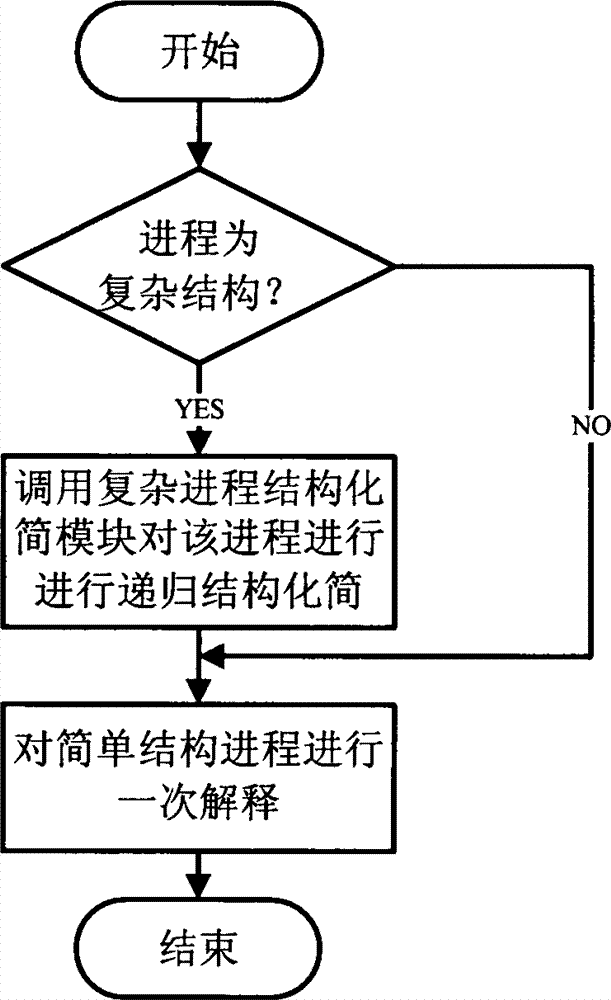

[0127] The MSVL cylinder calculation method based on arithmetic expression is the same as embodiment 1-2, see figure 2 , the complex structure process of the present invention refers to the process that contains OR operation and closure operation in the time series interval expression, or contains the OR operator (or) in the process execution body, and the structural conversion of the complex structure means that the process is first performed Recursive equivalent transformation, transforming it into a CCM model composed of simple structural processes; the equivalent transformation is carried out according to the following rules:

[0128] L1.φov(l 1 +l 2 )≡(φovl 1 )or(φovl 2 )

[0129]

[0130] L3.(φ 1 orφ 2 )ov(l)≡(φ 1 ovl)or(φ 2 ovl)

[0131] Wherein or is an existing operator in MSVL, and the simplification method of this operator is to select one of two independent processes connected by or to perform simplification. The above-mentioned complex structure proc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More