Indirect branch instruction processing method and device

A branch instruction and processing method technology, which is applied in electrical digital data processing, program control design, instruments, etc., can solve the problems of excessive context switching and low translation efficiency, and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

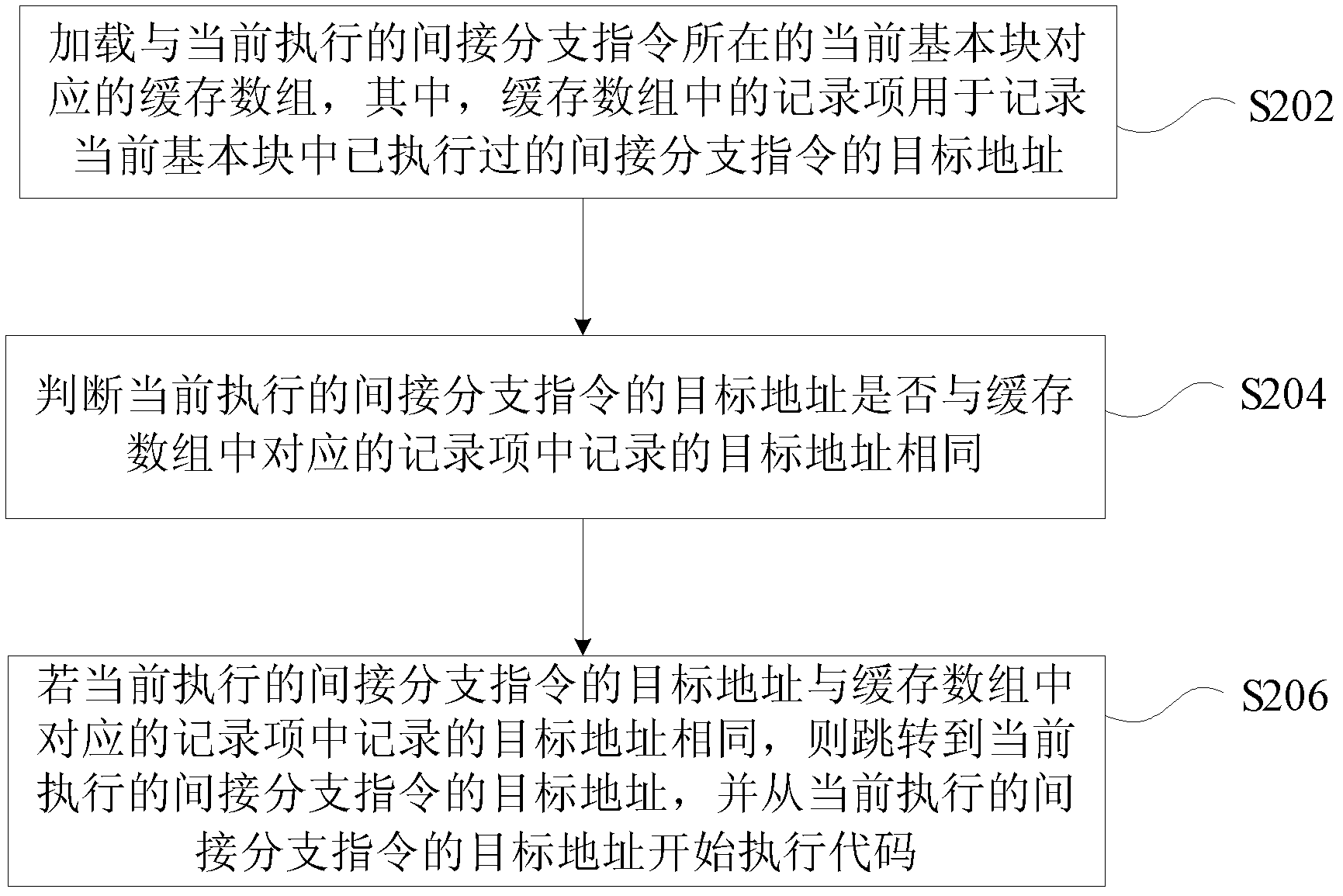

[0034] This embodiment provides a method for processing indirect branch instructions, such as figure 2 As shown, the method includes:

[0035] S202, load the cache array corresponding to the current basic block where the currently executed indirect branch instruction is located, wherein the record item in the cache array is used to record the target address of the executed indirect branch instruction in the current basic block; preferably, every A basic block corresponds to a cache array, and the entries in the cache array record the target addresses of the executed indirect branch instructions in the current basic block. Preferably, the process of recording the target address of the indirect branch instruction can be realized by recording the pointer of the structure corresponding to the basic block where the target address of the indirect branch instruction is located, wherein the above structure is used to store the corresponding basic block, but the present invention Not...

Embodiment 2

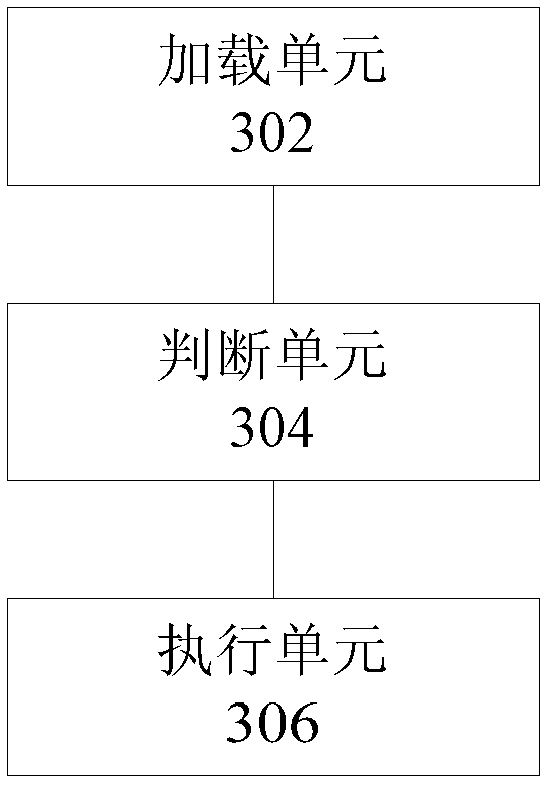

[0047] On the basis of the above-mentioned embodiment 1, this embodiment also provides an indirect branch instruction processing device, specifically, as image 3 As shown, the device includes: a loading unit 302, configured to load a cache array corresponding to the current basic block where the currently executed indirect branch instruction is located, wherein the record items in the cache array are used to record the executed in the current basic block. The target address of the indirect branch instruction; preferably, each basic block corresponds to a cache array, and the records in the cache array record the target address of the indirect branch instruction that has been executed in the current basic block. Preferably, the indirect branch instruction can be recorded by recording the The process of recording the target address of the indirect branch instruction is realized by the pointer of the structure body corresponding to the basic block where the target address of the ...

Embodiment 3

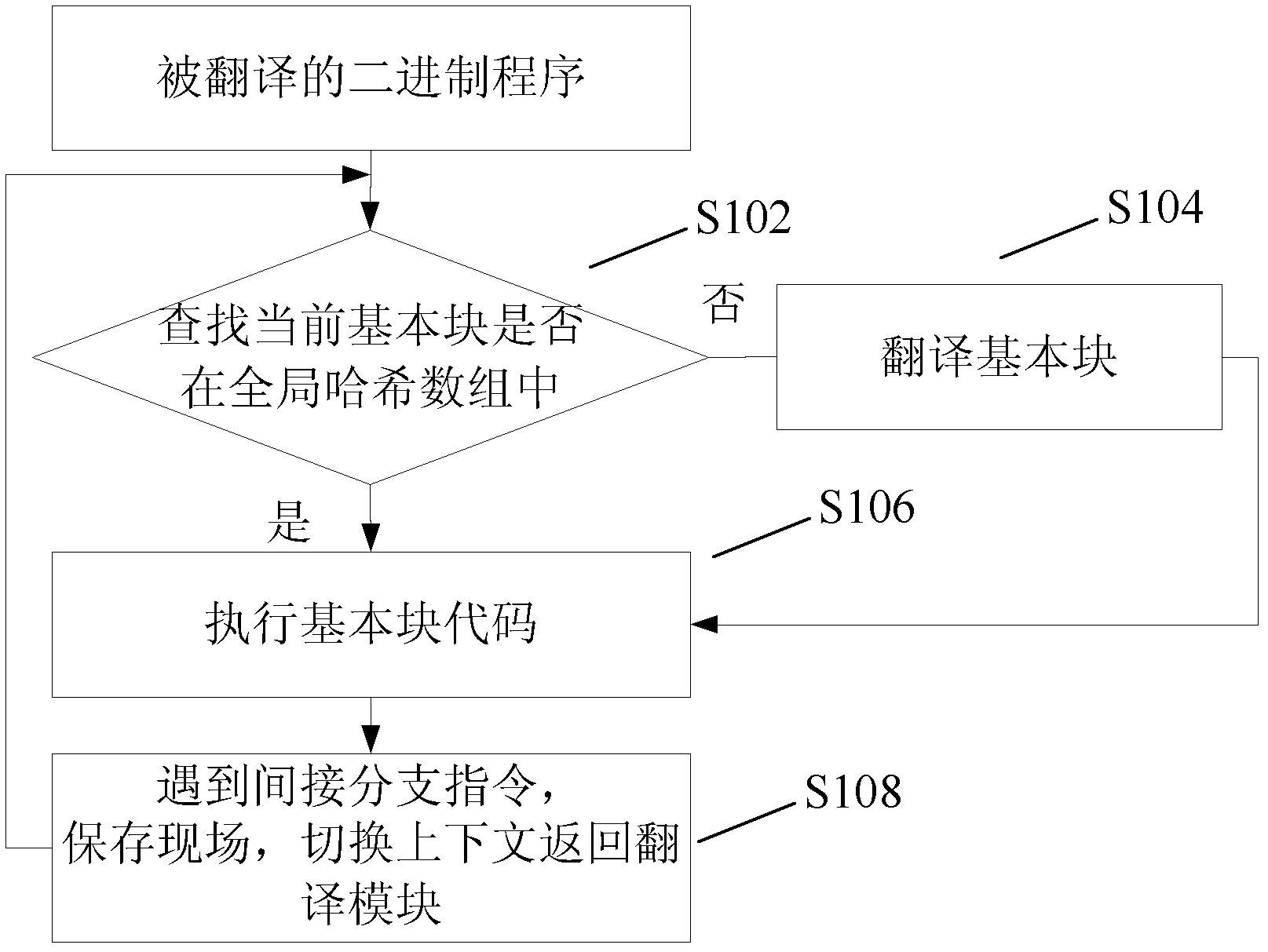

[0058] On the basis of the above-mentioned embodiment 1 and embodiment 2, the present invention also provides a specific indirect branch instruction processing scheme applied to binary translation, which comprises:

[0059] Step 1, add a cache array for each basic block, and this cache array is used to cache the target address of the indirect branch instruction. Preferably, the process of recording the target address of the indirect branch instruction can be realized by recording the pointer of the structure corresponding to the basic block where the target address of the indirect branch instruction is located, wherein the above structure is used to store the corresponding basic block, but the present invention Not limited to this, other alternative ways can also be used to record the target address of the indirect branch instruction.

[0060] Step 2, when the indirect branch instruction is executed for the first time, because the cache array of the basic block where the indir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More