Wiring method of memory device

A wiring method and equipment technology, applied in the computer field, can solve problems such as small motherboard area, short distance between memory controller and memory device, and increased production cost of printed circuit board (PCB), so as to reduce the number of stacked layers and improve design Efficiency and production cost savings

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

[0039] see figure 1 , the embodiment of the present invention includes:

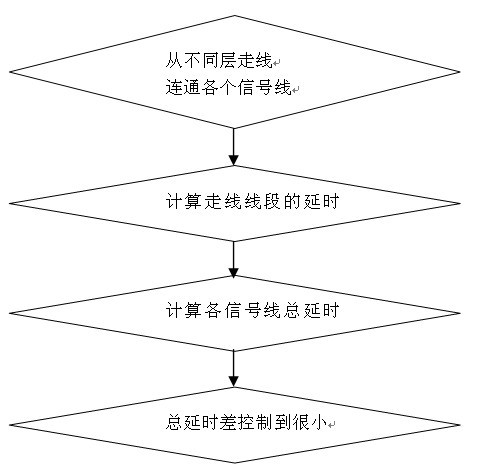

[0040] A wiring method of a memory device of the present invention, the specific steps include:

[0041] (1) Connect each signal line of the same data group between the memory controller and the memory device, and the wiring can be routed from multiple wiring layers of the printed circuit board (PCB) at the same time.

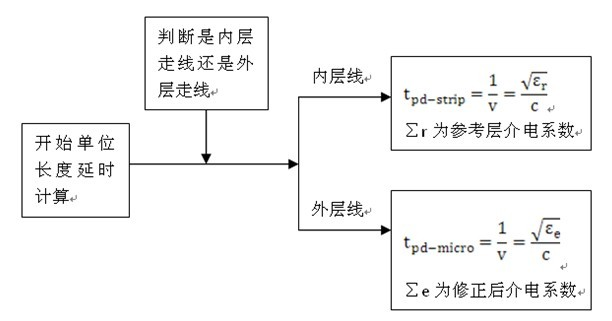

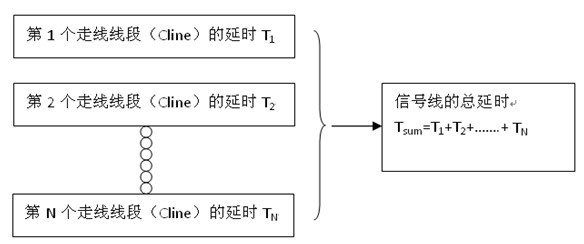

[0042] (2) According to the delay T of the line segment (Cline) per unit length D The calculation method calculates the delay of all the line segments (Cline) of each signal line respectively. Delay (T i ) is equal to the delay (T D ) times the length (...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More