Output stage quick response circuit and response method thereof

A fast-response, output-stage technology, applied in logic circuits, electrical components, pulse technology, etc., can solve the problems that the rising edge time of the output stage output signal cannot be reduced, and the turn-off time of the output transistor has no help, etc., to achieve high-efficiency rise Effect of edge and falling edge time course, reduced rising edge time, accelerated state transition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

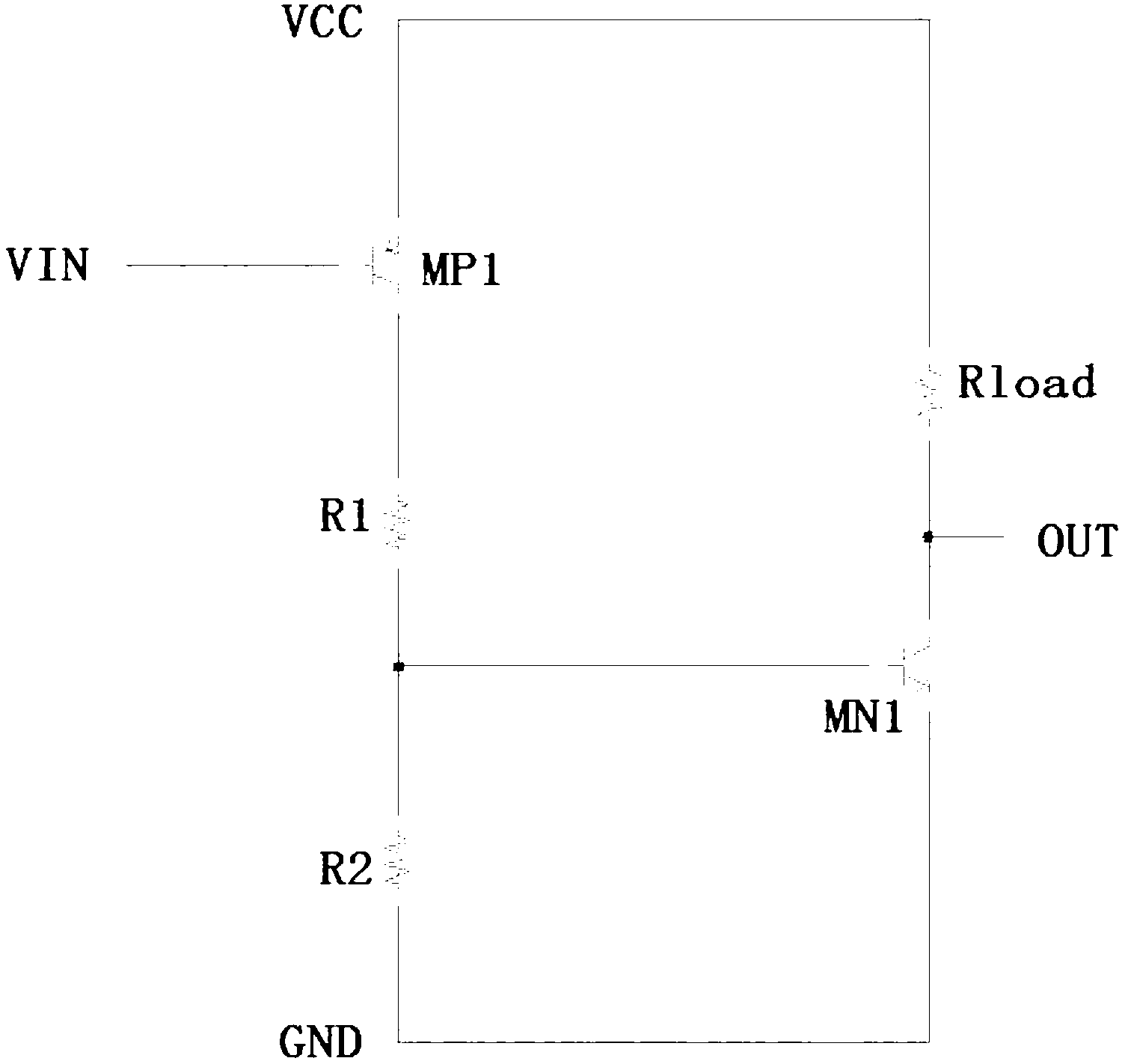

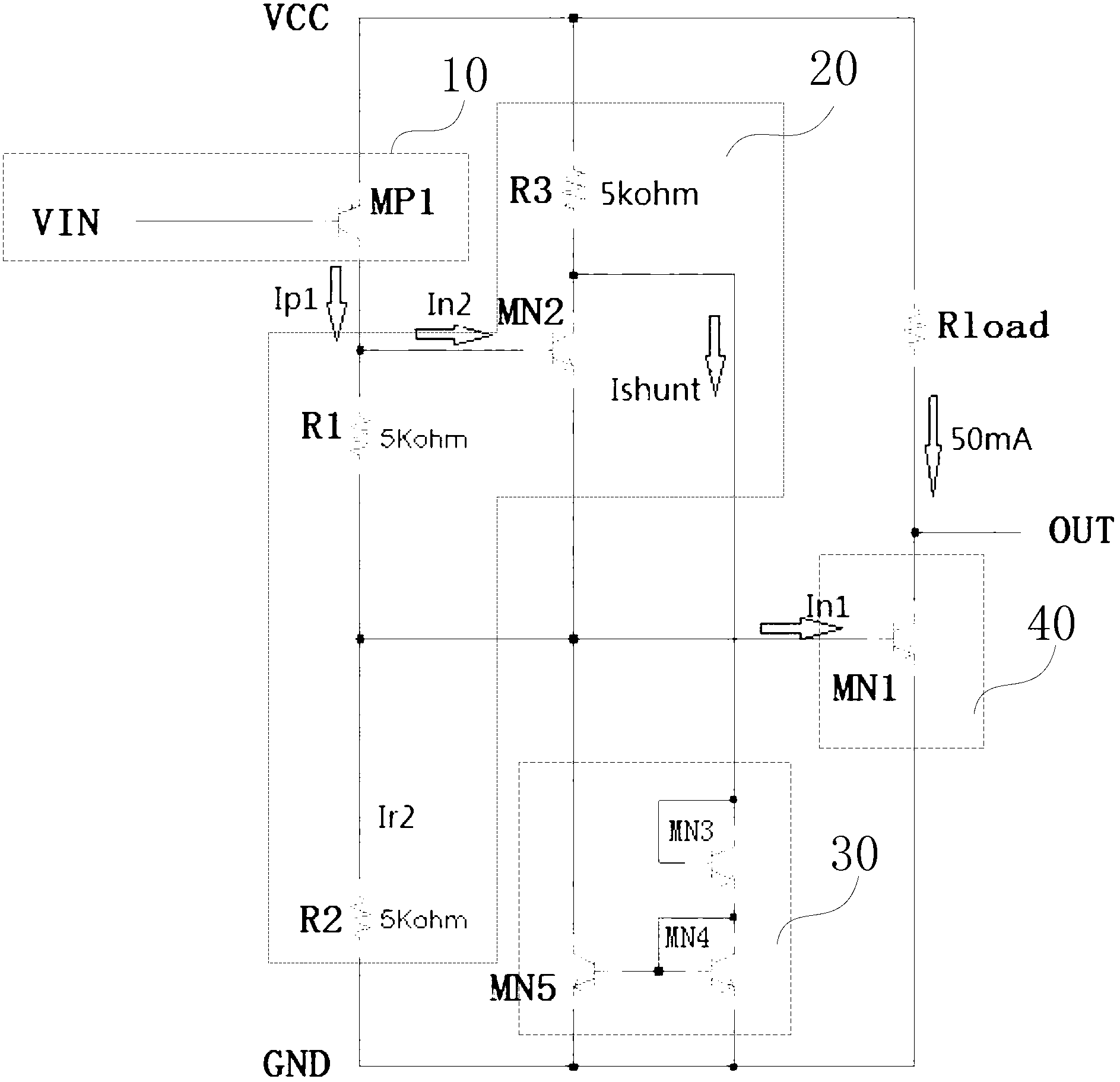

[0042] see image 3 , The present invention discloses a fast response circuit of an output stage, said circuit comprising: an input stage 10 , a driver stage 20 , an acceleration stage 30 , and an output stage 40 . This embodiment includes several transistors, and the transistors can be triodes based on bipolar technology, or MOS transistors based on CMOS technology; this embodiment uses the transistor as an example to introduce the fast response circuit of the present invention.

[0043] The input stage 10 is used for receiving an input signal VIN. In this embodiment, the input stage 10 includes a first triode MP1; the base of the triode MP1 is connected to the input signal terminal VIN, the collector is connected to the driving stage 20, and the emitter is connected to the power supply voltage VCC.

[0044] The output stage 40 includes a second transistor MN1 for outputting an output signal OUT. The base of the second transistor MN1 of the output stage is connected to the ...

Embodiment 2

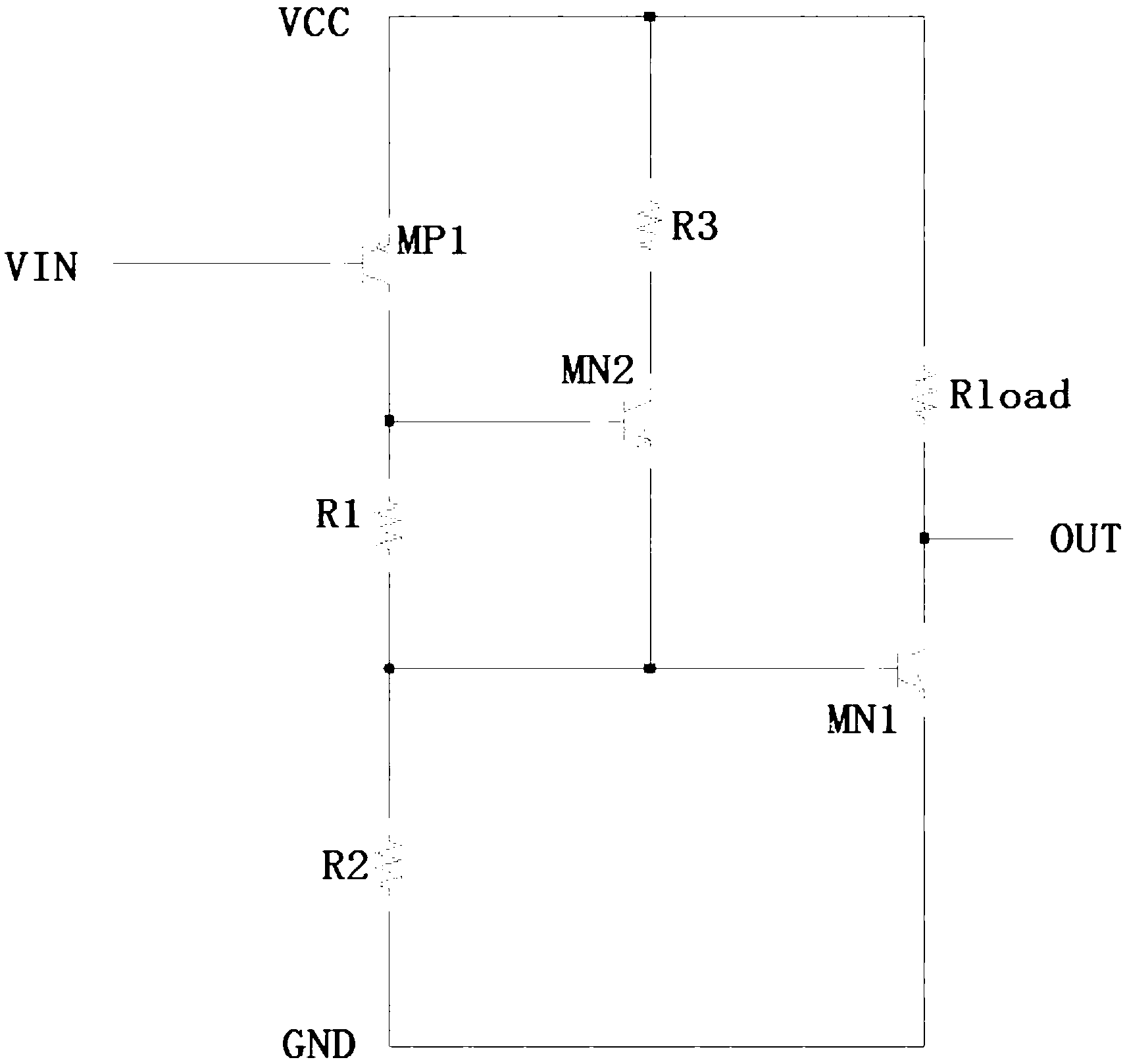

[0060] see Figure 4 The difference between this embodiment and Embodiment 1 is that in this embodiment, the fast response circuit of the present invention uses a MOS transistor based on CMOS technology (replacing the triode in Embodiment 1) to realize the technical solution of the present invention.

[0061] The input stage is used for receiving the input signal VIN. The input stage includes a first MOS transistor MP1; the gate of the MOS transistor MP1 is connected to the input signal terminal VIN, the drain is connected to the driving stage, and the source is connected to the power supply voltage VCC.

[0062] The output stage includes a second MOS transistor MN1 for outputting an output signal OUT. The gate of the second MOS transistor MN1 of the output stage is connected to the second end of the first resistor R1, the drain of the second MOS transistor MN1 is connected to the signal output end, the second end of the fourth resistor Rload, and the second end of the fourth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More