Method for automatically starting central processing unit (CPU) system by utilizing double flashes

An automatic and code-starting technology, applied in the direction of program loading/starting, generation of response errors, error detection of redundant data in operation, etc., can solve problems such as boot failure, system startup failure, startup failure, etc., to achieve reliable High performance, simple operation and strong controllability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific examples.

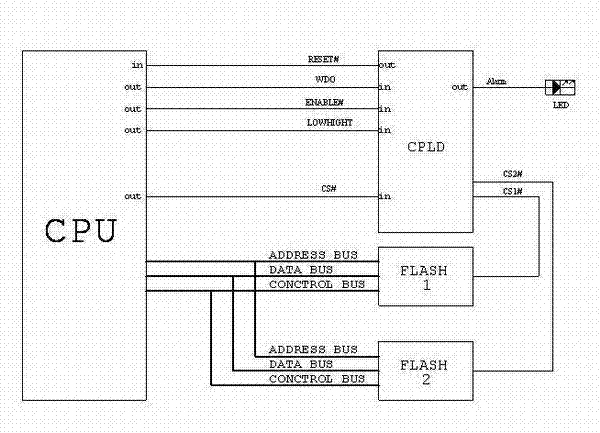

[0014] A method for automatically starting a CPU system with dual FLASH. Before leaving the factory, the two FLASHs are programmed with a startup program bootrom and a complete application program of the entire system.

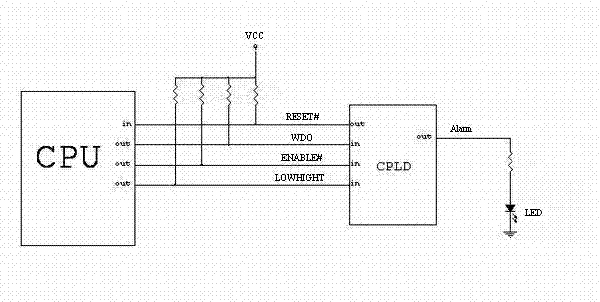

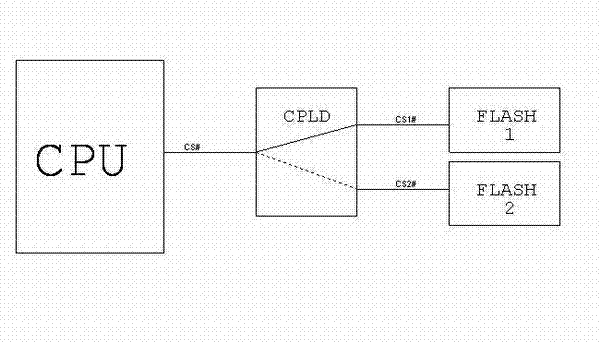

[0015] Such as figure 2 Shown, the control handshake schematic diagram between CPU and CPLD that the present invention adopts, RESET# among the figure resets the reset signal of whole CPU system for CPLD; A pulse wave with a period of 1S. ENABLE# is for authorized users who need to upgrade FLASH and control the CPU by command to pull down the signal to enable the upgrade function, and then CPLD determines to switch the CPU chip selection CS# to CS1# or CS2# by reading the LOW / HIGHT signal; image 3 shown in image 3 The middle CPLD is equivalent to a toggle switch. If the CPU sets LOW / HIGHT to high level (default), t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More