Method for manufacturing semiconductor device

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of increased wiring resistance and increased wiring delay, and achieve the effect of easy connection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] (Summary of the manufacturing method of the embodiment)

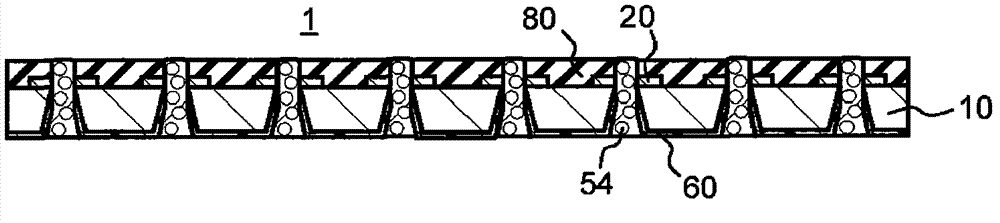

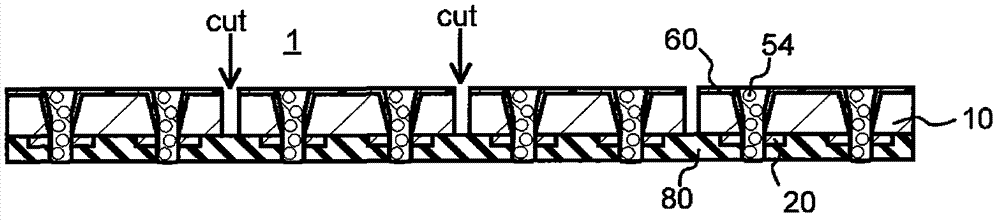

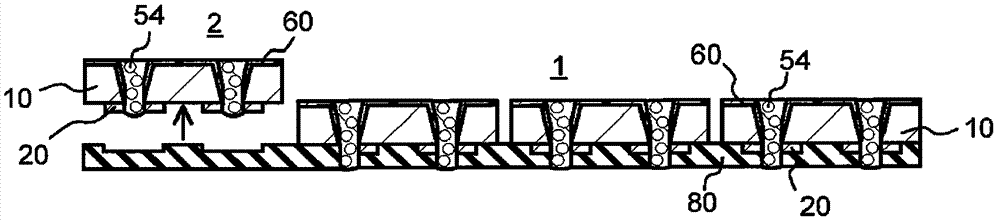

[0057] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. Figure 1A ~ Figure 1H is a sectional view showing a cross section of a semiconductor device in each step of the manufacturing method of the embodiment, figure 2 It is a flowchart showing each of these steps. In the manufacturing method of the embodiment, there are steps of forming via holes, cutting out chips, picking up chips, stacking chips, and firing chips.

[0058][Formation of via holes]

[0059] First, a wafer 1 is prepared, which is formed by forming a via hole on the device wafer 10 and filling the via hole with a porous metal material 54 (step 100. Hereinafter referred to as "S100") .).

[0060] Such as Figure 1A As shown, electrode pads 20 for constituting circuits are formed on one main surface of the device wafer 10 , and recesses (or through holes) corresponding to the position...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More