Reconfigurable 2D (two-dimensional) mesh on-chip network structure and reconfiguration method thereof

An on-chip network structure and reconfiguration technology, applied in data exchange networks, digital transmission systems, electrical components, etc., can solve problems such as topology differences, and achieve moderate hardware overhead and low power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

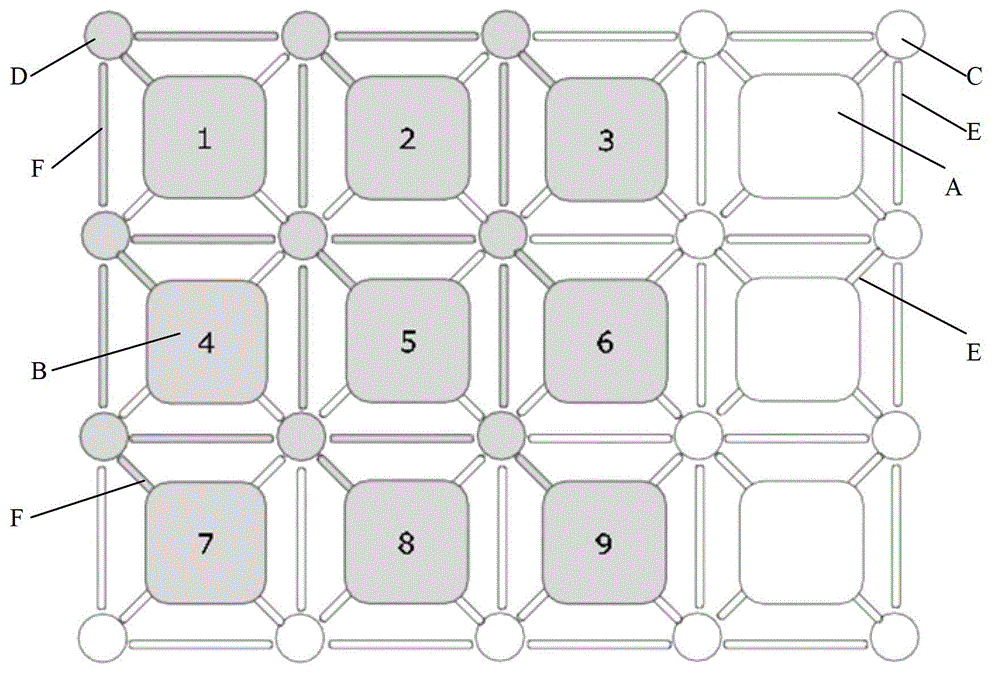

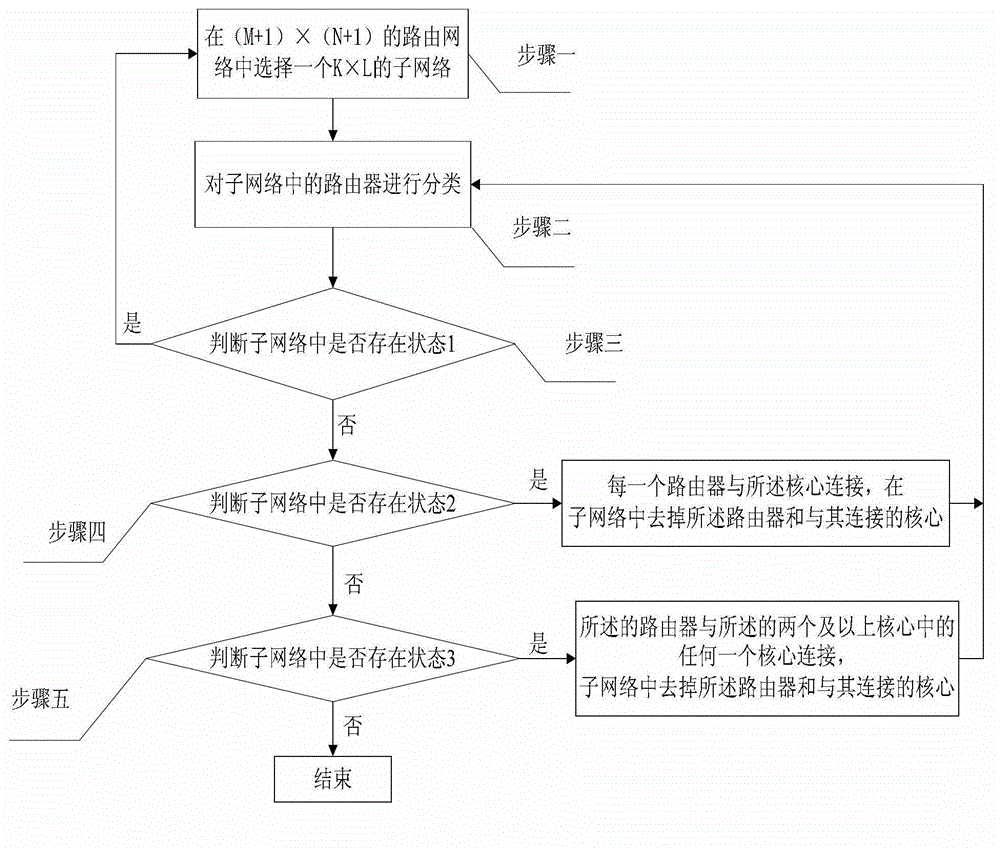

[0024] Specific implementation mode one: combine figure 1 Describe this embodiment, the reconfigurable 2D mesh network-on-chip structure described in this embodiment, the reconfigurable 2D mesh network-on-chip structure, which includes M×N cores and (M+1)×(N+1) routers, M×N cores include K×L working cores, and redundant cores (M×N-K×L);

[0025] Each core can be connected to one of the four adjacent routers: each router communicates with the four adjacent cores through the multiplexer MUX and the network interface NI.

specific Embodiment approach 2

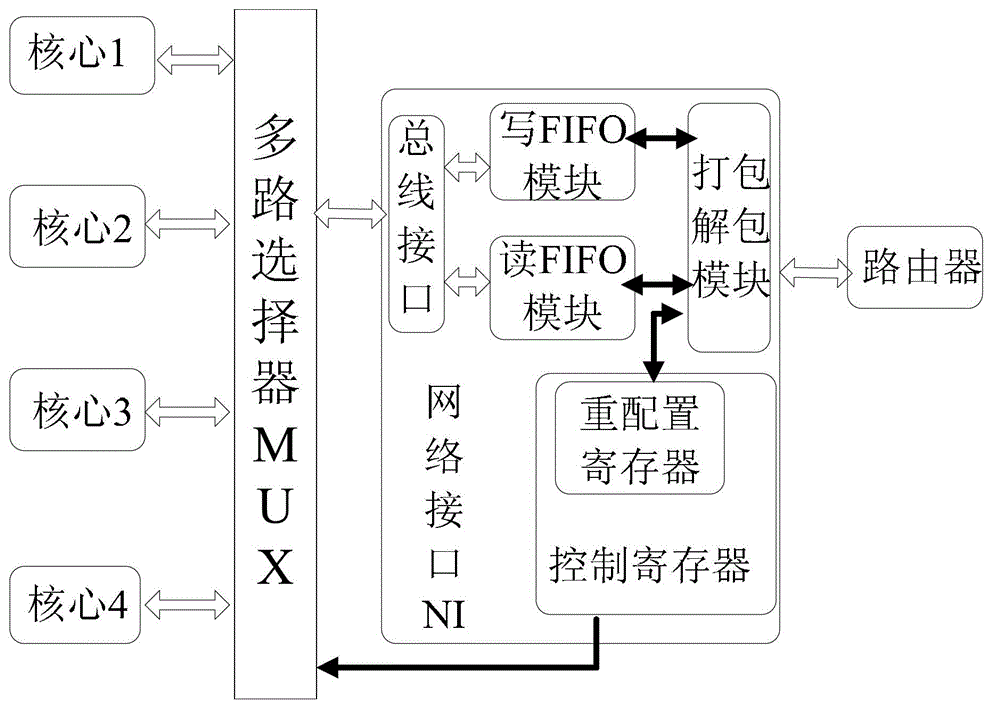

[0026] Specific implementation mode two: combination figure 2 This embodiment is described. This embodiment is a further limitation of the reconfigurable 2D mesh network-on-chip structure described in Embodiment 1. The network interface NI includes a bus interface, a write FIFO module, a read FIFO module, unpacking and packaging The module and the control register are characterized in that the control register also includes a reconfiguration register, and the reconfiguration register includes a reconfiguration status register REC_STA, a reconfiguration control register REC_CNTL and a virtual node number register NODE_NUM,

[0027] The unpacking and packaging module is used for unpacking or packaging normal messages in the network, and is also used for packaging or unpacking reconfiguration messages, and writes the reconfiguration messages after packaging or unpacking into the reconfiguration status register REC_STA;

[0028] The reconfiguration status register REC_STA is used...

specific Embodiment approach 3

[0032] Embodiment 3: This embodiment is a further limitation of the reconfigurable 2D mesh network-on-chip structure described in Embodiment 1.

[0033] The header flake format of the network interface NI is:

[0034]

[0035]

[0036] In this embodiment, the format of the traditional network interface header chip is modified, and bits 31-29 of the service type are modified. On the basis of the original BE service and GS service, the reconfiguration service type (RC) is added.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com