Systems and methods providing arrangements of vias

A chip and semiconductor technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of torque increase, affecting the mutual contact and alignment of ball grid arrays, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

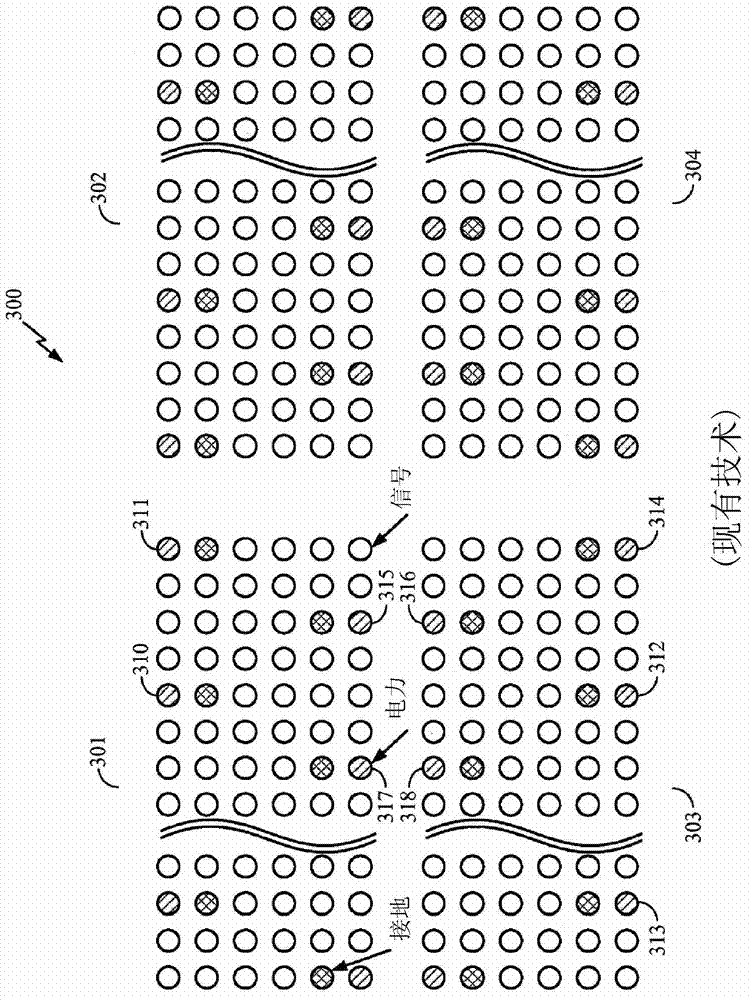

[0023] Figure 4 is an illustration of an exemplary system 400 adapted according to one embodiment. The system 400 includes a logic chip 402 and a memory chip 401 . The memory chip 401 includes contacts 422 , 423 and the logic chip 402 includes contacts 412 , 413 . For your convenience, Figure 4 Only four contacts 412, 413, 422, 423 are shown, but it is understood that various embodiments may include many more contacts arranged in an array. exist Figure 4 , the contacts are arranged in an array, the contacts being aligned to provide electrical contact between the logic chip 402 and the memory chip 401 . Specifically, the contacts 422 and 423 communicate with the redistribution layer 415 to access various memory cells (not shown) in the memory chip 401 . Likewise, contacts 412 and 413 communicate with logic circuits (not shown) and metal layer 418 via through-silicon vias (TSVs) 416 , 417 . Although in Figure 4 The RDL is not shown on the logic chip 402 in the embodim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More