Synchronous clock extraction method for receiving end in fully digital spread spectrum communication system

A technology of spread spectrum communication and synchronous clock, which is applied in the field of full digital spread spectrum, can solve the problems such as the clock cannot be synchronized, and achieve the effect of eliminating clock signal glitches

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

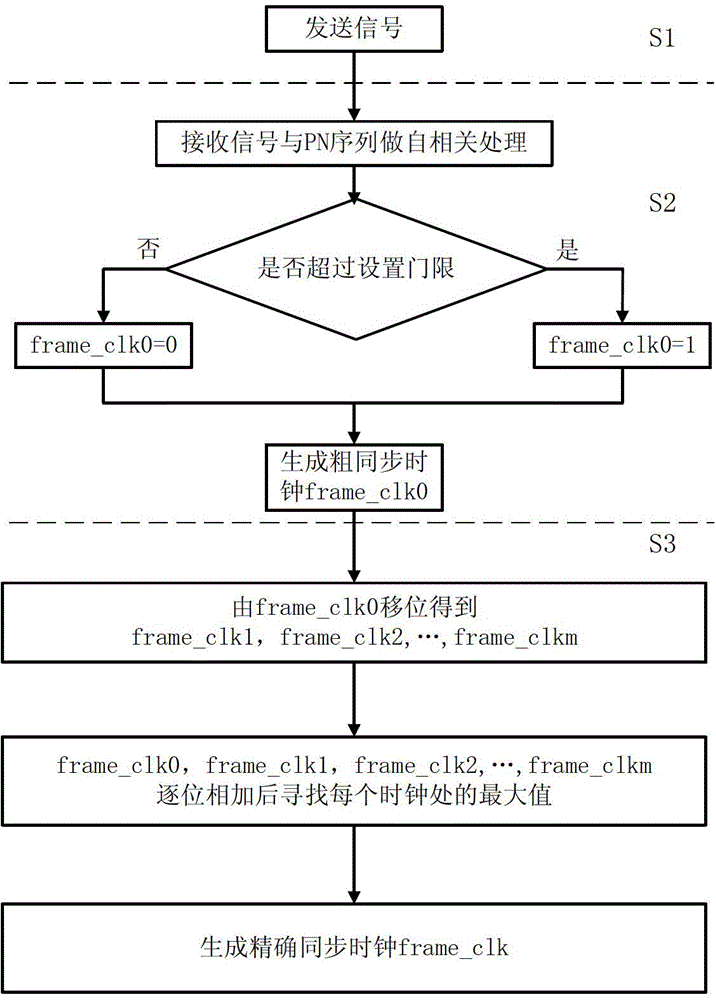

[0020] Such as figure 1 As shown, the present invention provides a synchronous clock extraction method at the receiving end in an all-digital spread spectrum communication system, comprising the following steps:

[0021] S1, the sending end transmits the original data after 15 times of spread spectrum; the implementation method of the spread spectrum is: the sender encodes each bit in the original data through FPGA, and becomes the PN code whose sequence length is N Or the inverse code of the PN code whose sequence length is N, the PN code or the inverse code of the PN code represent the "0" bit and the "1" bit in the original data, and N can flexibly change the spreading...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More