Encoder device and method for short code length multi-system weighted repeat-accumulate code

A repeating accumulation code, multi-system technology, applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc. High coding complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

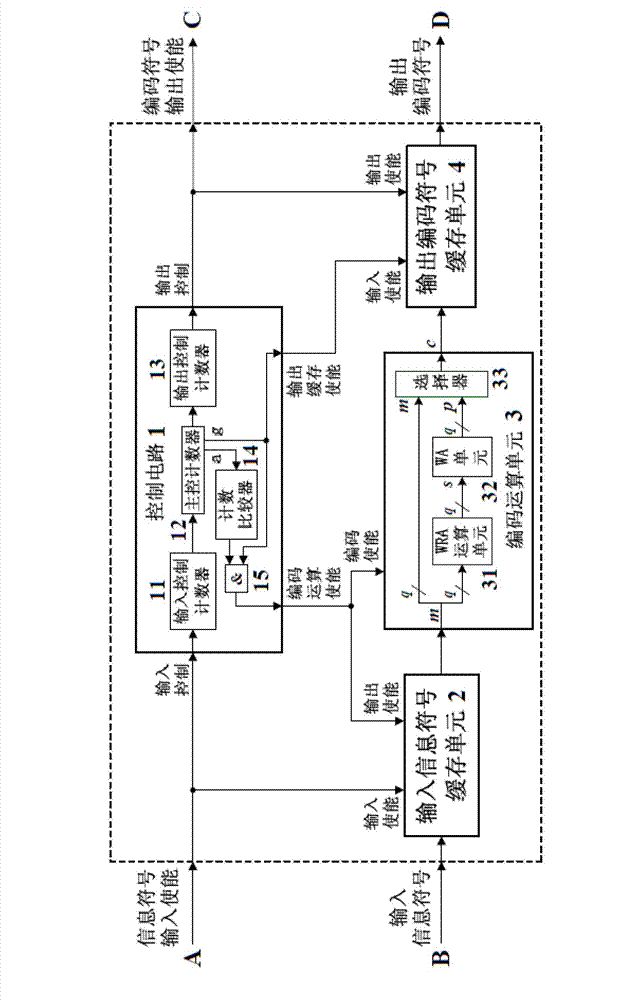

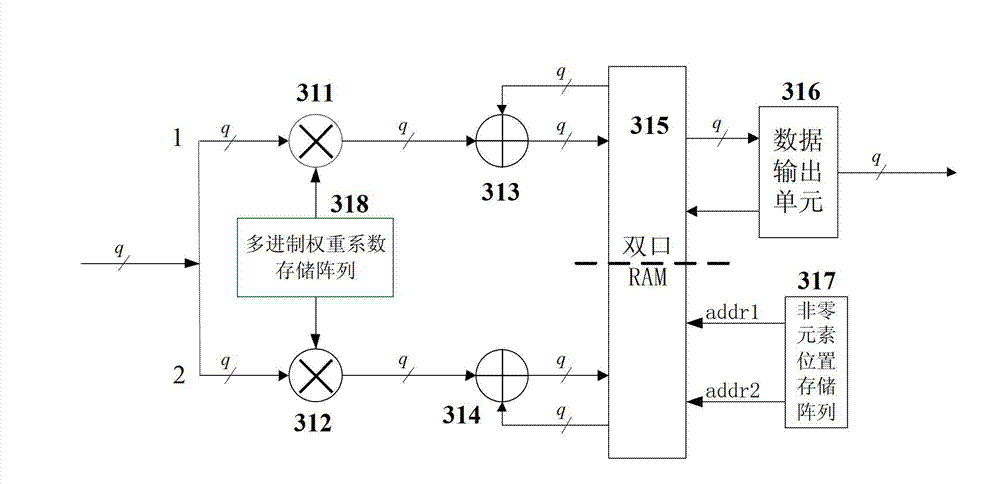

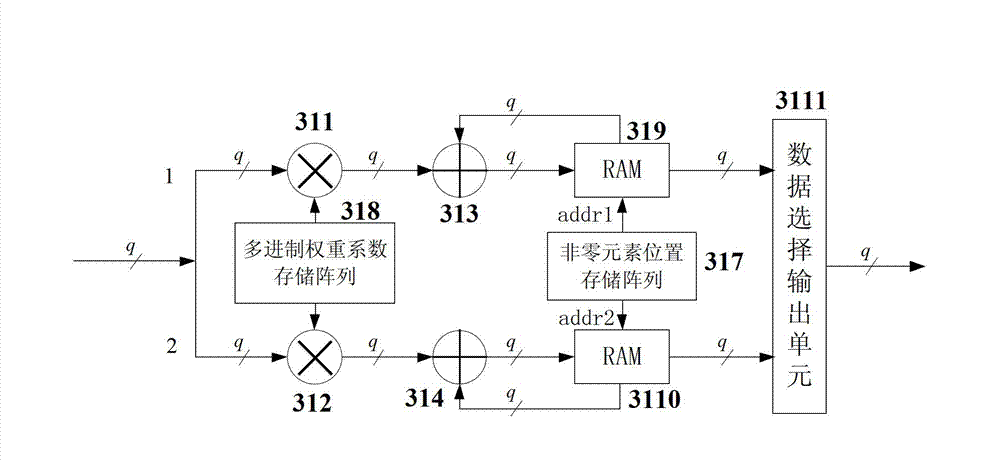

[0095] The encoder device proposed by the present invention can be realized by using Field Programmable Gate Array (Field Programmable Gate Array, FPGA). Instructions attached figure 2 The dual-port random access memory (Random Access Memory, RAM) module and attached image 3 The RAM module in can adopt the RAM module integrated in FPGA chip to realize. attached figure 2 And attached image 3 The multi-ary weight coefficient storage array and non-zero element position storage array in Figure 4 The storage array of non-zero element positions inside the gating network, and the attached Figure 5 And attached Figure 6 The multiplier coefficient memory in the FPGA chip can be implemented by a read-only memory (Read-Only Memory, ROM) module integrated in the FPGA chip.

[0096] If an independent RAM module and ROM module are used to realize the encoder device proposed in this patent, the attached figure 2 The dual-port RAM module can be realized by the dual-port RAM chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More