Patents

Literature

57results about How to "Reduce encoding delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for encoding and decoding an audio signal using adaptively switched temporal resolution in the spectral domain

ActiveUS20090012797A1Quality improvementReduce encoding delaySpeech synthesisTemporal resolutionFrequency spectrum

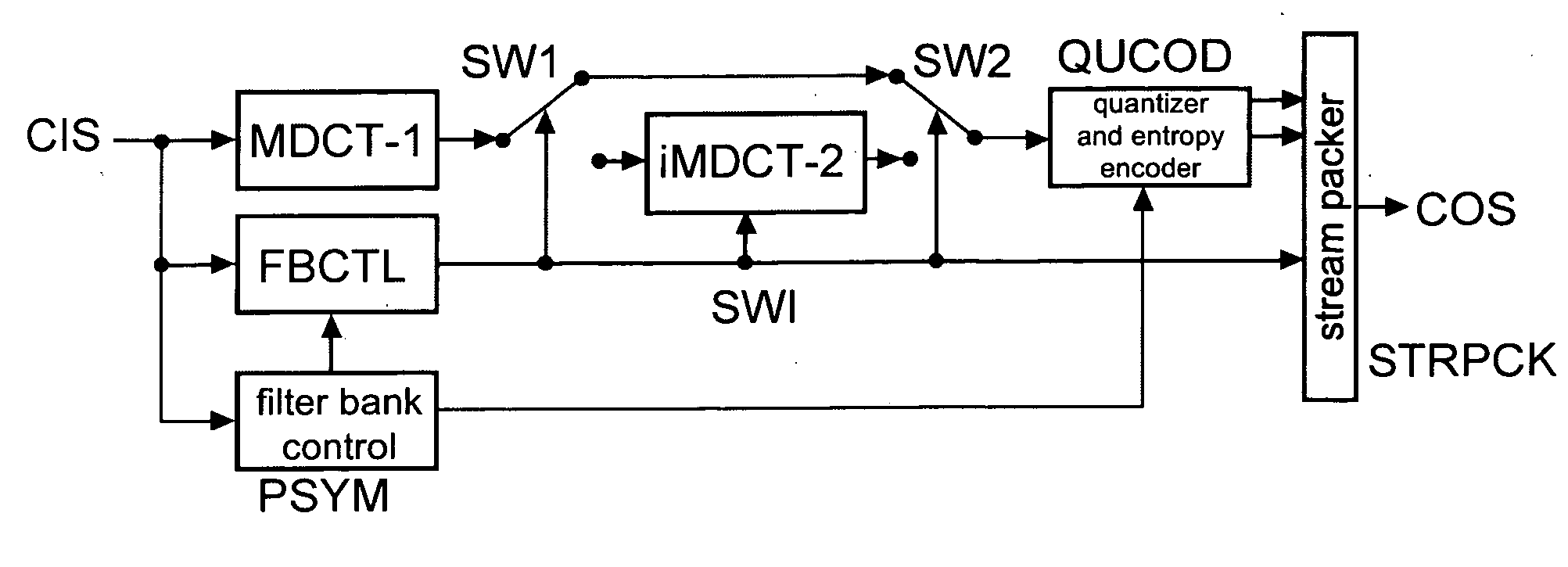

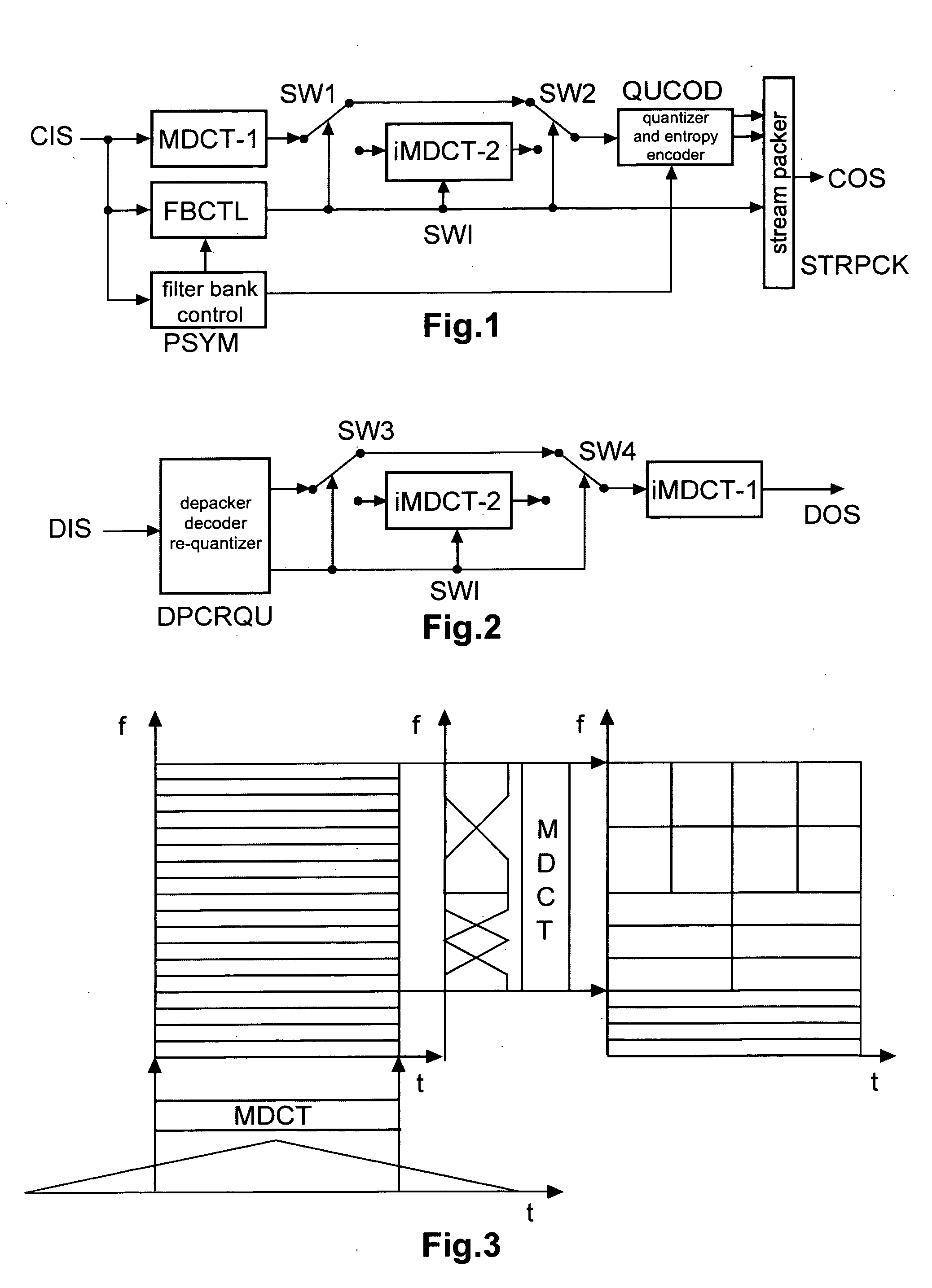

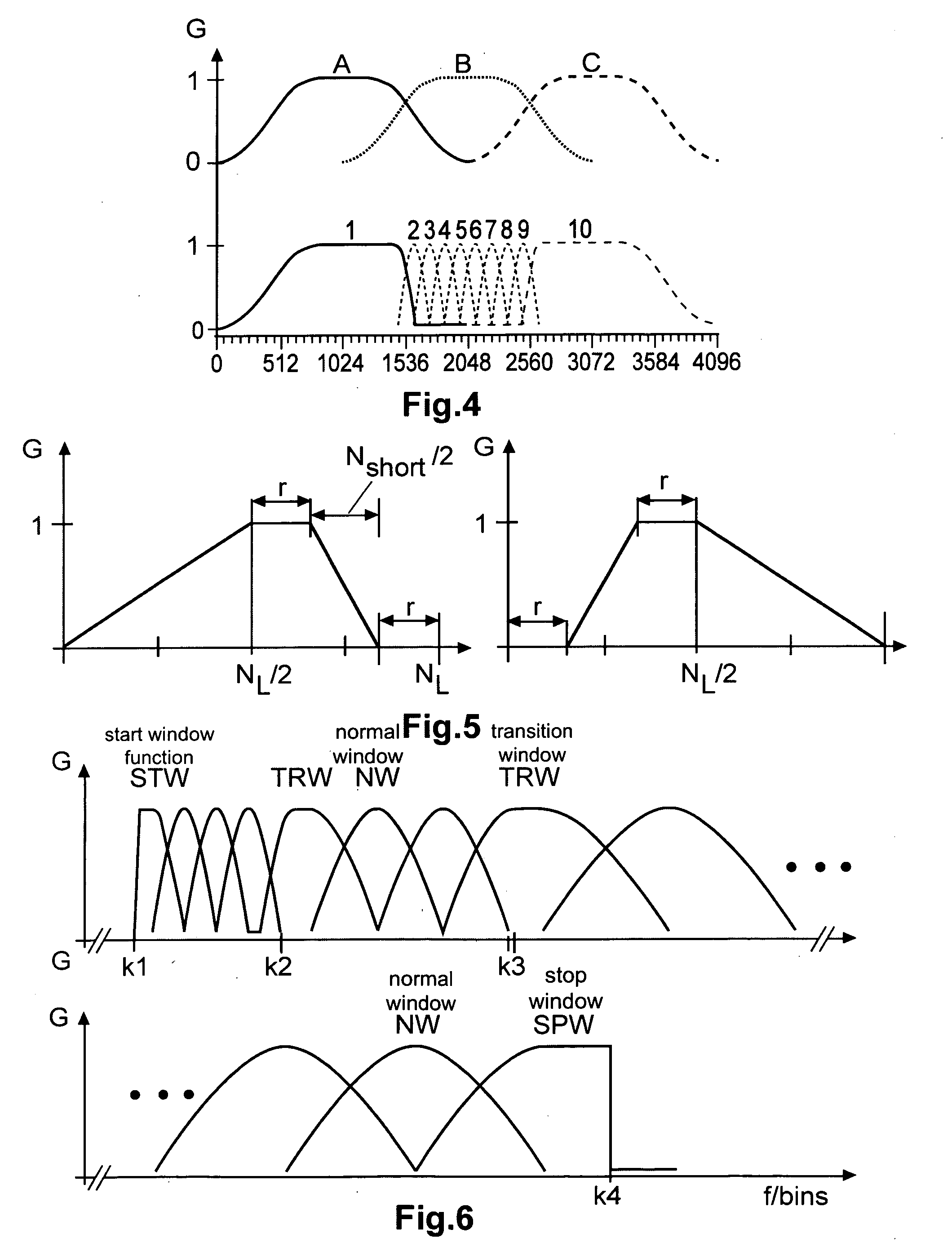

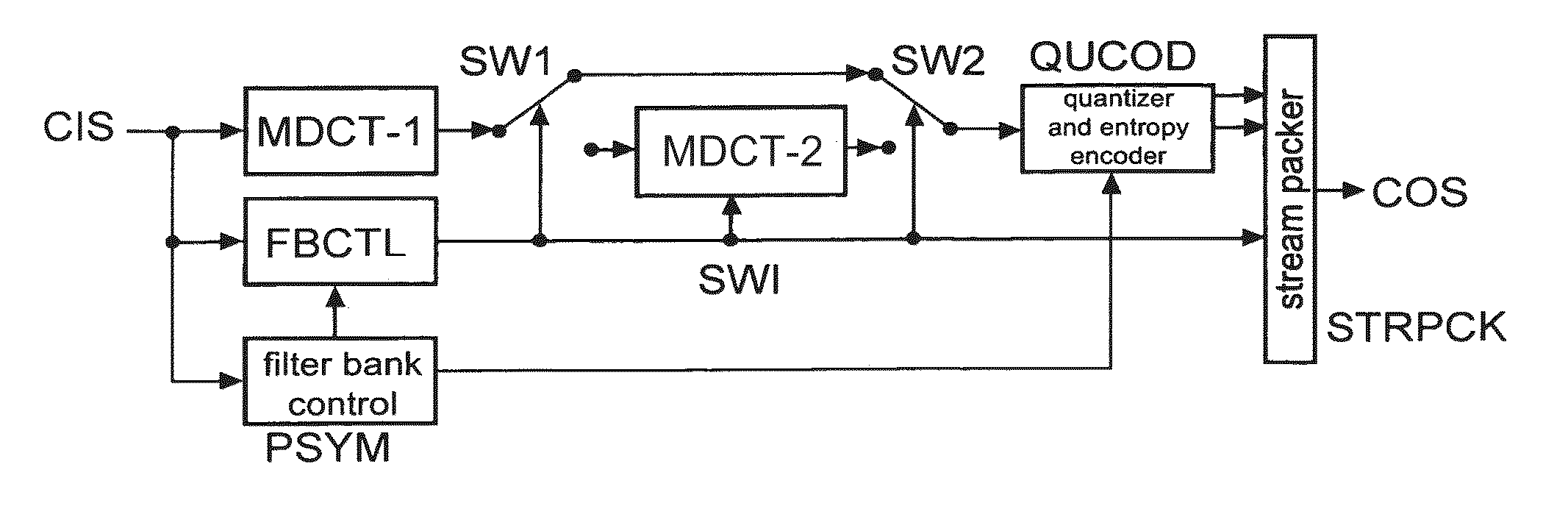

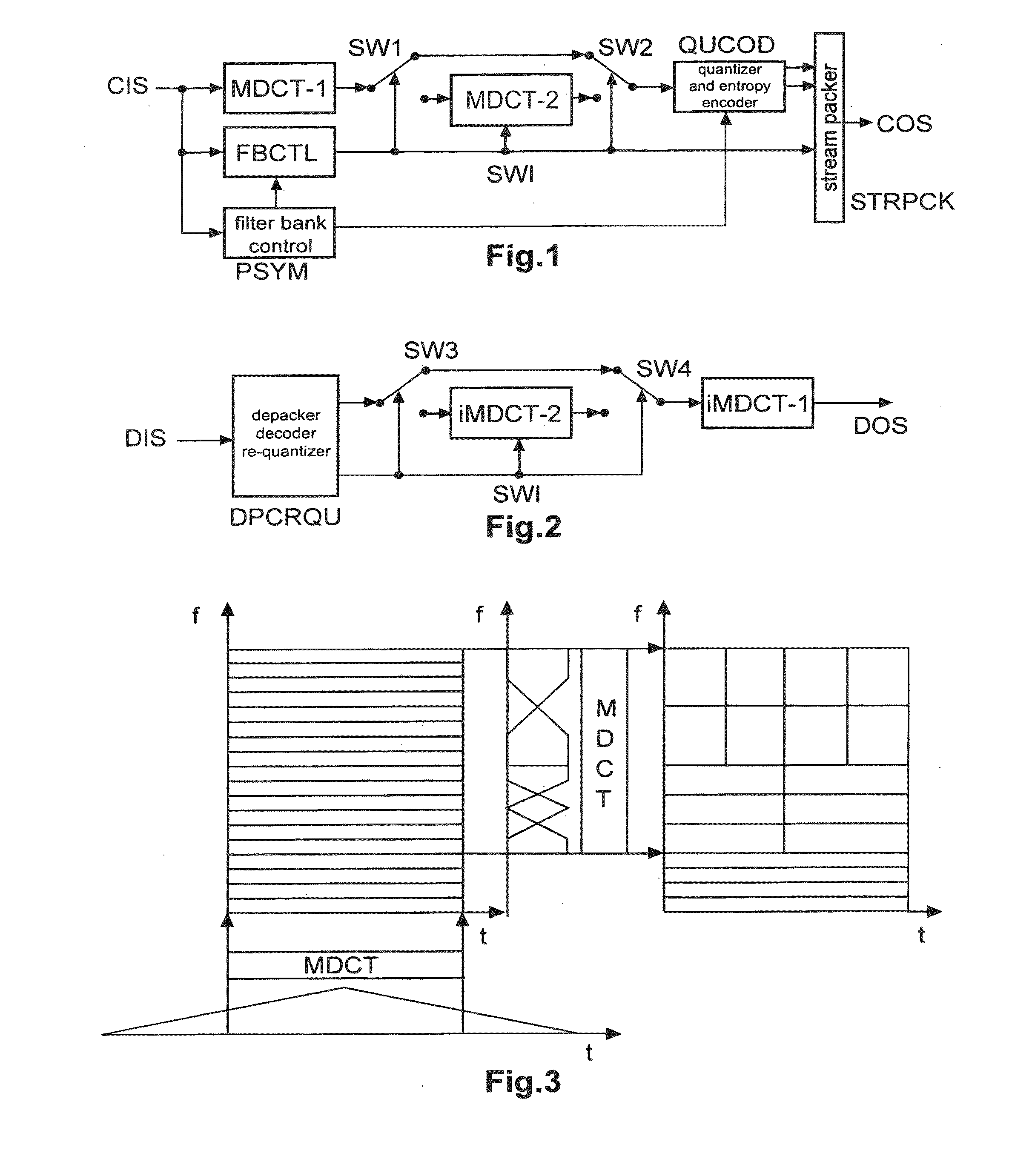

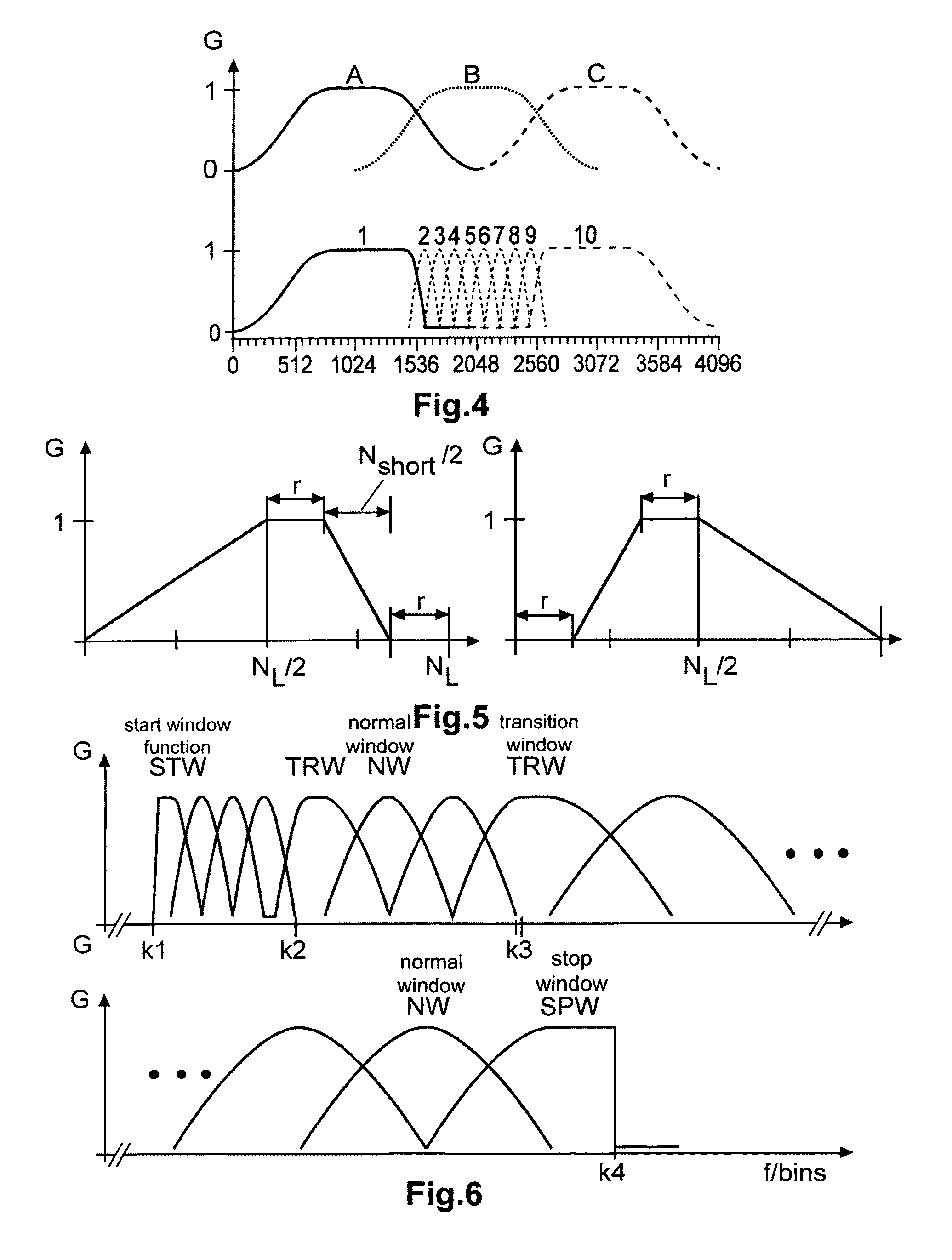

Perceptual audio codecs make use of filter banks and MDCT in order to achieve a compact representation of the audio signal, by removing redundancy and irrelevancy from the original audio signal. During quasi-stationary parts of the audio signal a high frequency resolution of the filter bank is advantageous in order to achieve a high coding gain, but this high frequency resolution is coupled to a coarse temporal resolution that becomes a problem during transient signal parts by producing audible pre-echo effects. The invention achieves improved coding / decoding quality by applying on top of the output of a first filter bank a second non-uniform filter bank, i.e. a cascaded MDCT. The inventive codec uses switching to an additional extension filter bank (or multi-resolution filter bank) in order to re-group the time-frequency representation during transient or fast changing audio signal sections. By applying a corresponding switching control, pre-echo effects are avoided and a high coding gain and a low coding delay are achieved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Method and apparatus for encoding and decoding an audio signal using adaptively switched temporal resolution in the spectral domain

ActiveUS8095359B2Quality improvementReduce encoding delaySpeech synthesisTemporal resolutionFrequency spectrum

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

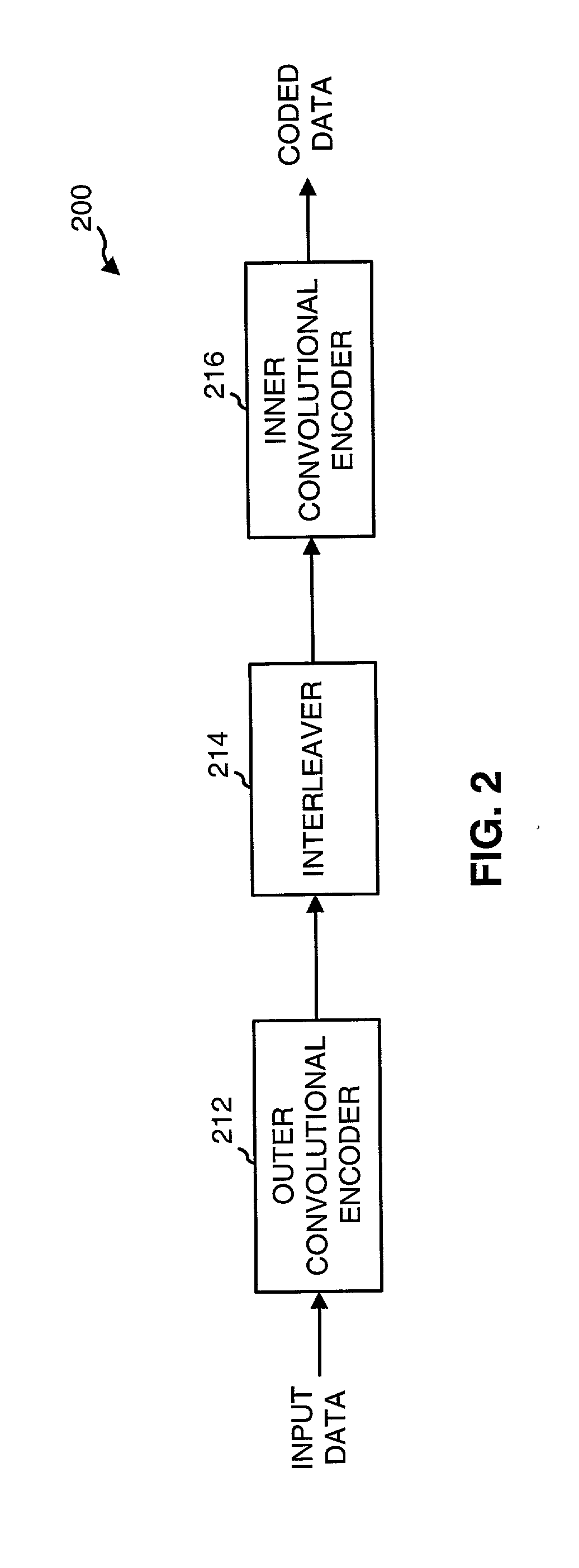

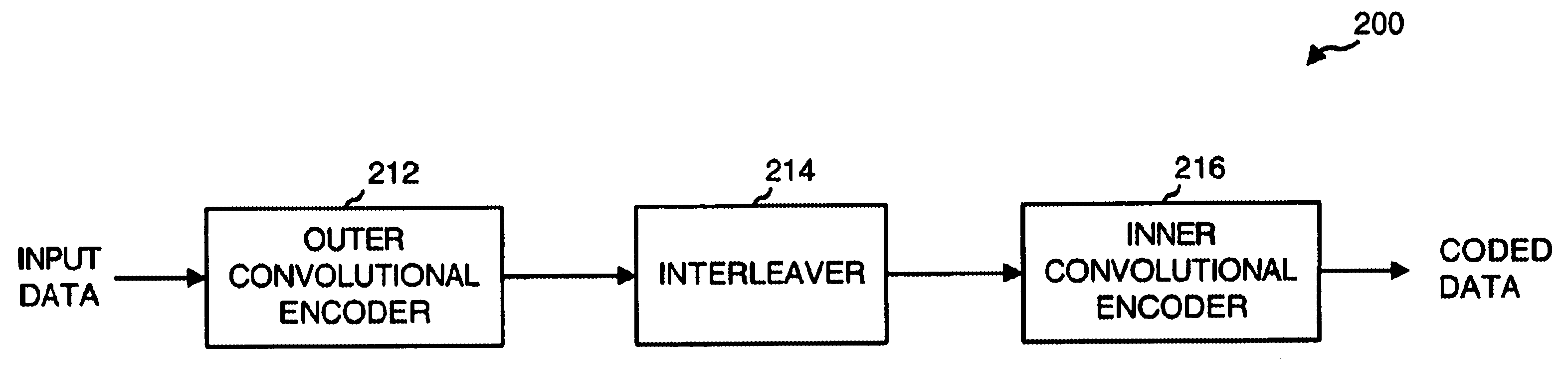

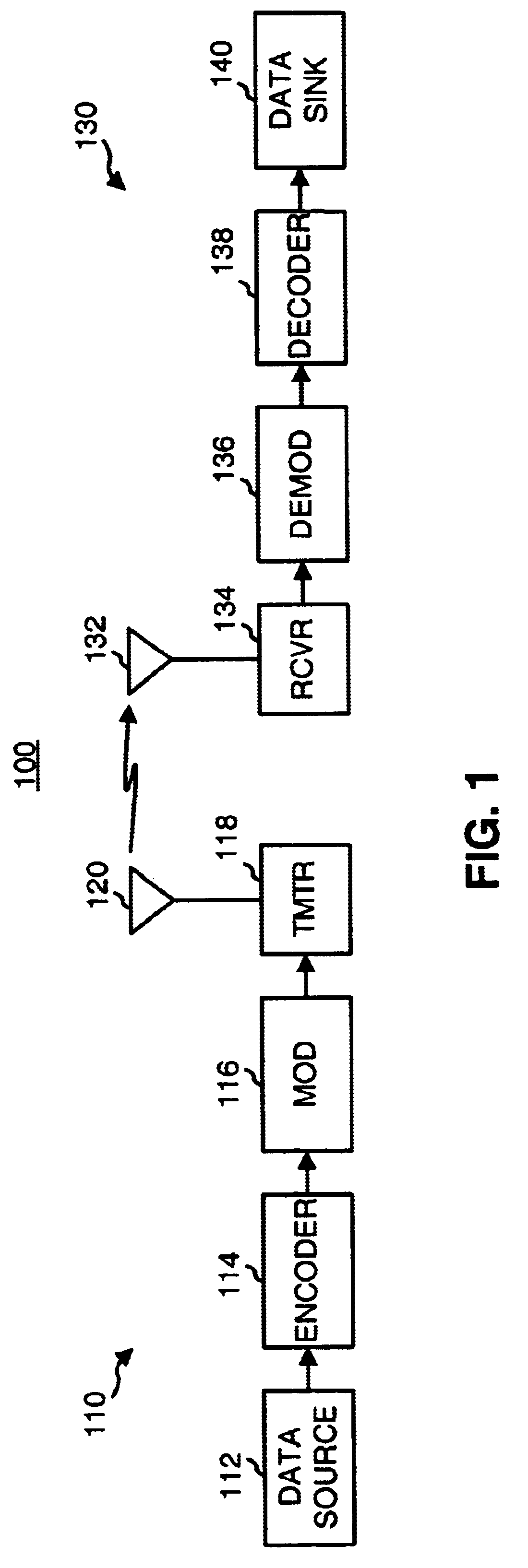

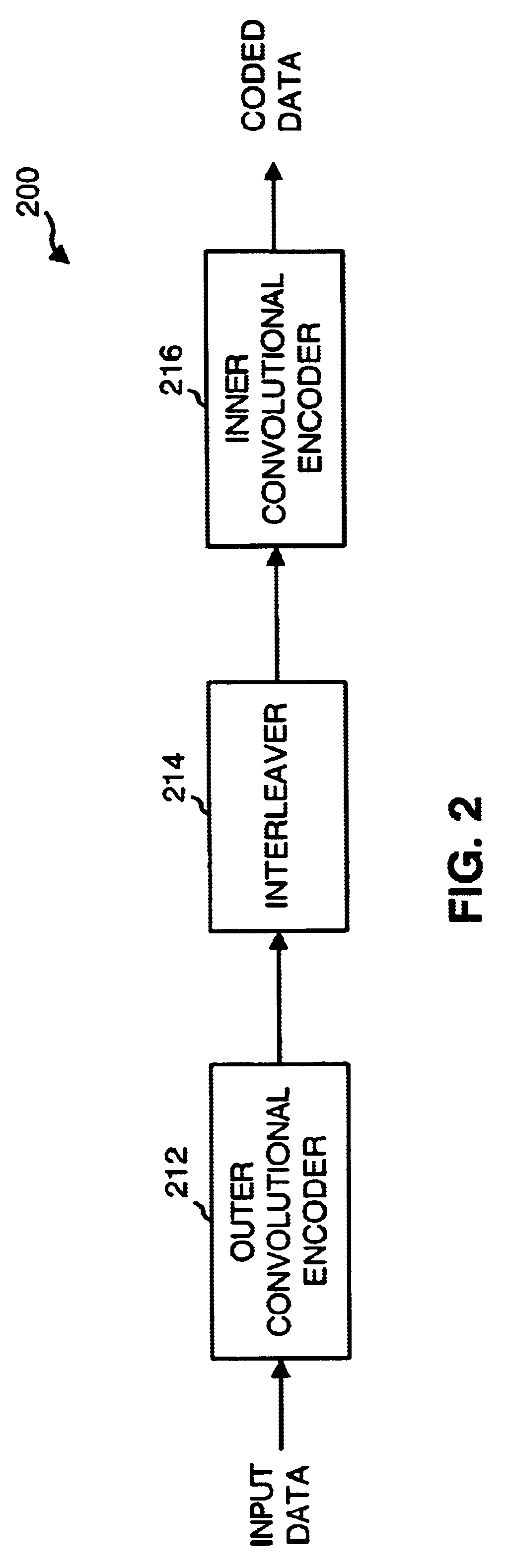

Method and apparatus for coding bits of data in parallel

InactiveUS20030101401A1Reduce encoding delayIncrease delayError correction/detection using convolutional codesError preventionComputer architectureCode point

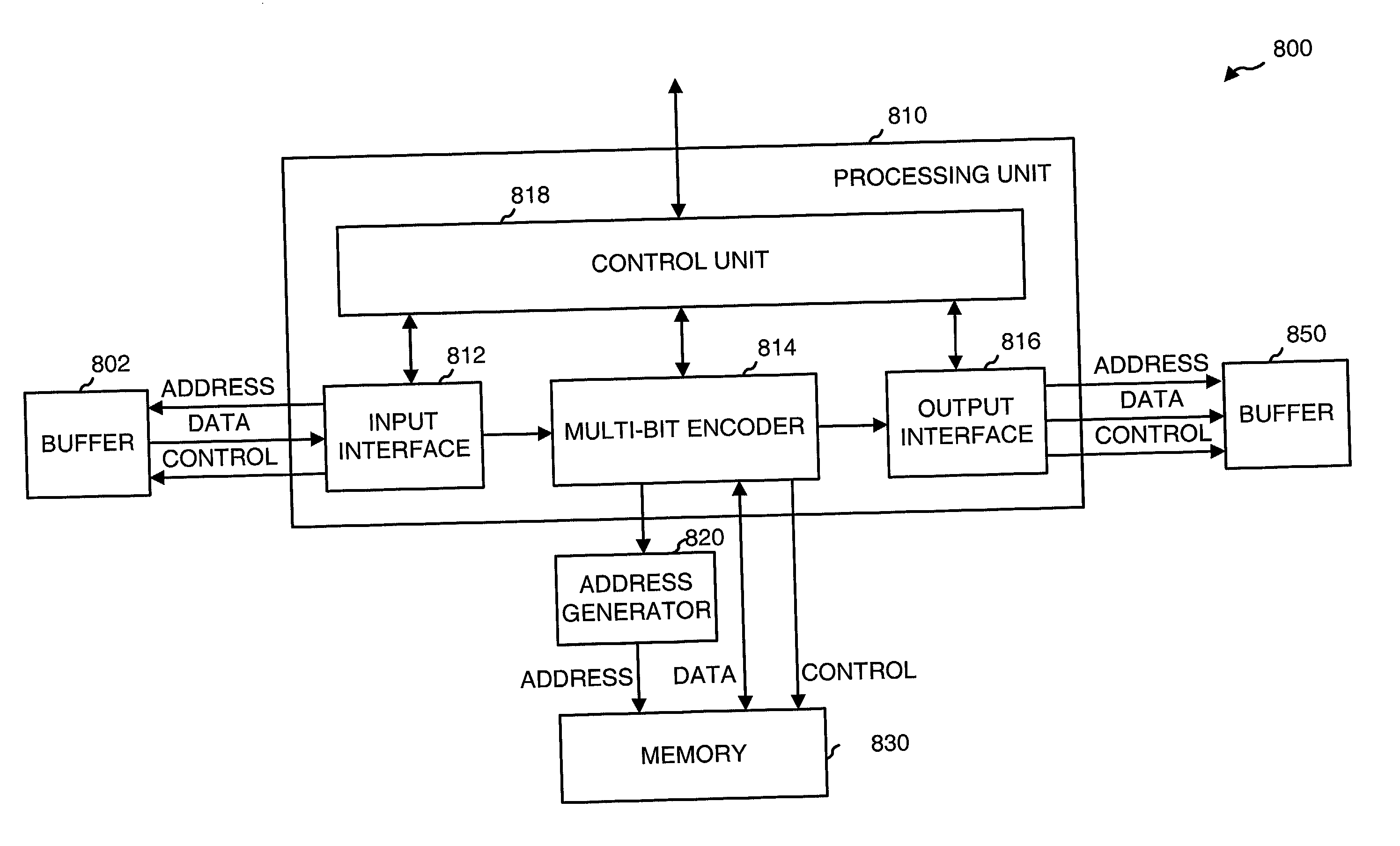

A concatenated encoder capable of coding multiple data bits in parallel and including a first (outer) encoder, a memory, and a second (inner) encoder coupled in cascade. The first encoder receives and codes M data bits in parallel in accordance with a first coding scheme to generate MR code bits. The memory receives and stores unpunctured ones of the MR code bits from the first encoder. The second encoder receives and codes N code bits in parallel in accordance with a second coding scheme to generate coded data. M and N can be any values (e.g., M>=8, N>=4). Each encoder can be a (e.g., a rate ½) convolutional encoder that implements a particular polynomial generator, and can be implemented with one or more look-up tables, a state machine, or some other design.

Owner:QUALCOMM INC

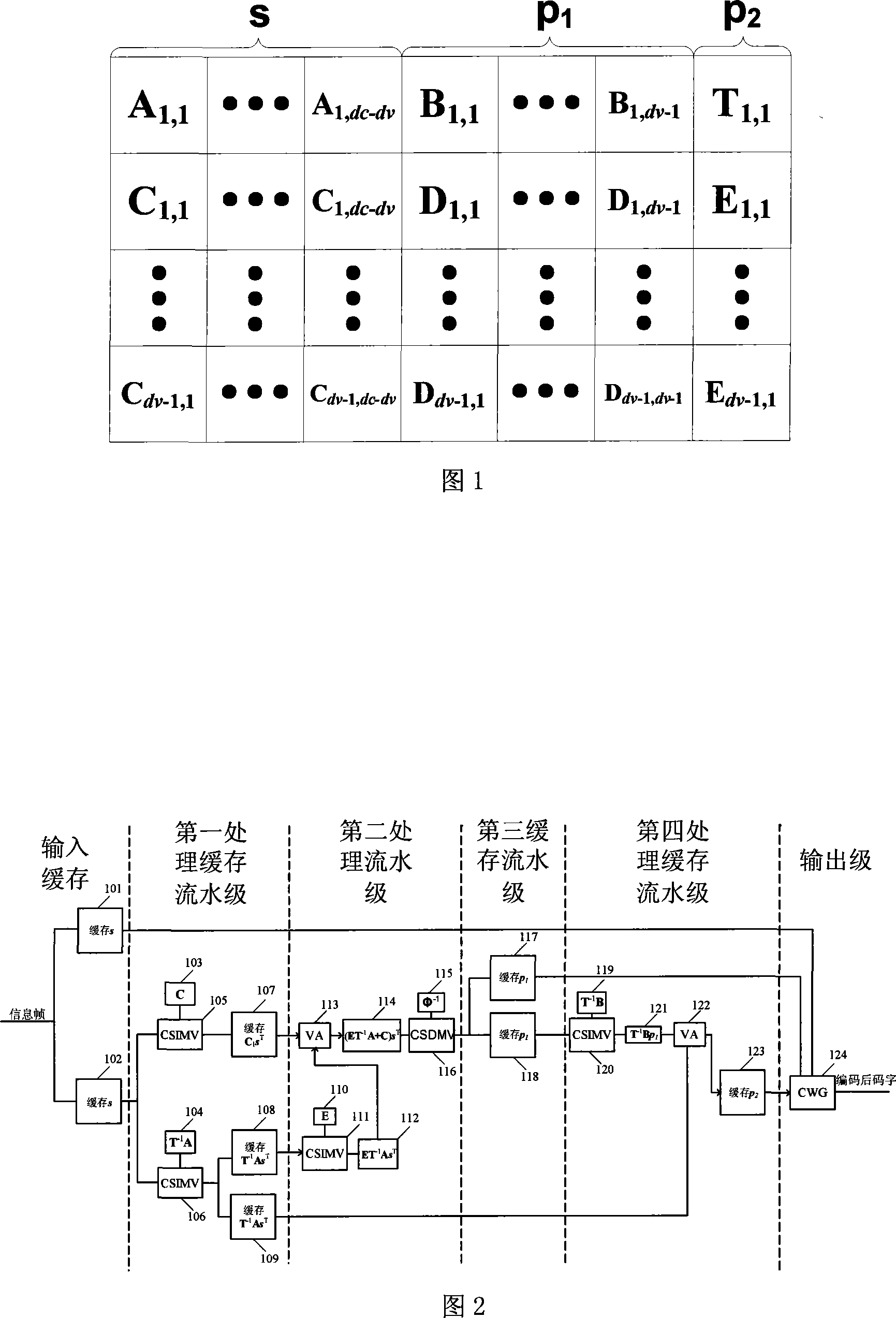

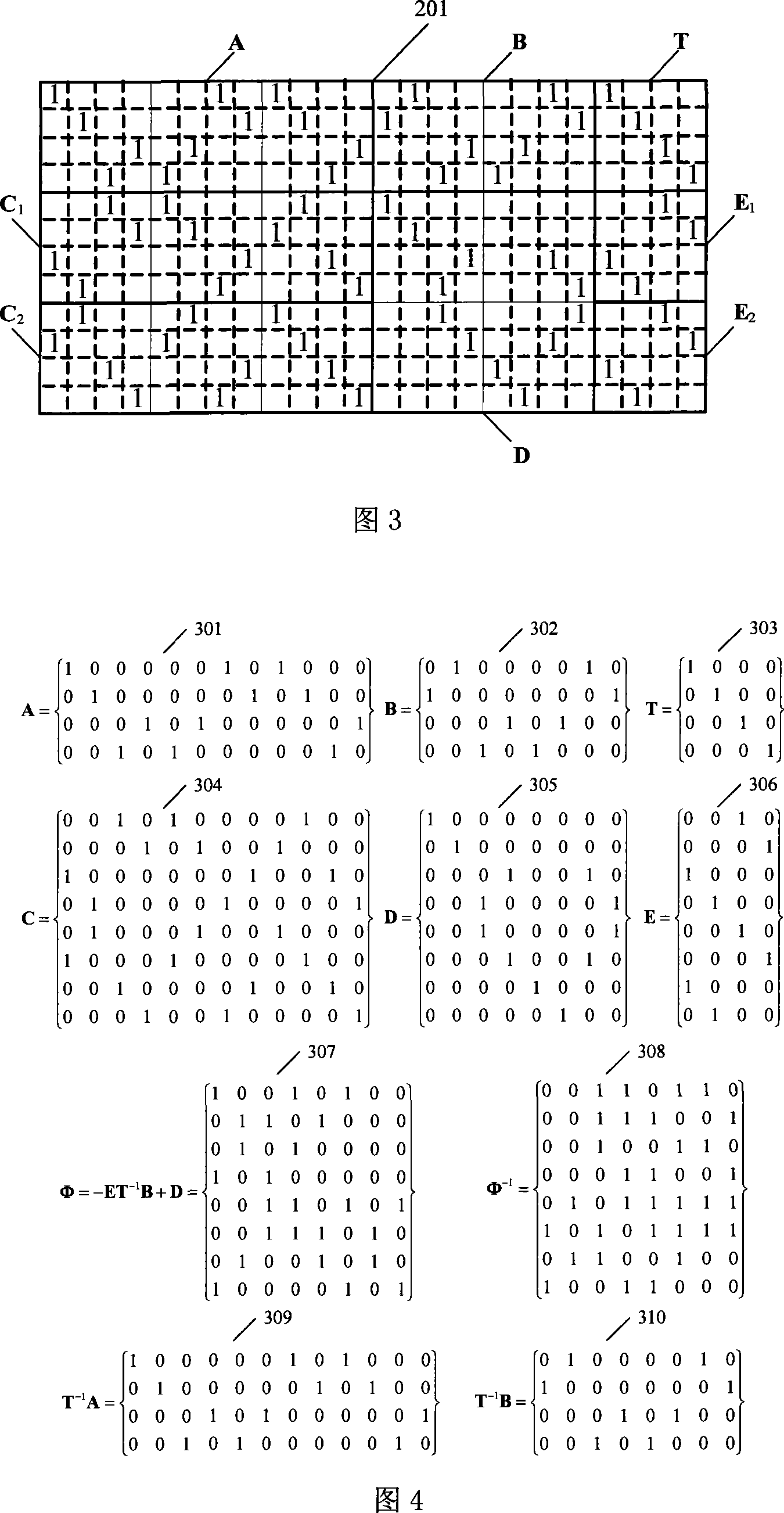

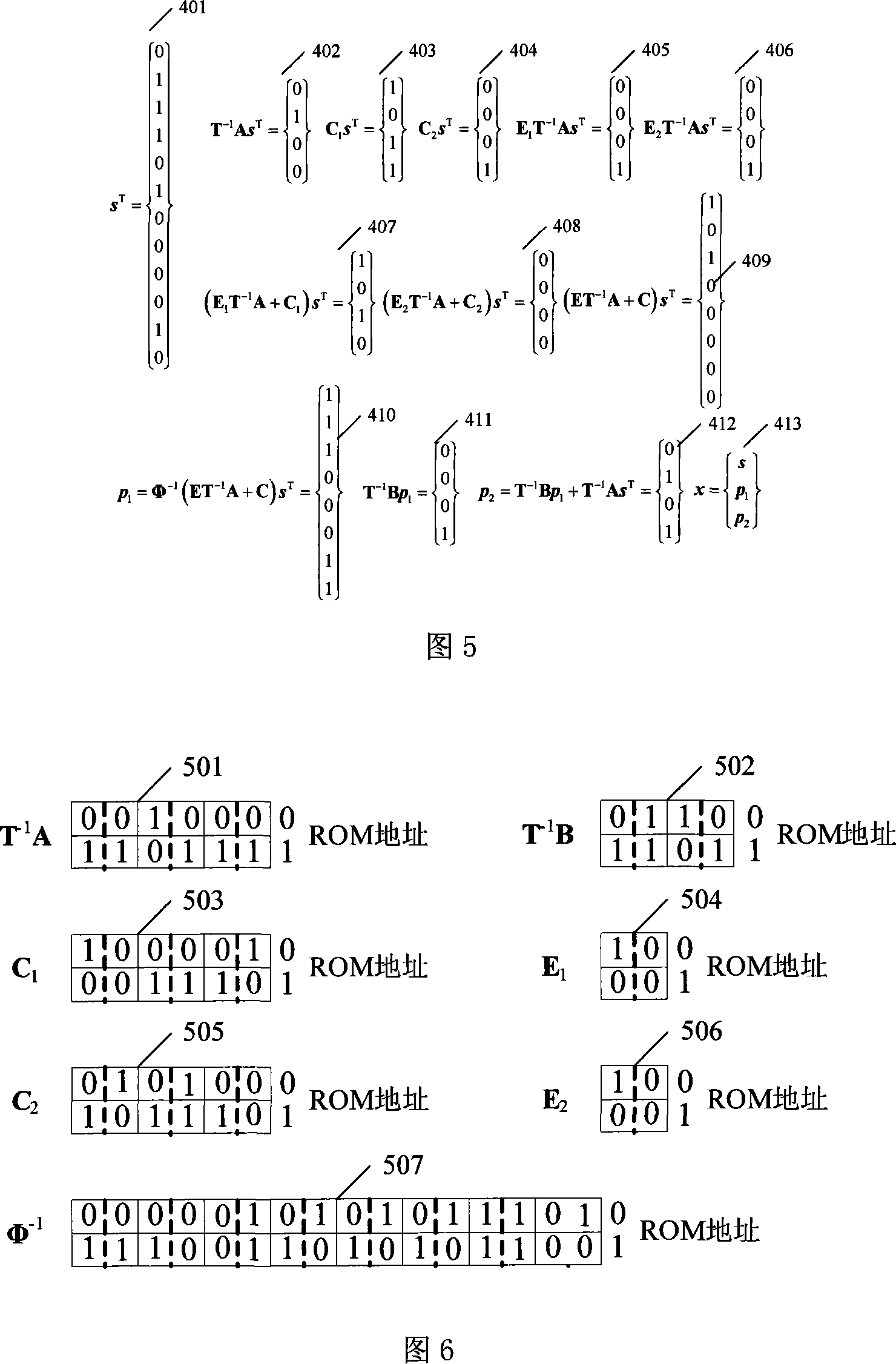

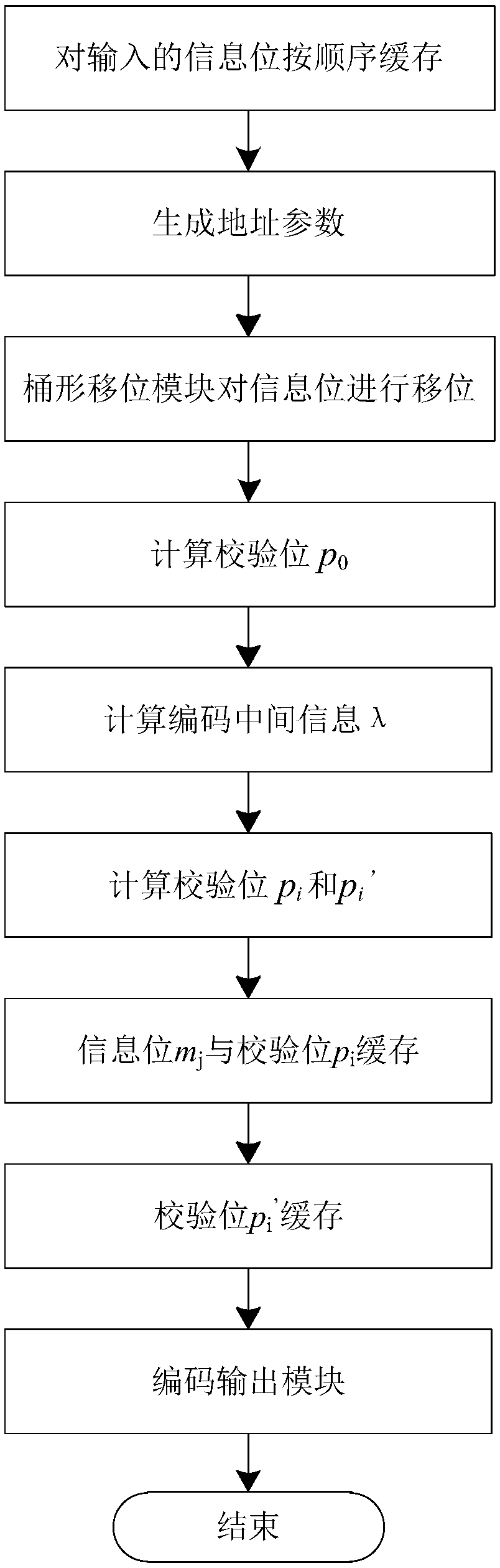

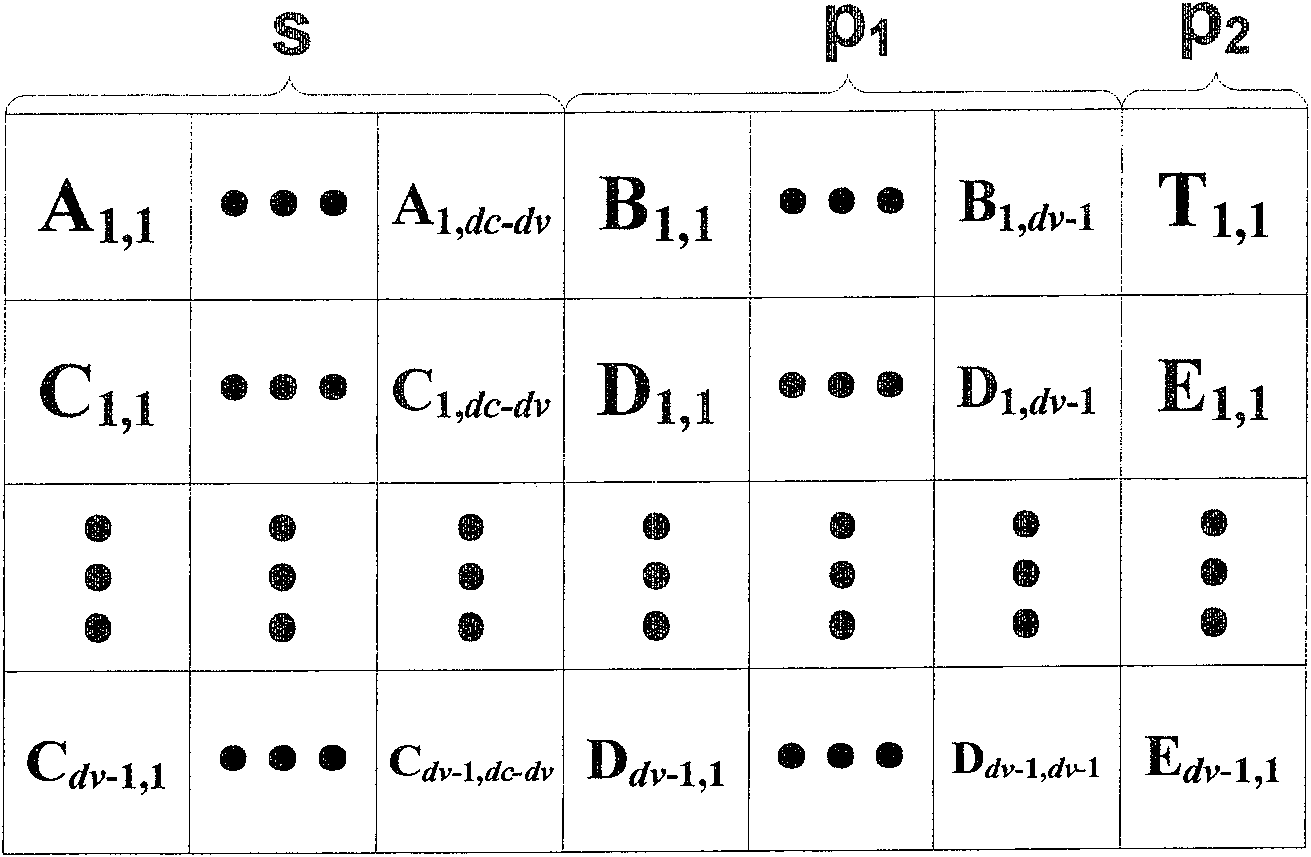

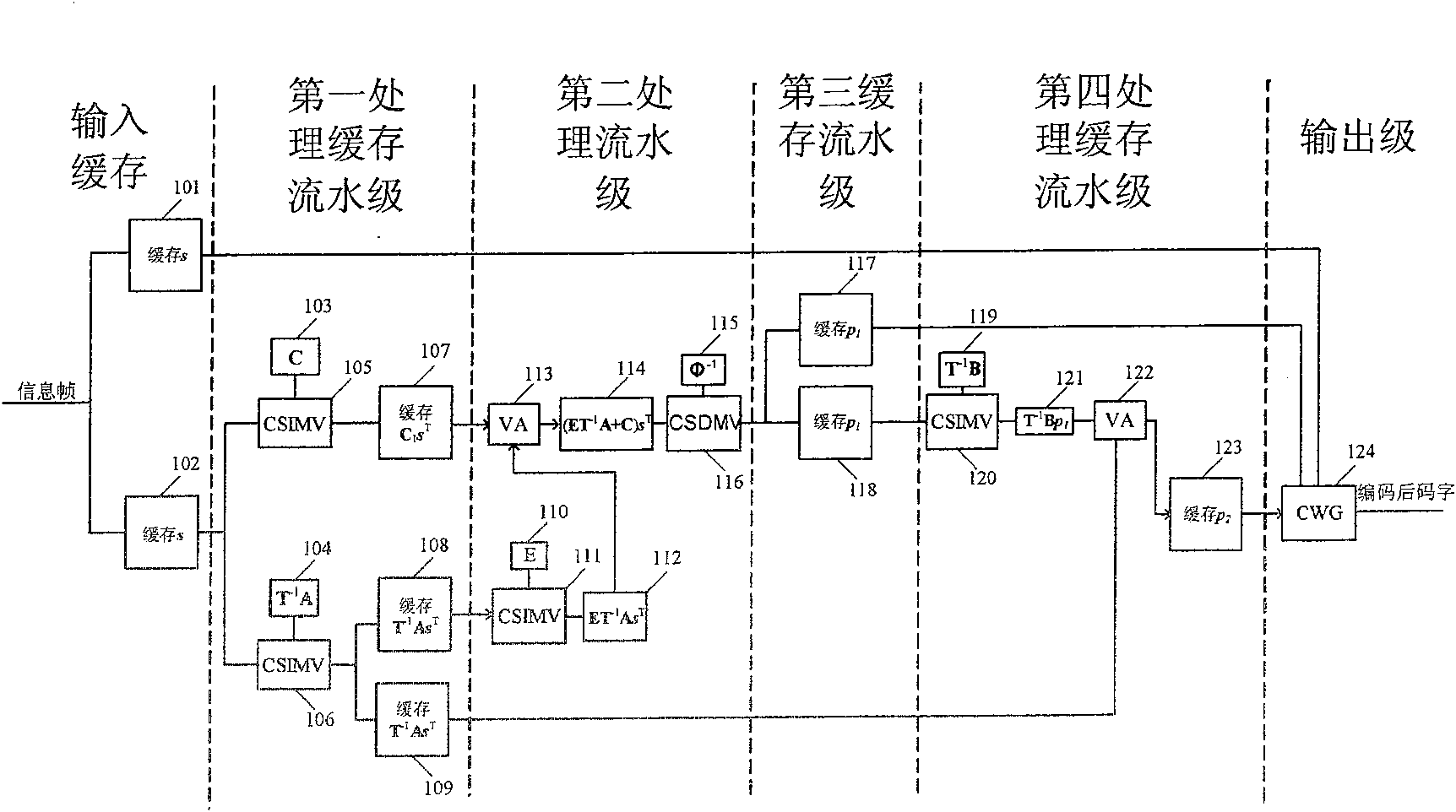

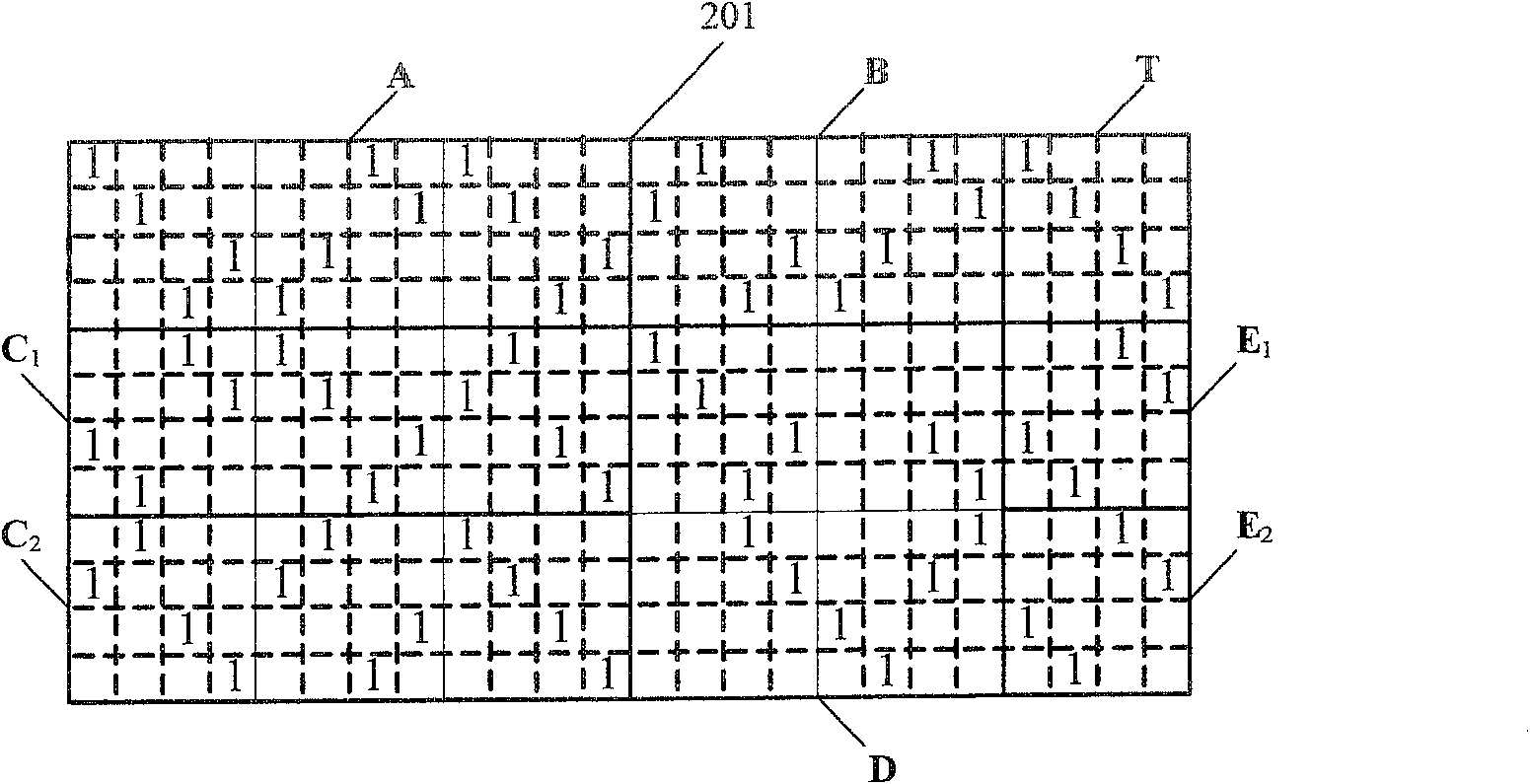

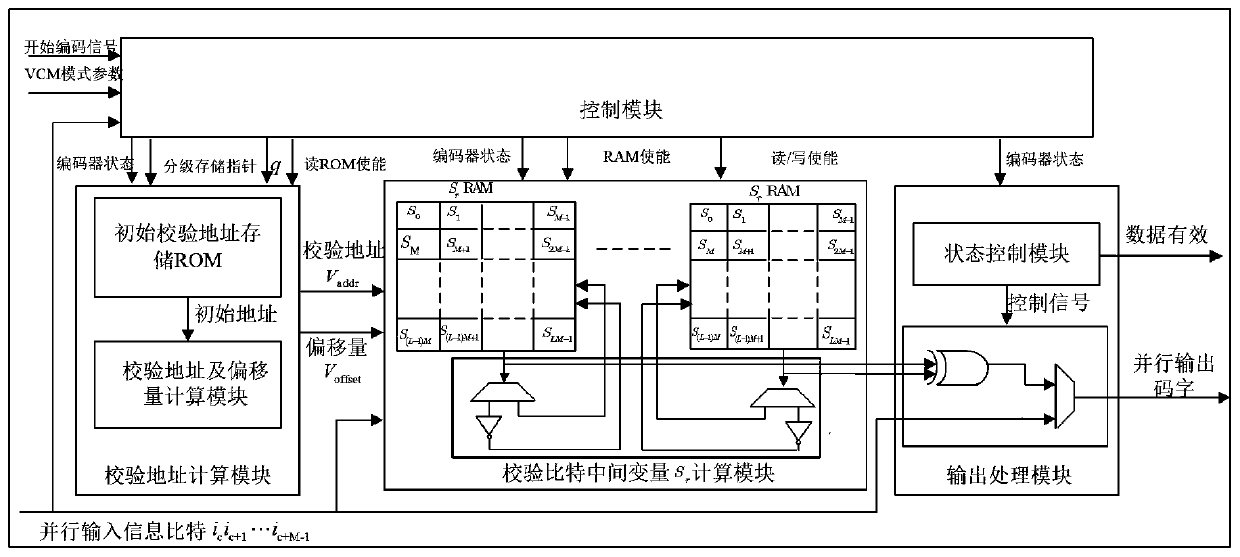

Encoder of LDPC code of layered quasi-circulation extended structure

InactiveCN101119118ASave resourcesImprove throughputError correction/detection using multiple parity bitsVariable-length codeEuclidean vector

The present invention discloses a coder of LDPC code used in hierarchical quasi-cyclic expansion structure, comprising an input cache, a first depositing and caching pipeline grade, a second depositing pipeline grade, a third caching pipeline grade, a fourth depositing and caching pipeline grade and an output grade. By utilizing the character that the check matrix H is formed by connecting the quasi-cyclic sift matrix, the present invention simplifies the pipeline structure of the RU coding method, reduces the grades of the pipeline from sixth grade to fourth grade, and shortens the coding delay. Besides, the present invention decreases the largest pipeline delay and increases the coding thuoughput according to the fulfilling character of the main functional module. And the present invention also reduces the energy consumption of the coder ROM according to the operational character of the quasi-cyclic sift matrix; replaces the sparse matrixmultiply vector in the RU method with the quasi-cyclic sift unit matrix multiply vector; and replaces the non sparse matrix multiply vector in the RU method with the quasi-cyclic sift matrix multiply vector. A larger storing space can be remained in the ping pong RAM amid the grades to fit the demand of the variable length code and the VBR.

Owner:SHANGHAI JIAO TONG UNIV

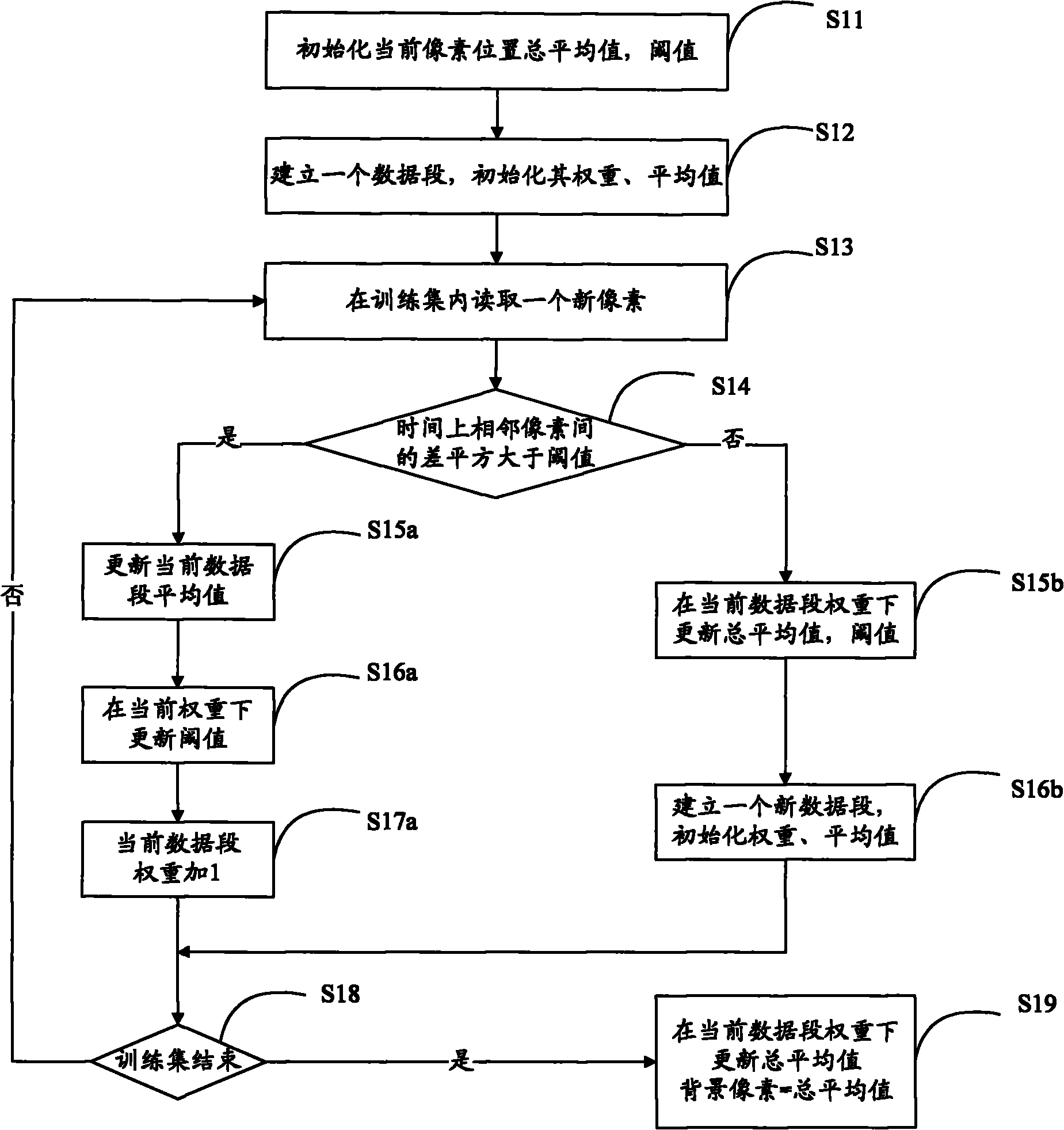

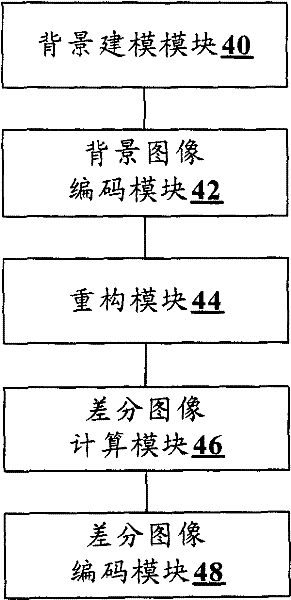

Background modeling-based static camera video compression method and background modeling-based static camera video compression system

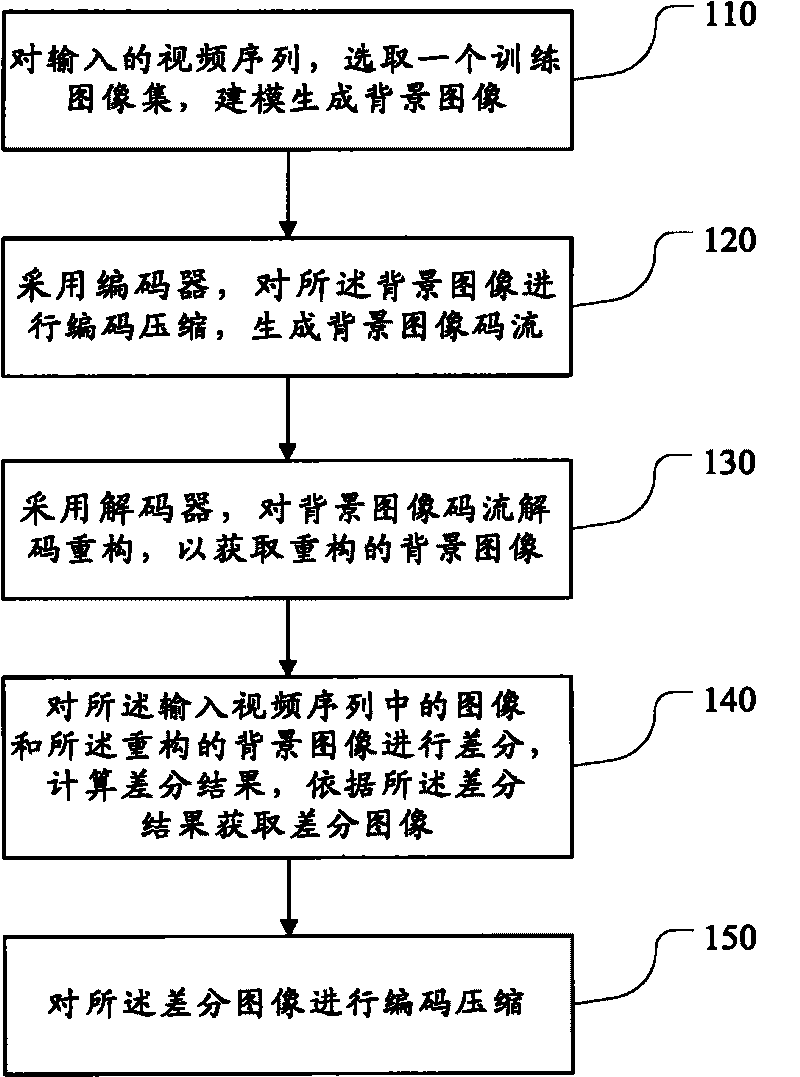

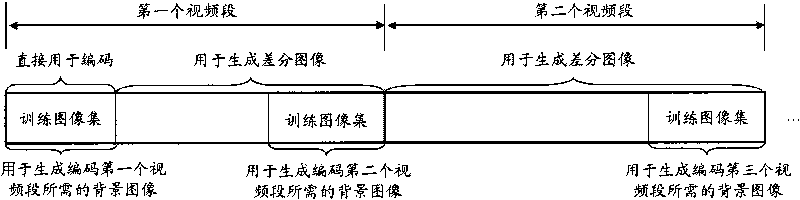

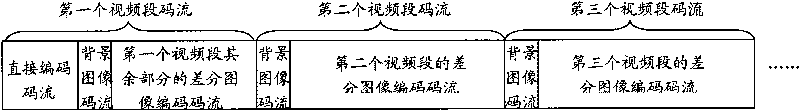

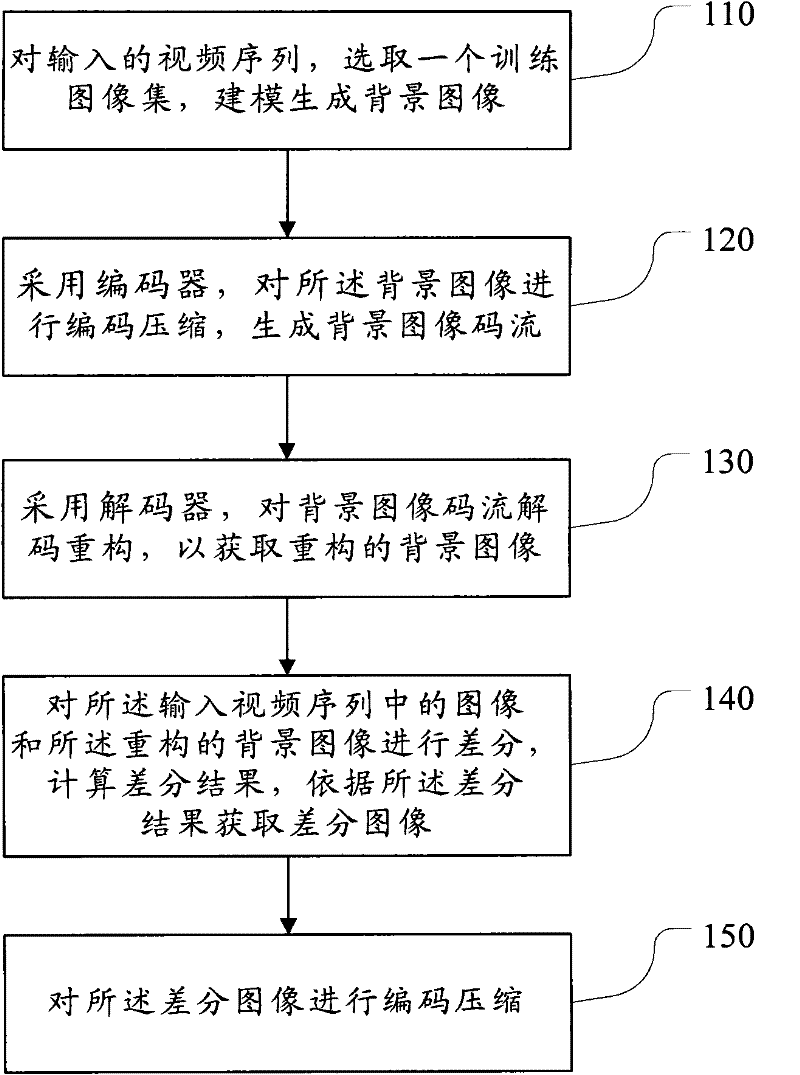

ActiveCN101742319AAvoid splittingImprove compression efficiencyTelevision systemsDigital video signal modificationVideo sequenceCompression method

The invention discloses a background modeling-based static camera video compression method and a background modeling-based static camera video compression system. The method comprises the following steps: for an input video sequence, selecting a training image set and modeling the selected training image set to generate a background image; adopting a coder to encode and compress the background image to generate a background image code stream; adopting a decoder to decode and reconstruct the background image code stream to acquire a reconstructed background image; differentiating images in the input video sequence and the reconstructed background image, calculating a differentiation result and acquiring a differential image according to the differentiation result; and encoding and compressing the differential image. In the method and the system, a fixed scene part and other parts of video are compressed respectively by utilizing the characteristic that a scene of the video sequence is fixed and establishing and updating a model describing the relatively fixed scene in the video so as to eliminate redundancy in the video sequence to a greater extent to obtain better compression performance.

Owner:PEKING UNIV

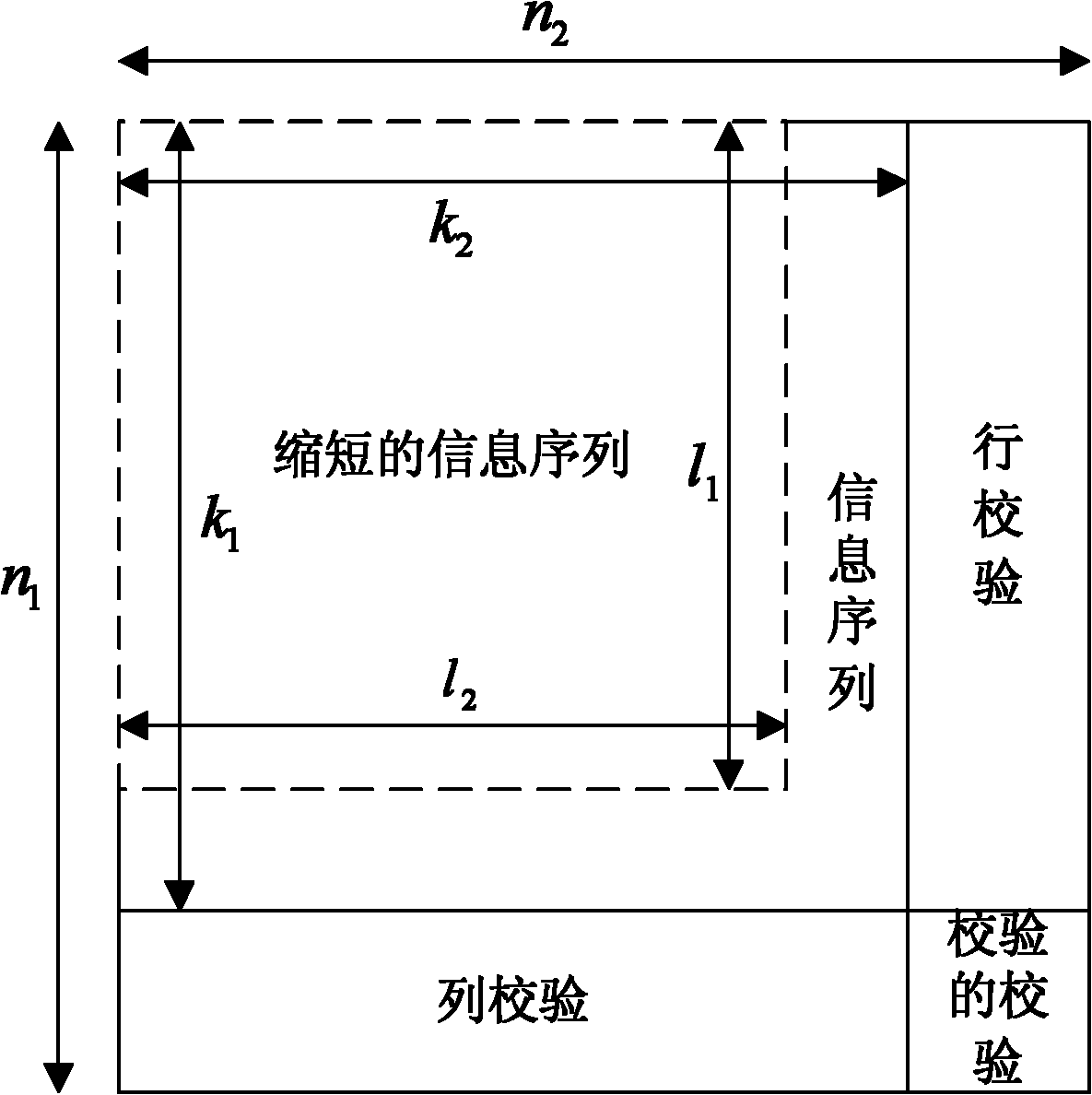

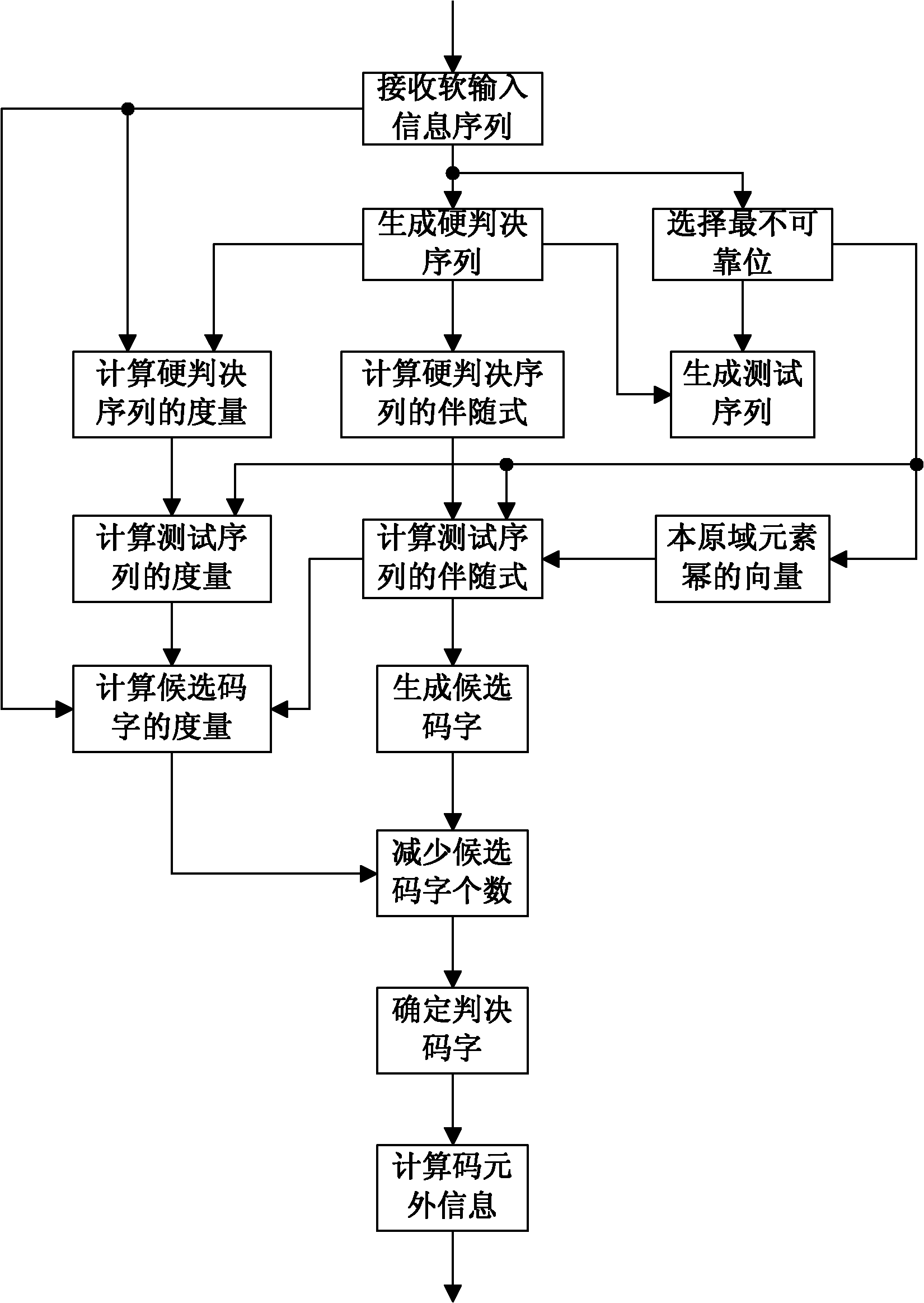

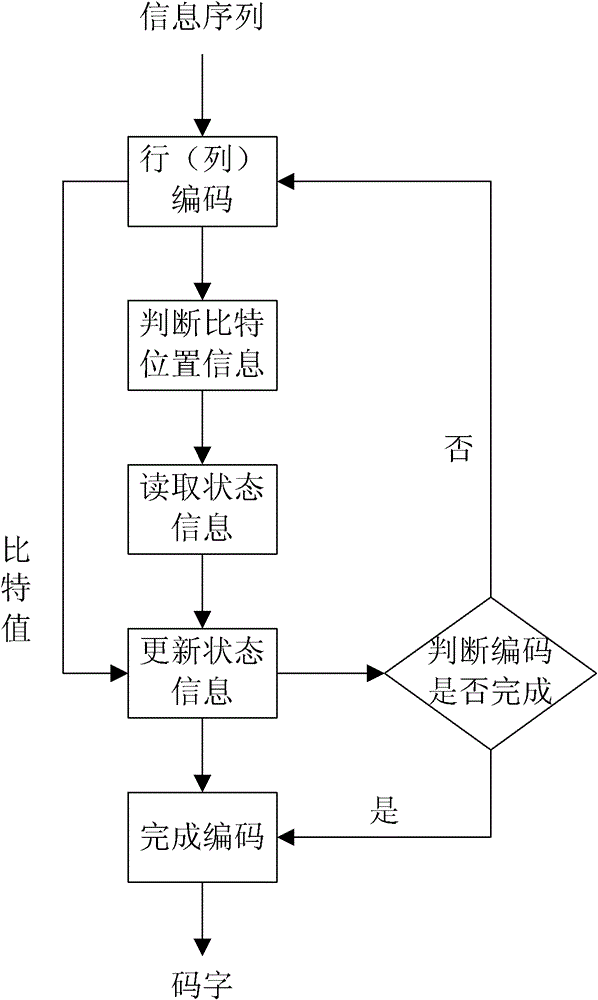

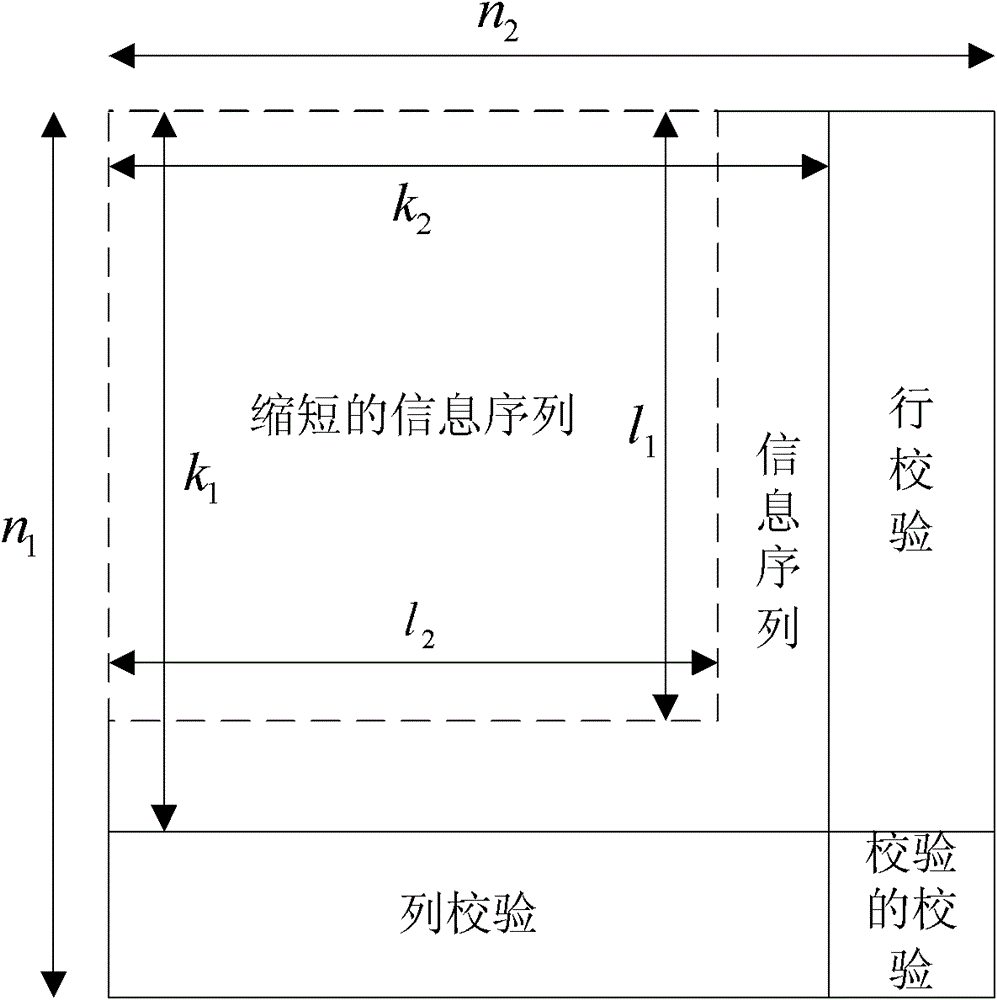

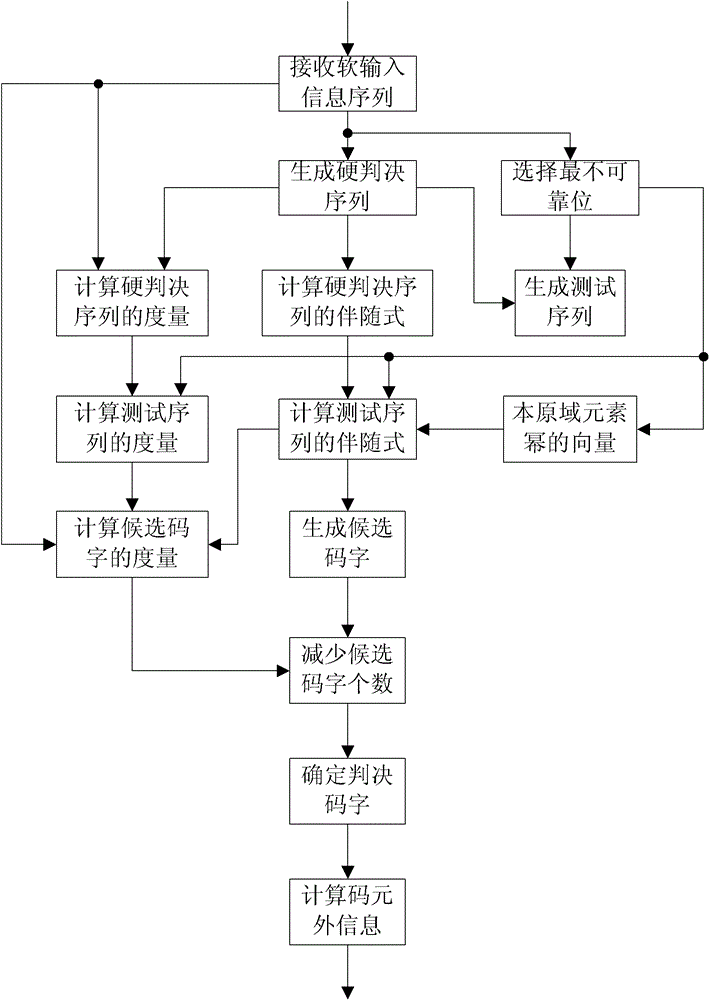

Encoding and decoding methods for shortening Turbo product code

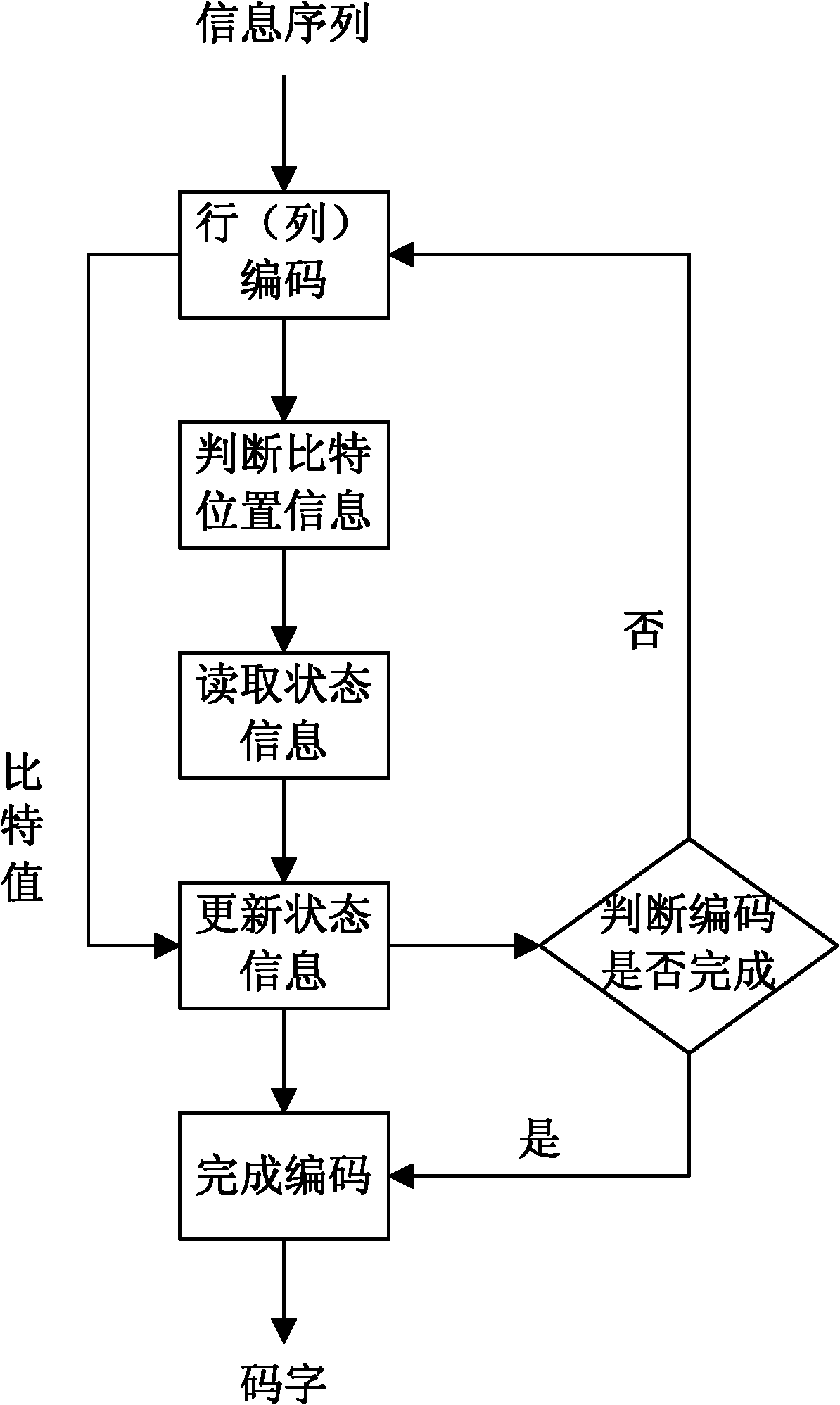

InactiveCN101958720AImprove data throughputReduce encoding delayError correction/detection by combining multiple code structuresTest sequenceCoded element

The invention relates to encoding and decoding methods for shortening a Turbo product code. The encoding method comprises the following steps of: performing row or column encoding on an information sequence to be encoded; performing parallel encoding on code words of row or column component codes generated by the row or column encoding; and judging whether the encoding is finished. The decoding method comprises the following steps of: generating a hard decision sequence of a soft-input information sequence; selecting the least reliable bits in the soft-input information sequence; generating atest sequence according to the hard decision sequence and the least reliable bits; decoding the test sequence to generate candidate code words; calculating the measurement of the candidate code wordsand the soft-input information sequence; reducing the number of the candidate code words; determining decision code words according to the measurement of the candidate code words; and calculating external information of each code element in the decision code words. The encoding method has the advantages of improving data throughput and reducing encoding delay; and the decoding method has the advantages of saving a mass of logical resources and storage resources, particularly well balancing decoding complexity and data throughput under the condition of longer code length of component codes.

Owner:XIDIAN UNIV

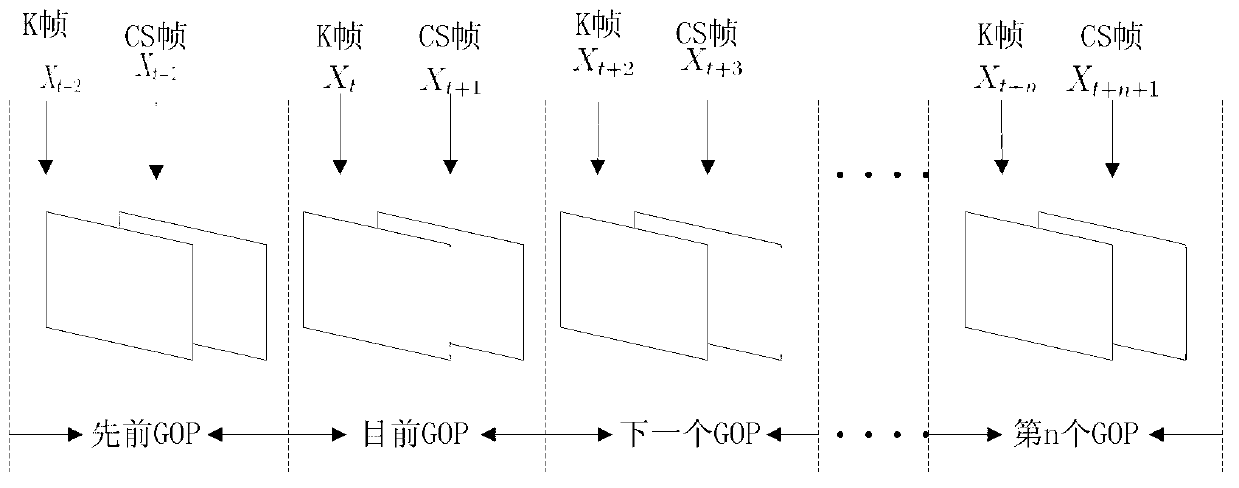

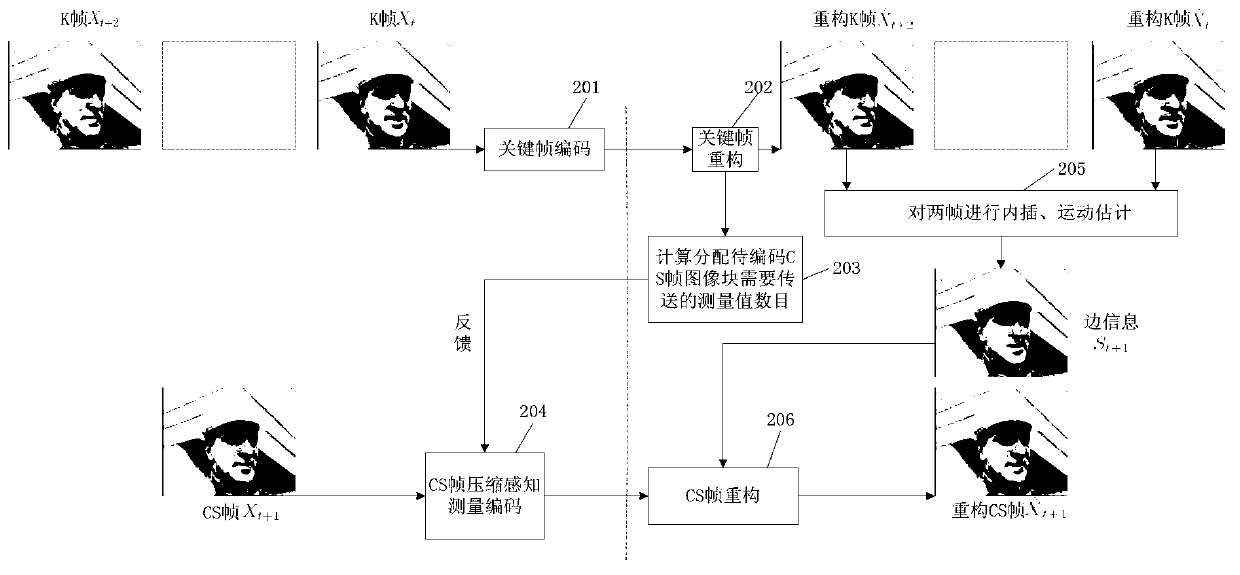

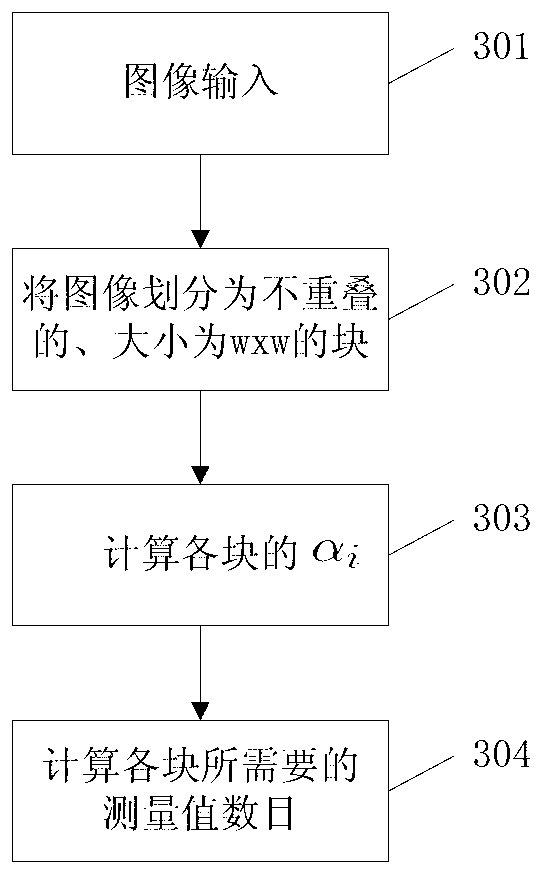

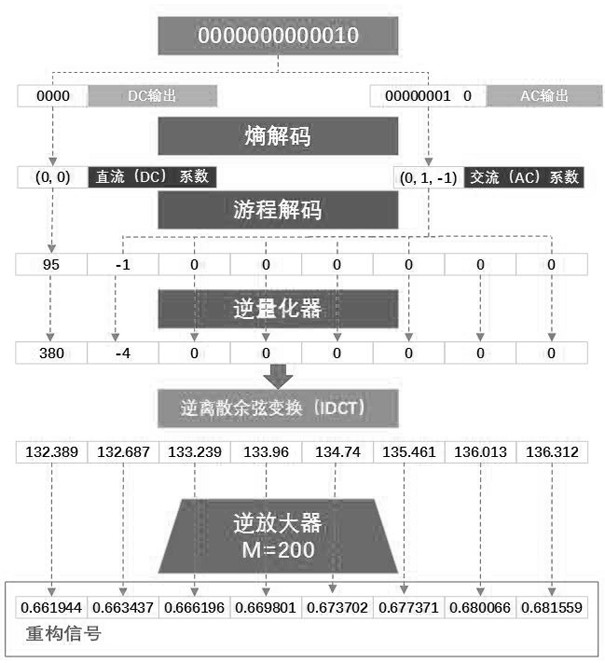

Compressed sensing coding and decoding method for distributed video coding non-critical frame

InactiveCN103347188AReduce encoding delayImprove refactoring qualityTelevision systemsDecoding methodsComputer architecture

The invention discloses a compressed sensing coding and decoding method for a distributed video coding non-critical frame. The method can calculate the number of required measured values for compressed sensing of corresponding image blocks in the non-critical frame according to DCT coefficient characteristics for reconstituting image blocks in the non-critical frame. The method can divide the image blocks into different type according to the required measurement number and can choose different coding methods according to the types of the image blocks. The compressed sensing coding and decoding method reduces complexity of compressed sensing coding and decoding of the distributed video coding non-critical frame and improves the quality of reconstitution images of the non-critical frame.

Owner:NANJING UNIV OF POSTS & TELECOMM

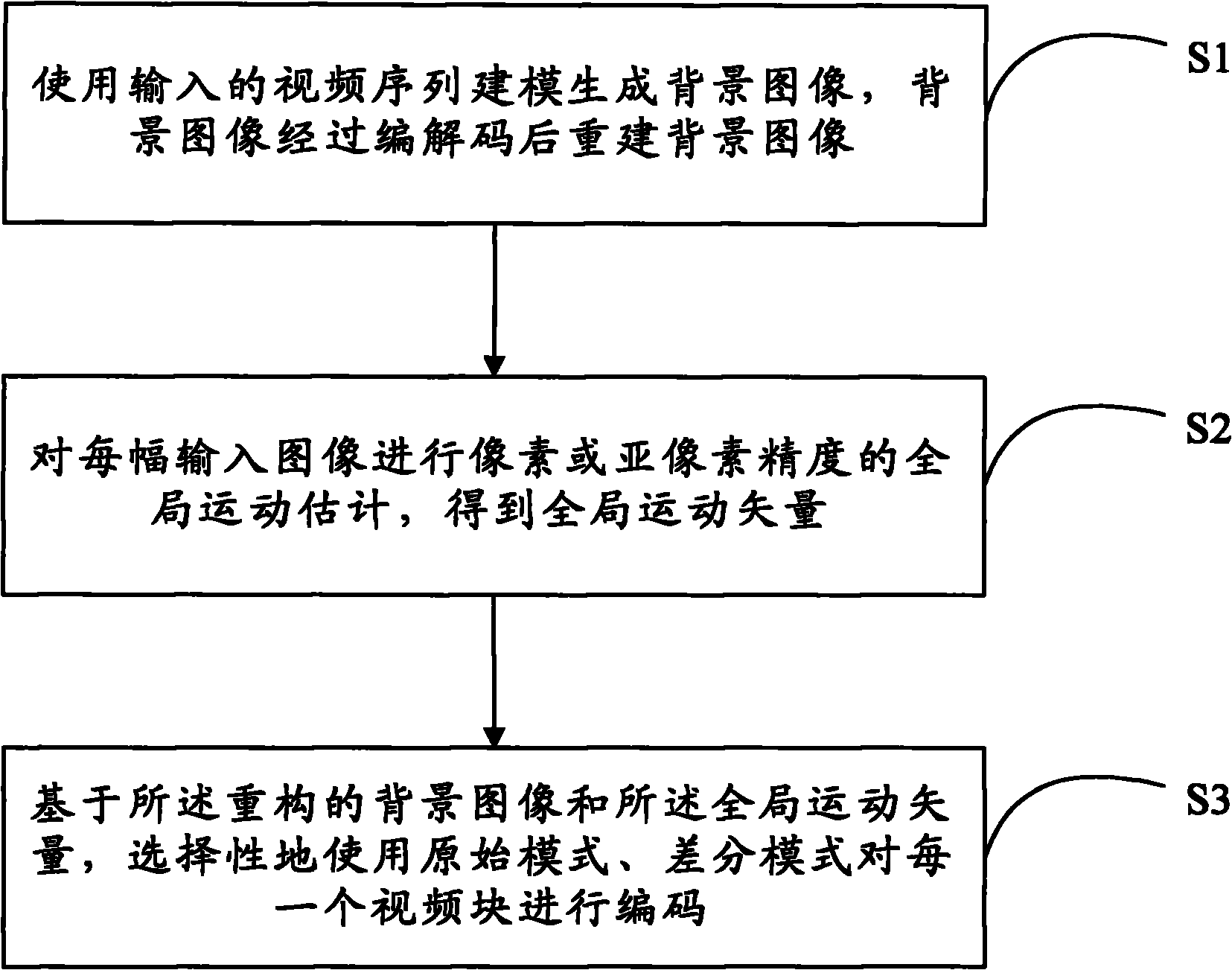

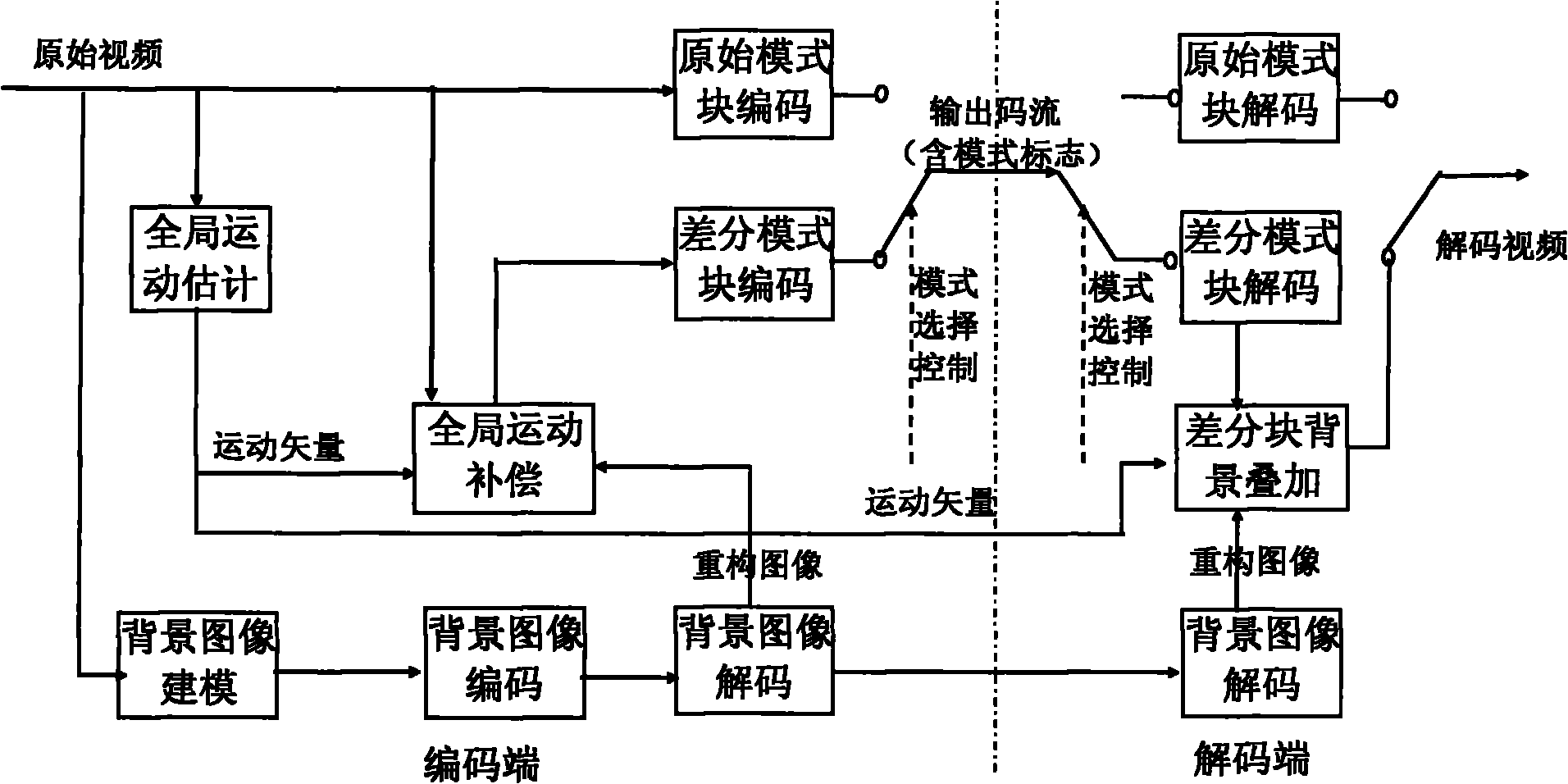

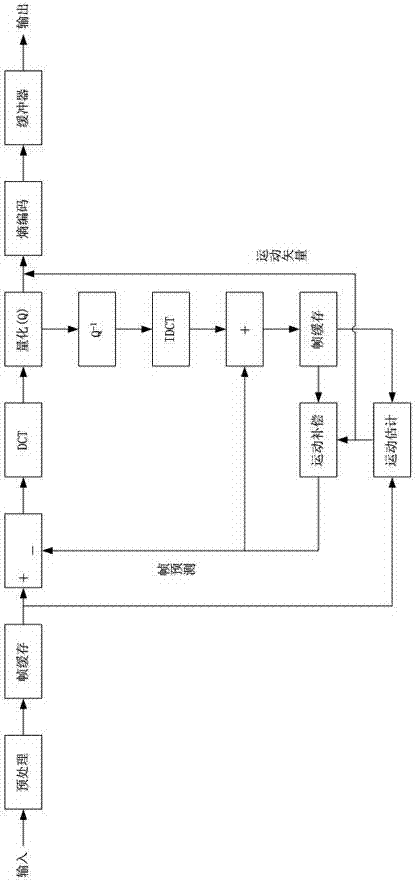

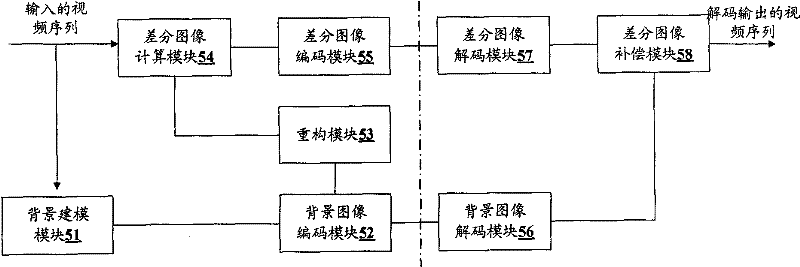

Video encoding/decoding method and system based on background modeling and optional differential mode

ActiveCN101883284AImprove encoding performanceEnsuring Coding EfficiencyImage analysisTelevision systemsMotion estimationMotion vector

The invention discloses video encoding / decoding method and system based on background modeling and an optional differential mode. The encoding method comprises the following steps of: modeling and generating a background image by using an input video sequence, and encoding to obtain a reconstructed background image; carrying out pixel or sub-pixel accuracy global motion estimation on each input image to obtain a global motion vector; and carrying out encoding on each video block by selectively using an original mode and a differential mode on the basis of the reconstructed background image and the global motion vector. The invention can improve the encoding performance and has the advantages of not increasing the encoding delay and being beneficial to further processing as the code streamcontains the background image per se.

Owner:PEKING UNIV

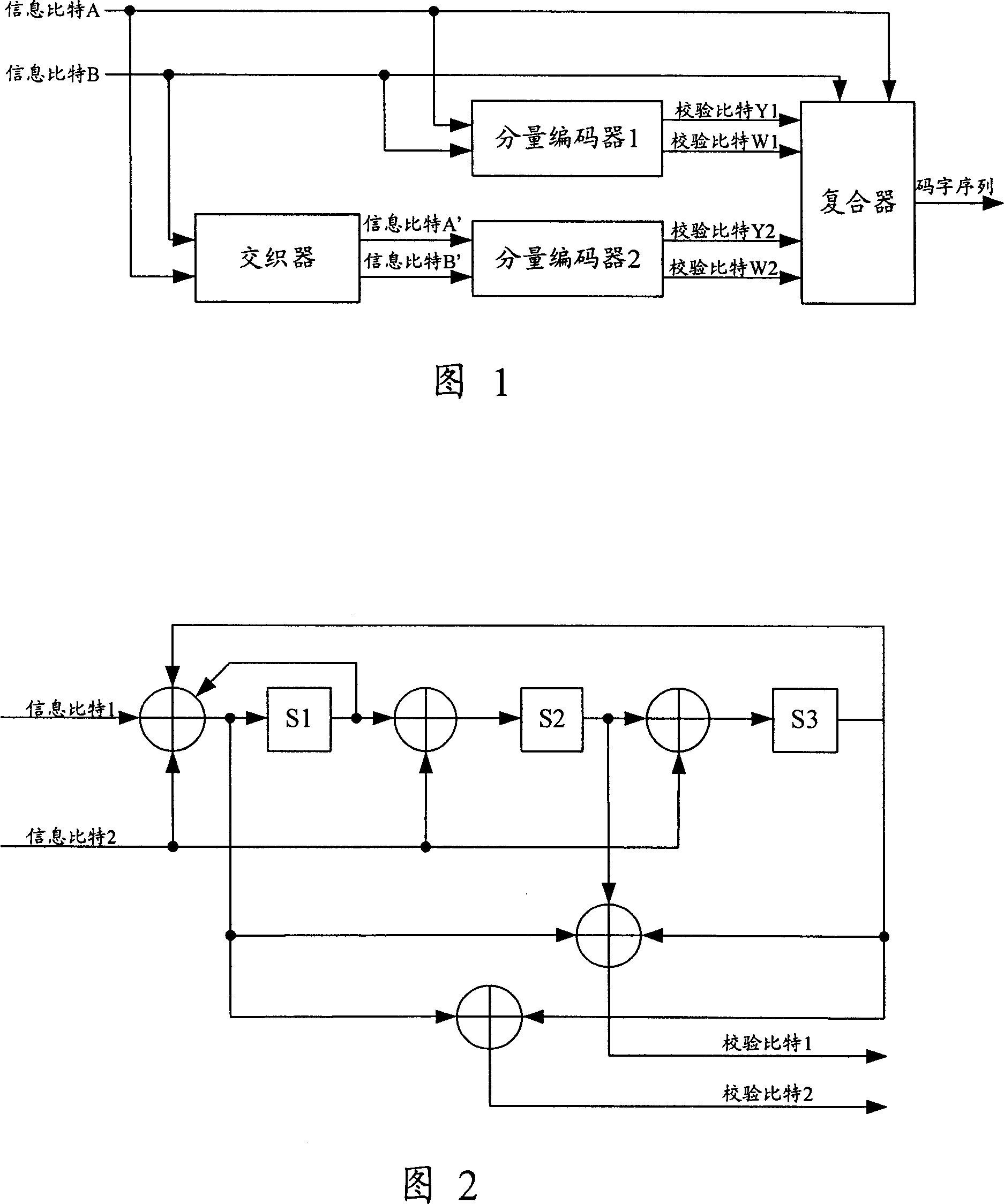

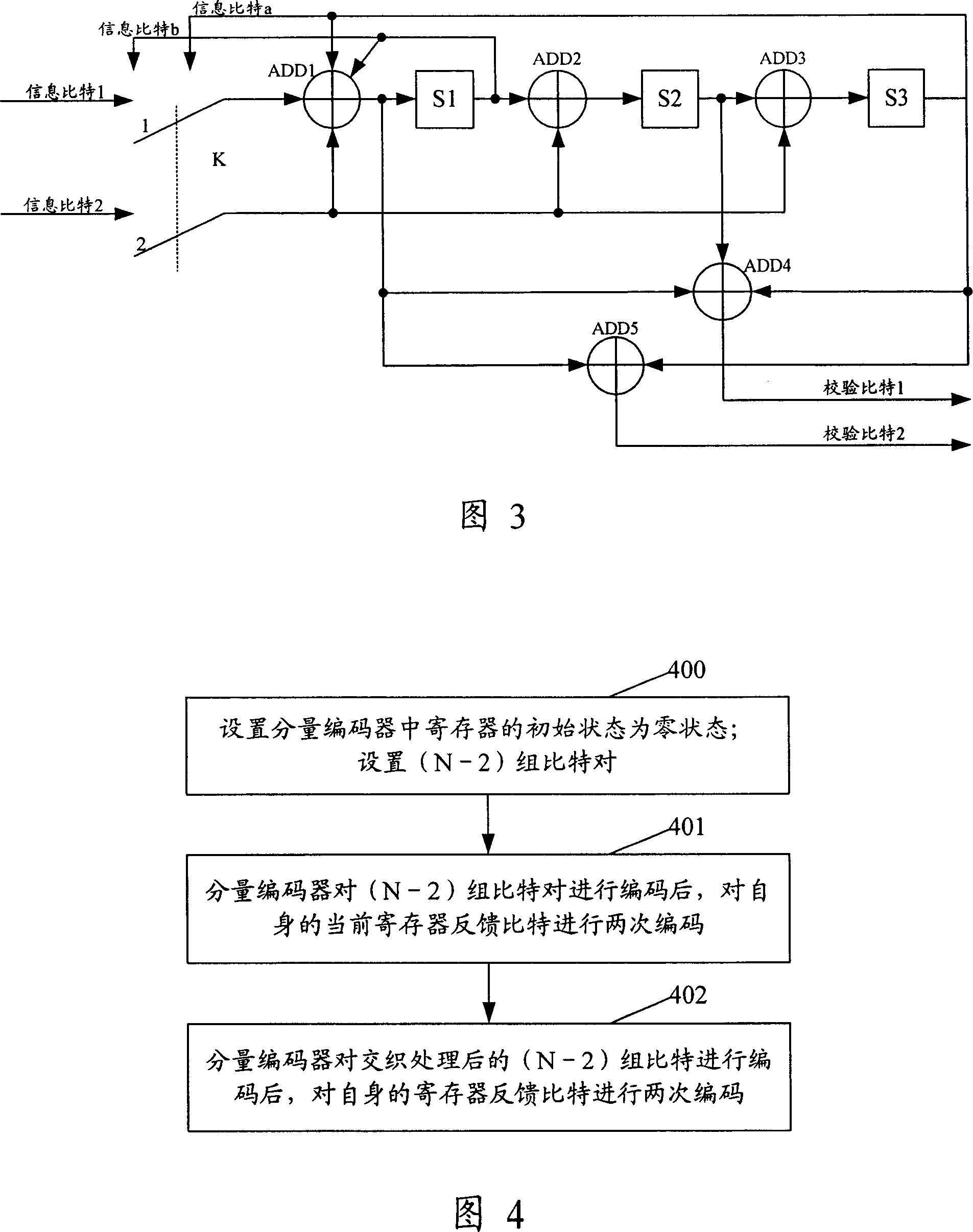

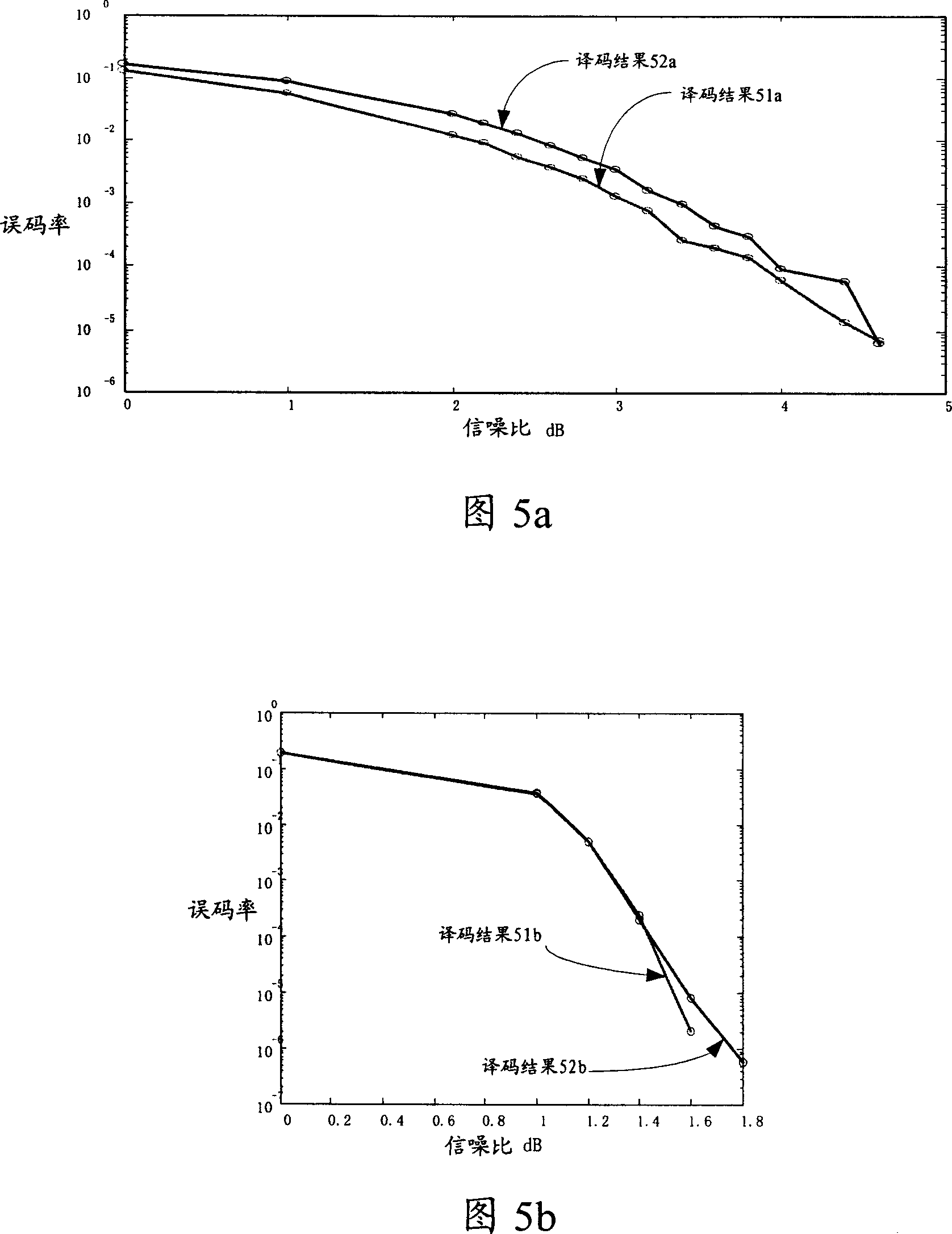

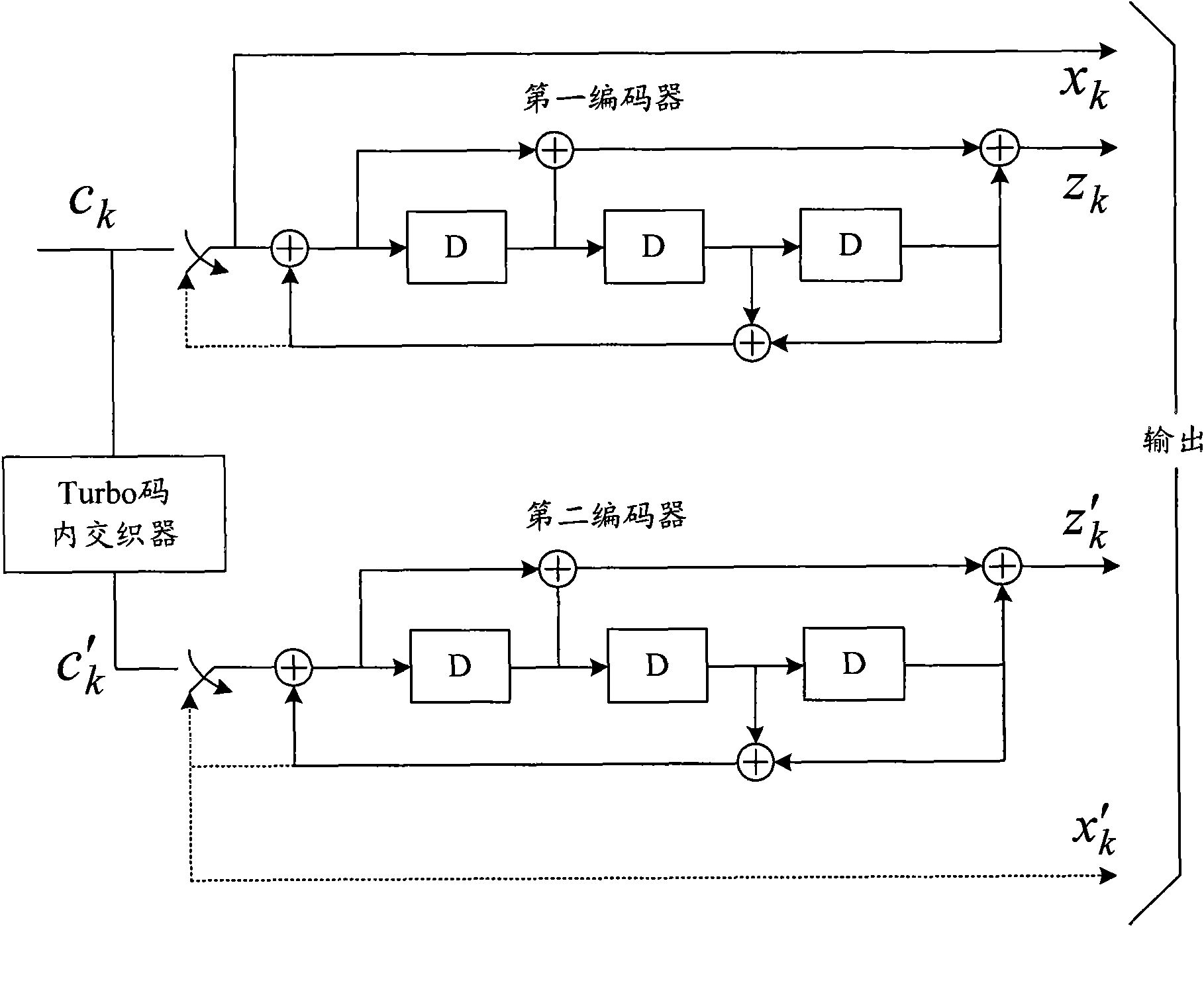

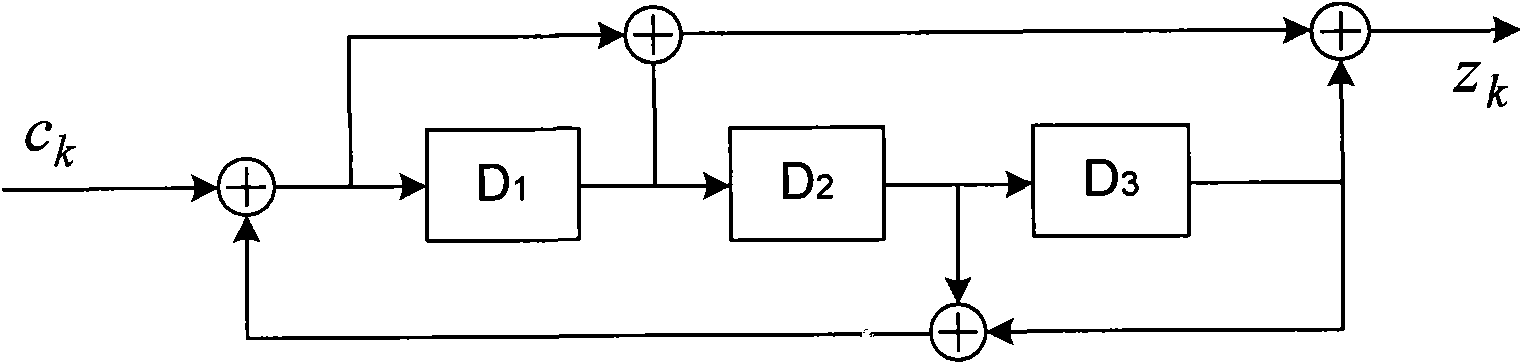

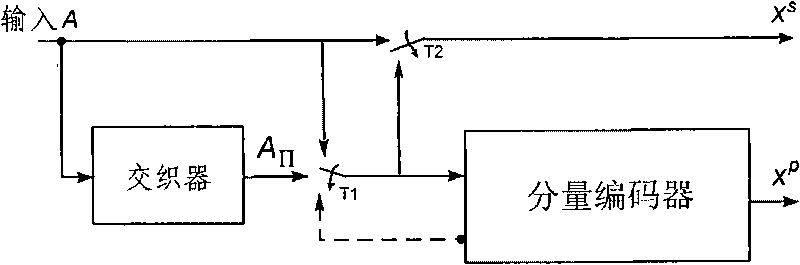

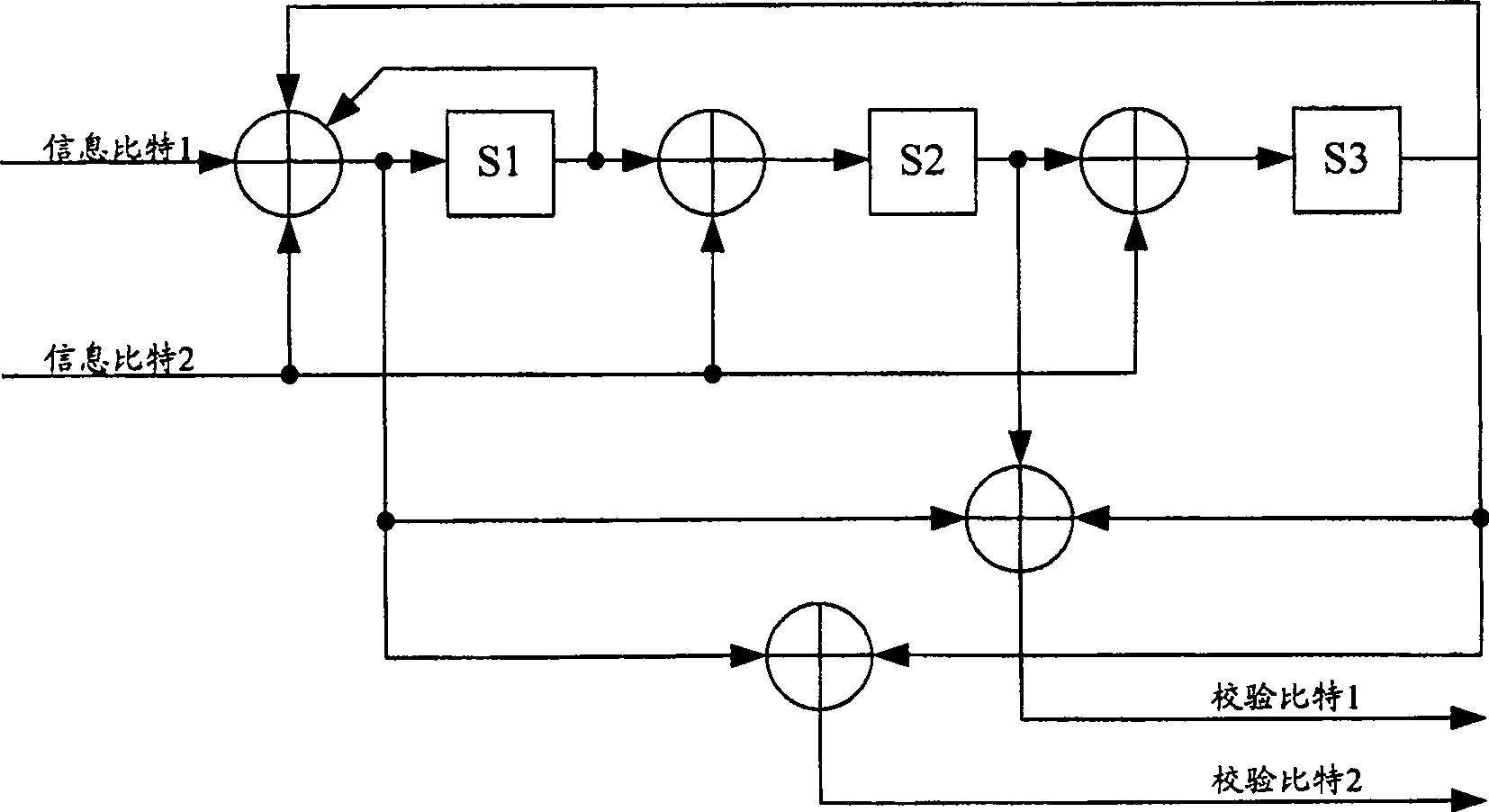

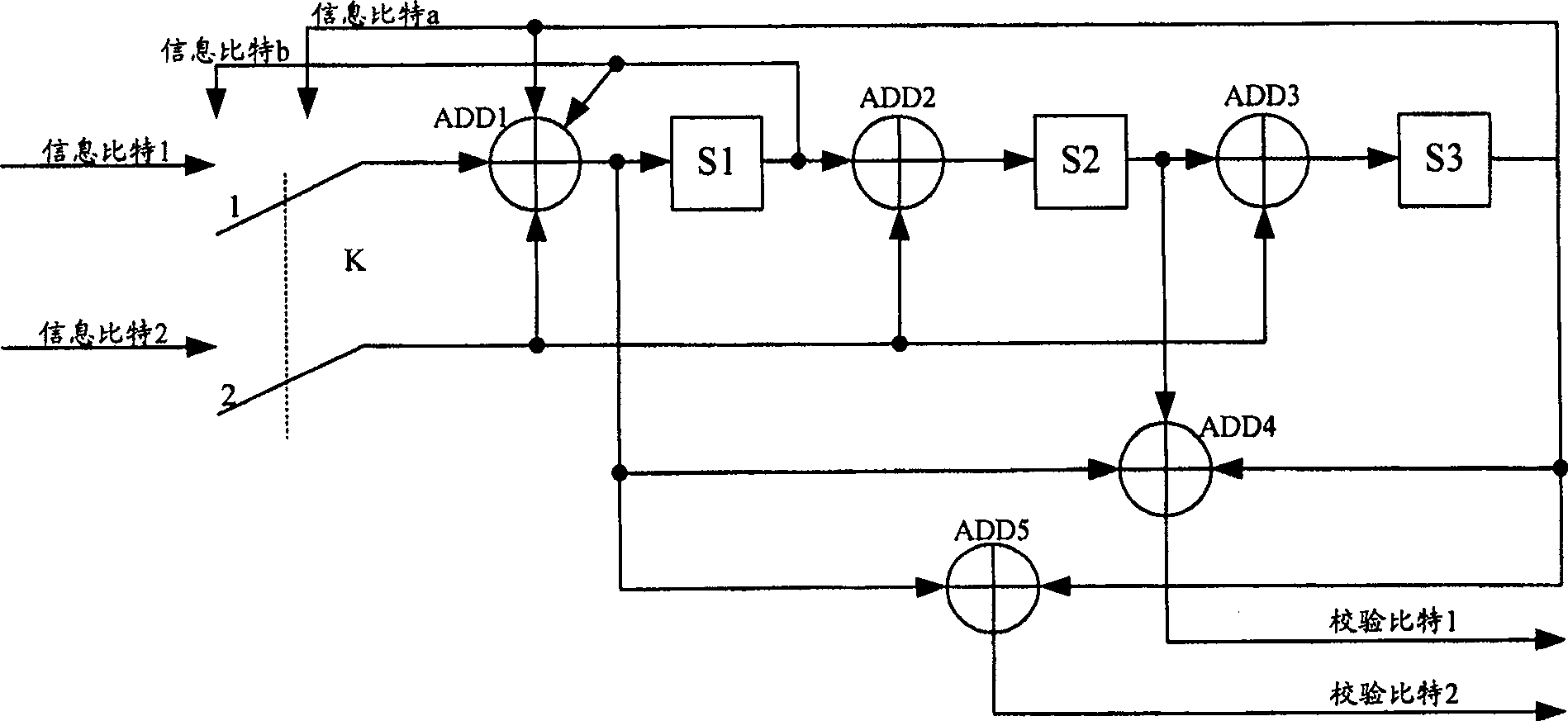

Component coder and coding method, double-output Turbo coder and coding method

InactiveCN1983827AConsistent stateAvoid double encoding processCode conversionError correction/detection by combining multiple code structuresDecoding methodsProcessor register

The invention is concerned with the component encoder and the decoding method, the initial condition set of the register is zero state in the component encoder, the component encoder uses the outputting feedback bit from the self register to decode at the control of the controlling switch after finish the decode for each decoding block, in order to ensure the final condition and the initial condition of the register are consistent after decode. The method is concerned with the double inputting Turbo encoder and the encoding method using the above component encoder. The invention can avoid the two time encoding process in the existing encoder, reduce computation quantity of encode and the coding delay, and reduce the decoding computation quantity of the receiving terminal.

Owner:HUAWEI TECH CO LTD

Method and apparatus for coding bits of data in parallel

InactiveUS6701482B2Reduce encoding delayIncrease delayError correction/detection using convolutional codesError preventionComputer architectureEncoder

A concatenated encoder capable of coding multiple data bits in parallel and including a first (outer) encoder, a memory, and a second (inner) encoder coupled in cascade. The first encoder receives and codes M data bits in parallel in accordance with a first coding scheme to generate MR code bits. The memory receives and stores unpunctured ones of the MR code bits from the first encoder. The second encoder receives and codes N code bits in parallel in accordance with a second coding scheme to generate coded data. M and N can be any values (e.g., M>=8, N>=4). Each encoder can be a (e.g., a rate ½) convolutional encoder that implements a particular polynomial generator, and can be implemented with one or more look-up tables, a state machine, or some other design.

Owner:QUALCOMM INC

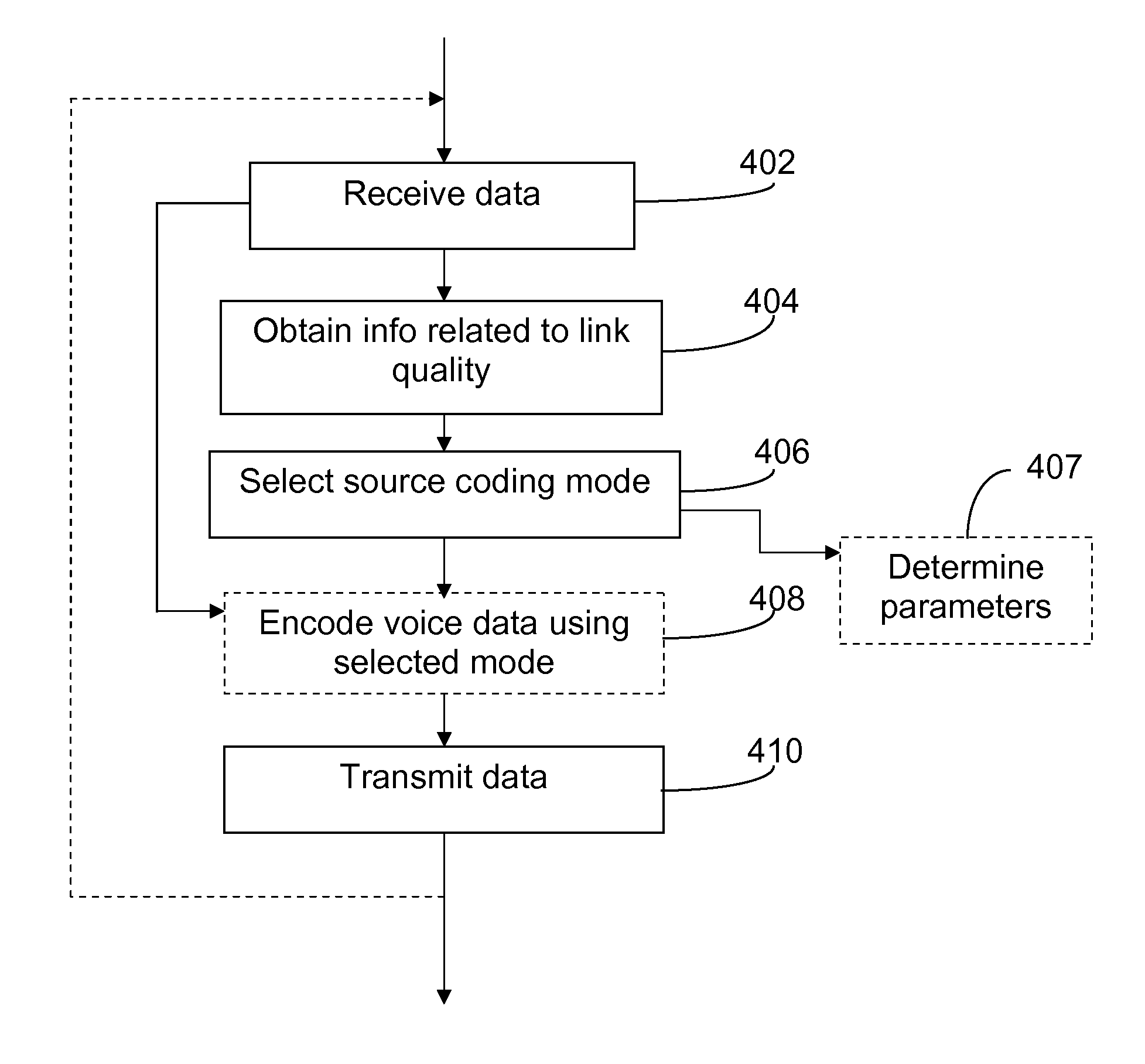

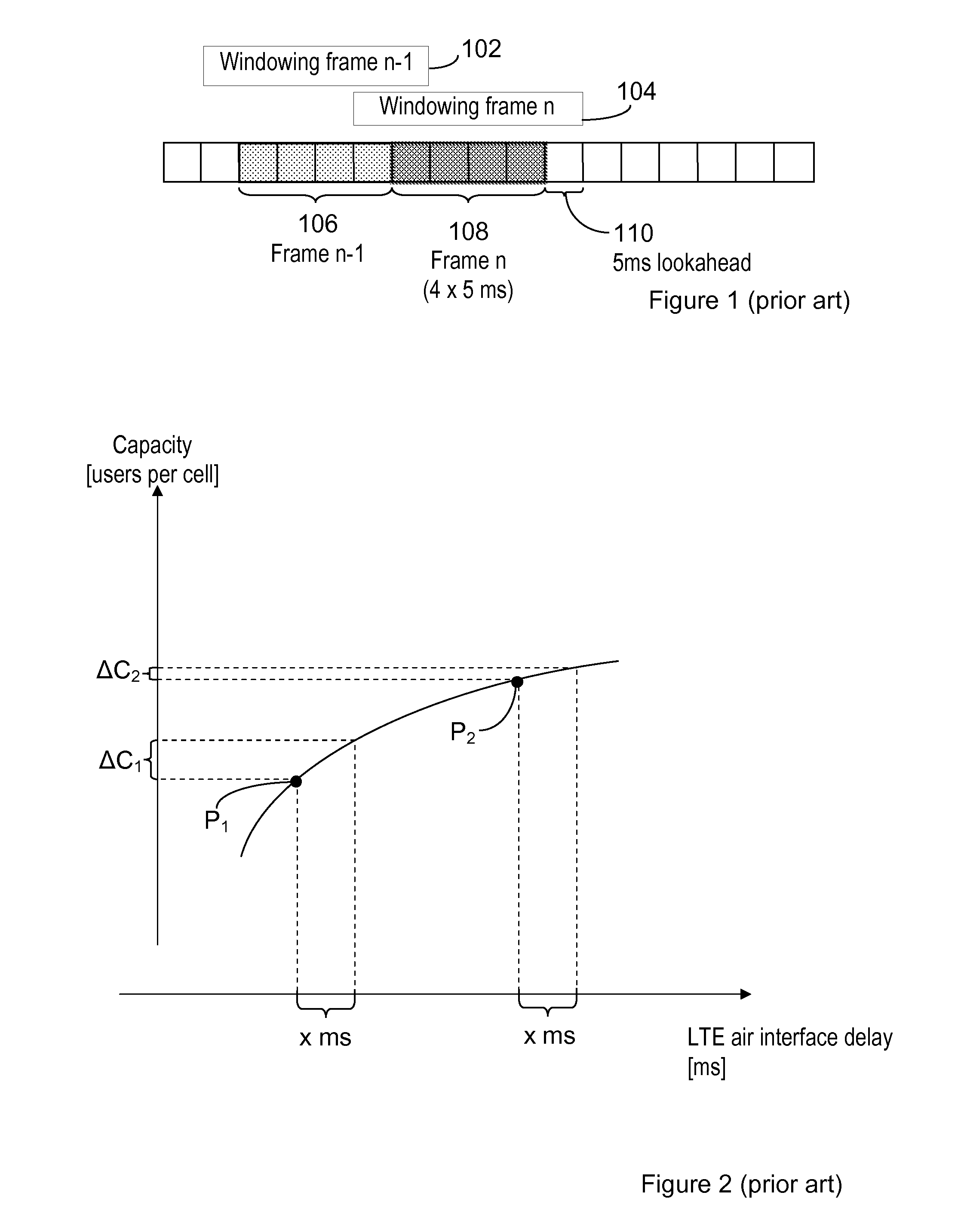

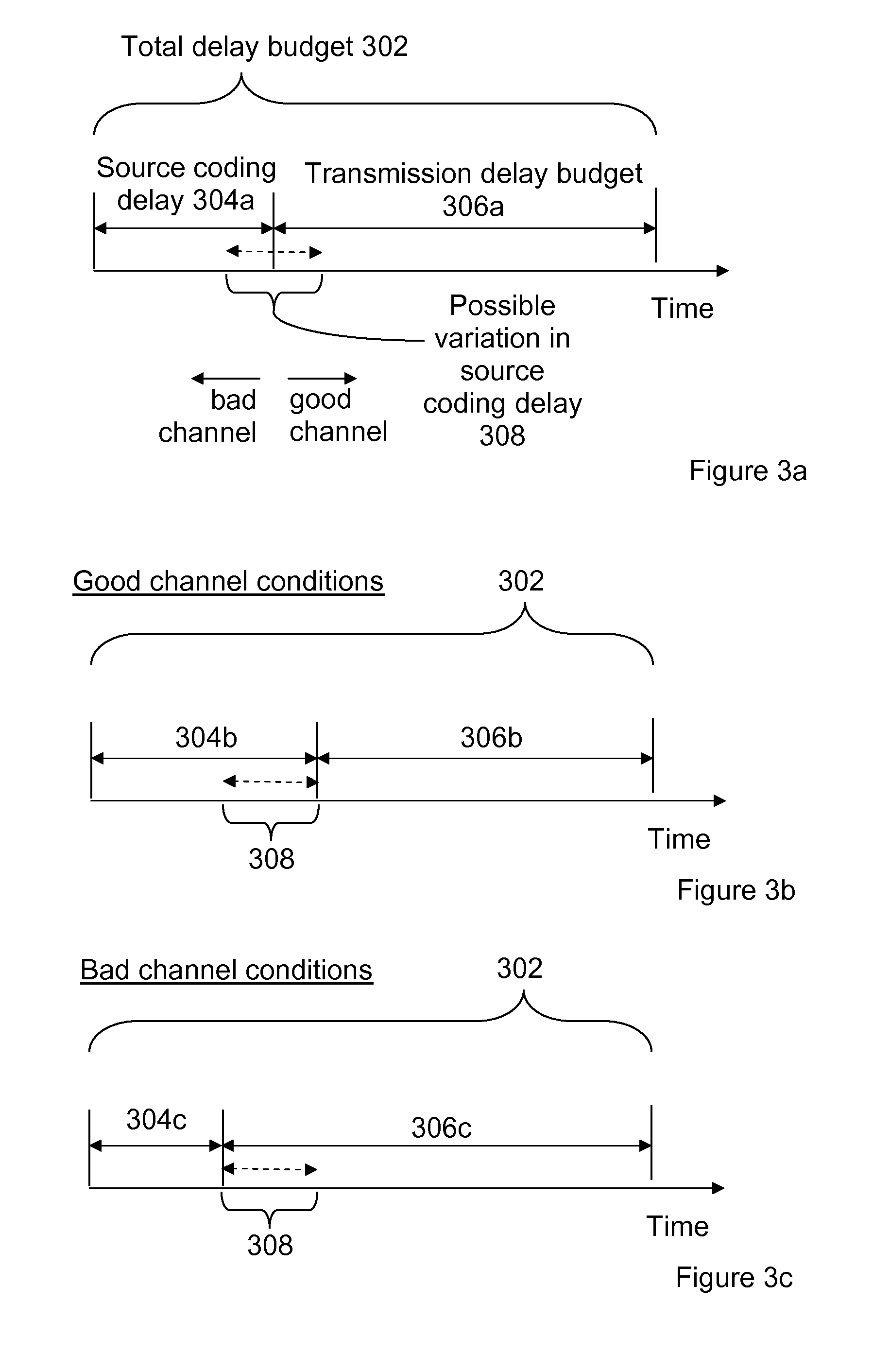

Source Code Adaption Based on Communication Link Quality and Source Coding Delay

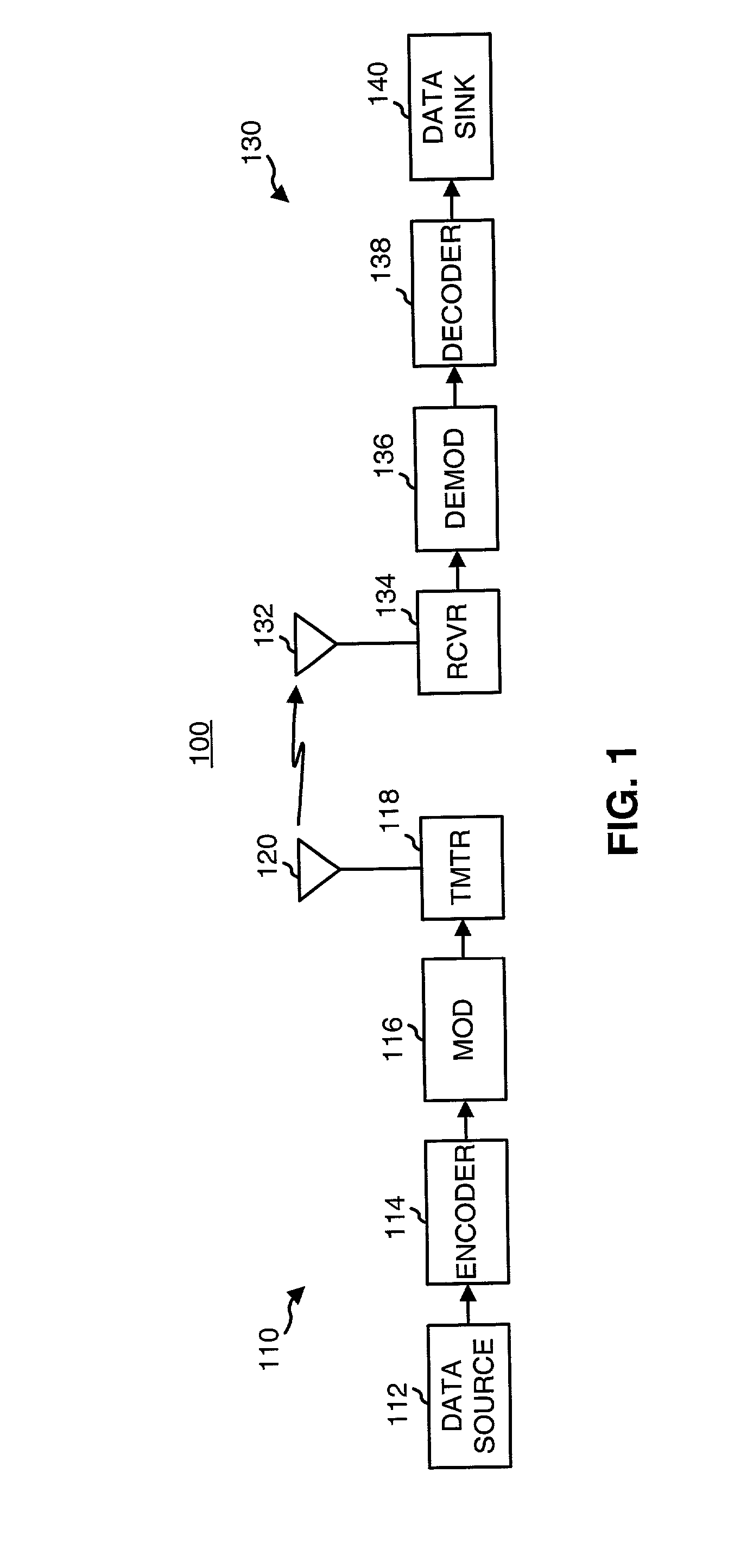

ActiveUS20120323568A1Improve transmission efficiencyImprove transmission capacityInterconnection arrangementsSpeech analysisTelecommunications linkVoice data

Method and arrangement in a network node for adapting a property of source coding to the quality of a communication link in packet switched conversational services in a communication system. The method comprises obtaining (404) information related to the quality of a communication link. The method further comprises selecting (406) a source coding mode with an associated source coding delay, based on the obtained information and the associated source coding delay. The selected source coding mode is selected from a set of at least two source coding modes associated with different source coding delays, and is to be used when source coding voice data to be transmitted over the communication link.

Owner:TELEFON AB LM ERICSSON (PUBL)

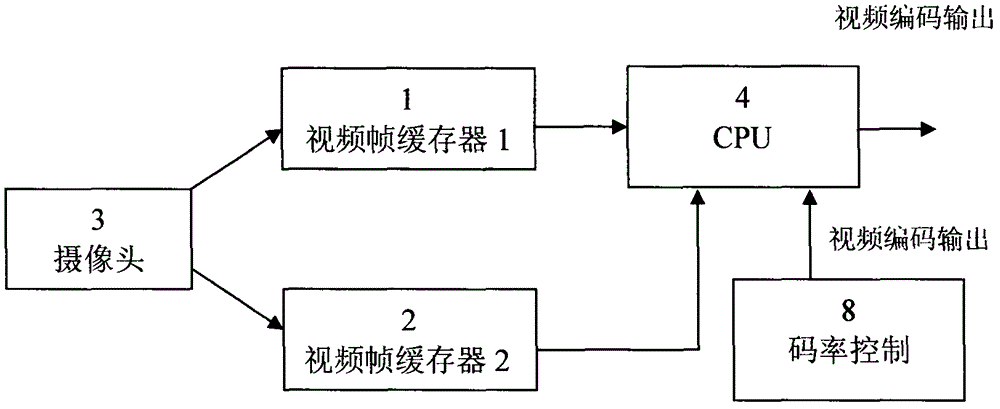

Method for reducing video coding time delay

InactiveCN102724489AReduce encoding delayReduce latencyPulse modulation television signal transmissionDigital video signal modificationReal-time computingComputer hardware

The invention discloses a method for reducing video coding time delay, so as to effectively reduce coding time delay in image video coding. The method comprises steps that: two video frame buffers are placed in handling the video coding, one frame of image data is collected by each video frame buffer in turns, one video frame buffer collects one frame of image data and the other video frame buffer collects the next frame of image data; and when CPU completes the video coding of one frame of image in one video frame buffer, the CPU continues to handle the video coding of the next frame of image in the other video frame buffer and the work is cycled.

Owner:苏州汉辰数字科技有限公司

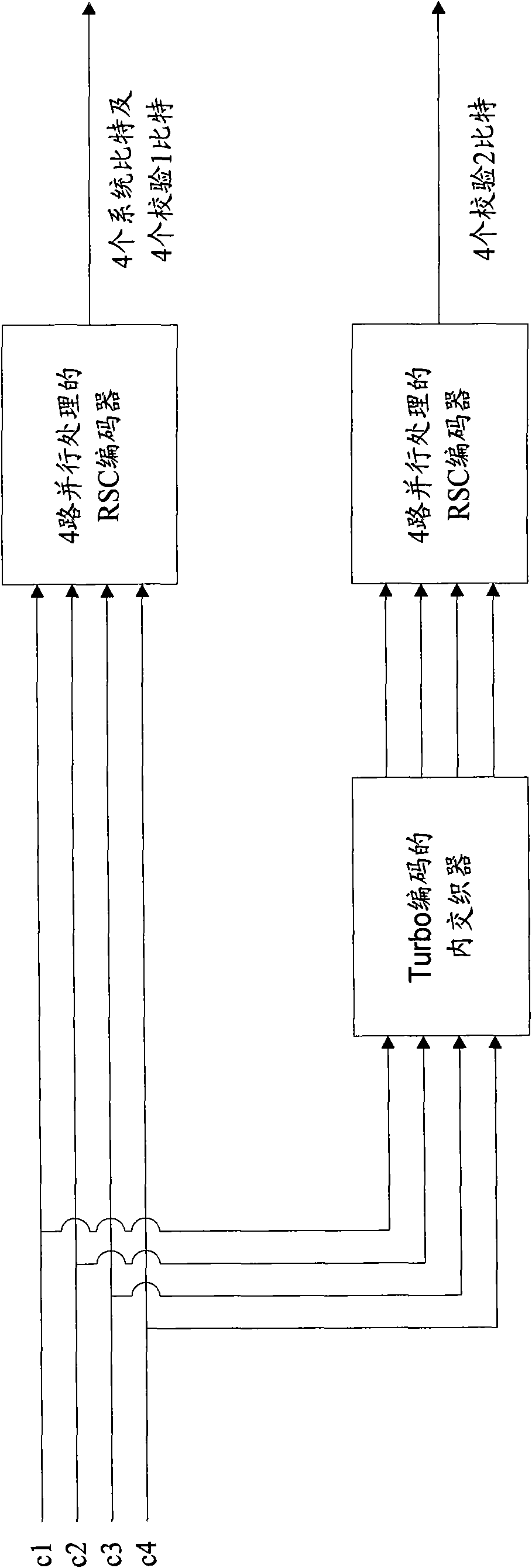

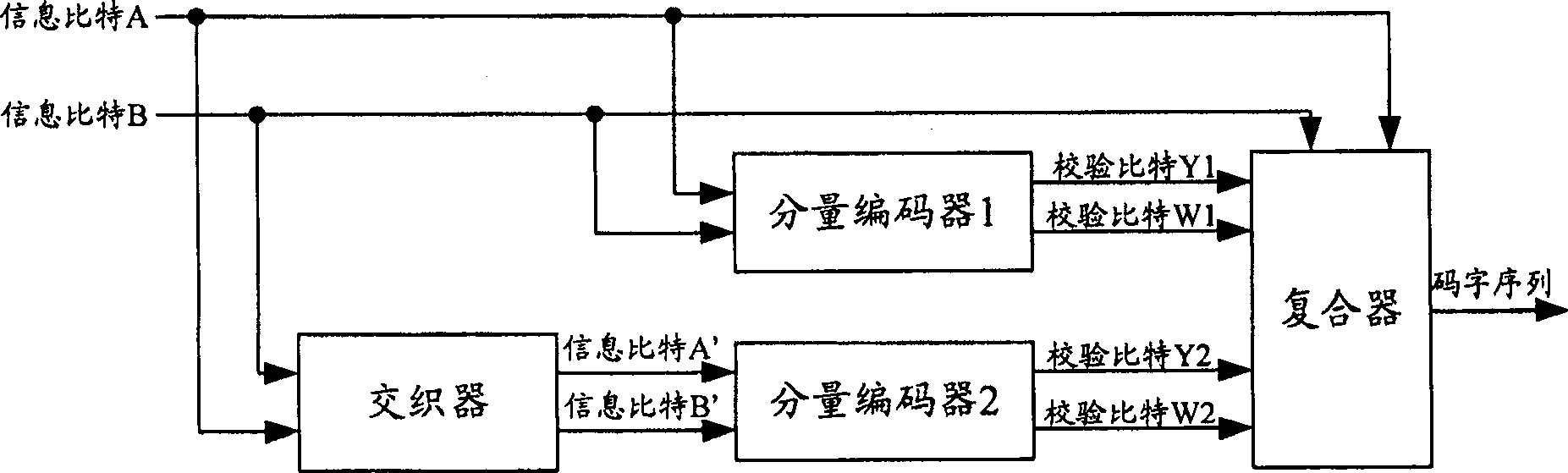

LTE (Long Term Evolution) Turebo encoder parallel processing device and method

ActiveCN101938282AProcessing speedReduce encoding delayError correction/detection using convolutional codesError correction/detection by combining multiple code structuresTurbo encoderParallel processing

The invention provides a data parallel encoded processing device in order to realize the parallel processing of LTE (Long Term Evolution) Turebo encoding. The device comprises a first parallel encoder, an inner interweaver and a second parallel encoder, wherein the first parallel encoder is used for carrying out parallel encoded processing on M bits of input data input from a first path; the inner interweaver is used for carrying out interwoven processing on M bits of data input from a second path parallel to the first path; and the second parallel encoder is used for receiving data subjected to the interwoven processing and carrying out parallel encoded processing on the data subjected to the interwoven processing, wherein M is equal to 2m, m is an integer being larger than 0 and smaller than 13, and the total bits of the input data can be divided by M with no remainder. In addition, the invention also provides a method for carrying out encoded processing on the data in order to realize the parallel processing of the LTE Turebo encoding.

Owner:SANECHIPS TECH CO LTD

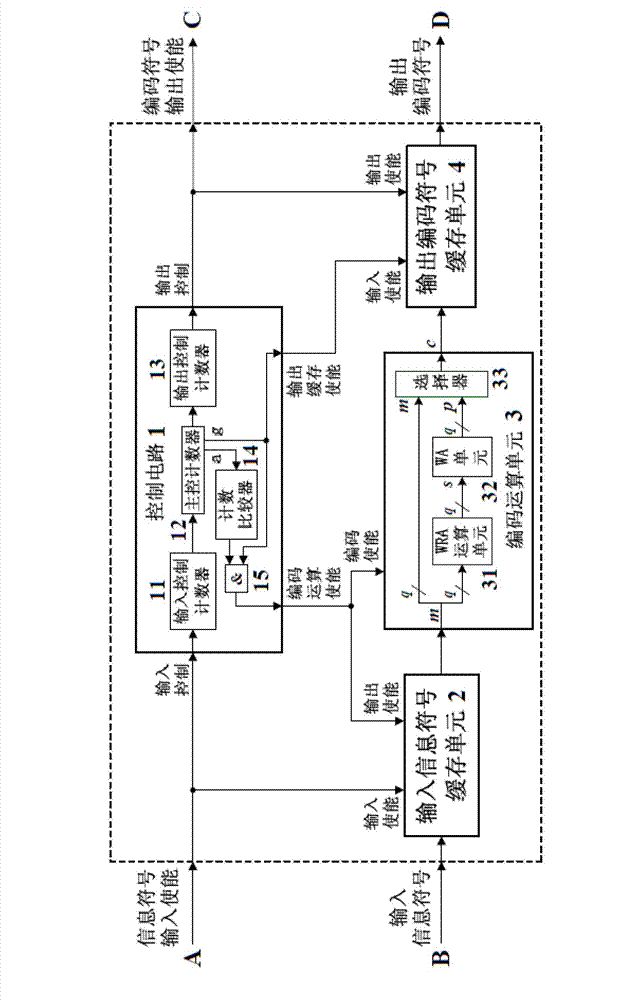

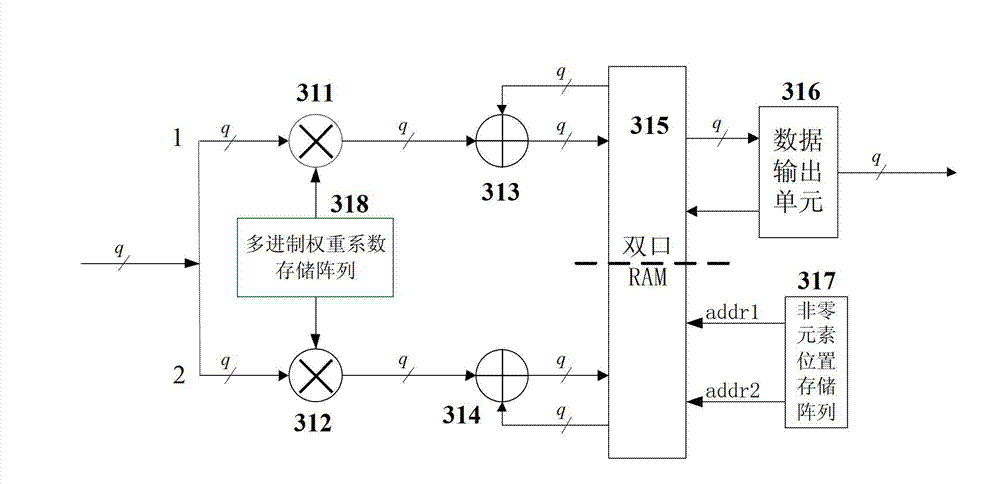

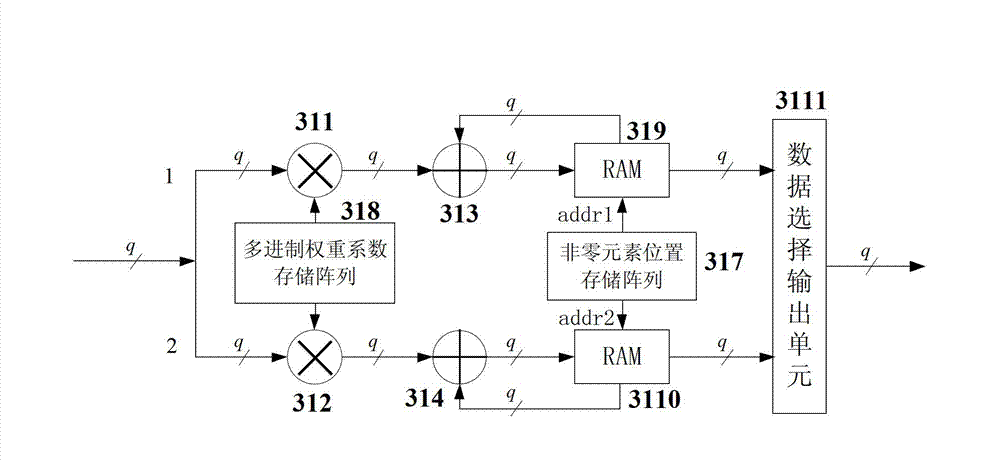

Encoder device and method for short code length multi-system weighted repeat-accumulate code

InactiveCN102820890AReduce coding complexityReduce encoding delayError correction/detection using multiple parity bitsCommunications systemComputer architecture

The invention discloses an encoder device for a short code length multi-system weighted repeat-accumulate code. The device comprises an input information symbol cache unit, a coding arithmetic unit and an output code symbol cache unit which are connected with a control circuit respectively, the control circuit comprises an input control counter, a master control counter and an output control counter which are sequentially connected, a counting signal a output by the master control counter is connected with logic and gate though a counting comparator, a gate signal g output by the master control counter is respectively connected with the logic and gate and the output code symbol cache unit, output of the logic and gate is connected with the input information symbol cache unit and the coding arithmetic unit, output of the output control counter is connected with the output code symbol cache unit, the coding arithmetic unit comprises a weighted repeat-accumulate arithmetic unit, a weighted accumulating unit and a selector which are sequentially connected, and the selector is directly connected with a signal input end of the coding arithmetic unit. According to the encoder device for the short code length multi-system weighted repeat-accumulate code, the complexity and coding delay have a linear relation with the code length, the achieving mode is simple, and the device is convenient to apply to the communication system.

Owner:TIANJIN UNIV

Encoding and decoding methods for shortening Turbo product code

InactiveCN101958720BIncrease storage resourcesImprove data throughputError correction/detection by combining multiple code structuresParallel encodingTheoretical computer science

The invention relates to encoding and decoding methods for shortening a Turbo product code. The encoding method comprises the following steps of: performing row or column encoding on an information sequence to be encoded; performing parallel encoding on code words of row or column component codes generated by the row or column encoding; and judging whether the encoding is finished. The decoding method comprises the following steps of: generating a hard decision sequence of a soft-input information sequence; selecting the least reliable bits in the soft-input information sequence; generating a test sequence according to the hard decision sequence and the least reliable bits; decoding the test sequence to generate candidate code words; calculating the measurement of the candidate code words and the soft-input information sequence; reducing the number of the candidate code words; determining decision code words according to the measurement of the candidate code words; and calculating external information of each code element in the decision code words. The encoding method has the advantages of improving data throughput and reducing encoding delay; and the decoding method has the advantages of saving a mass of logical resources and storage resources, particularly well balancing decoding complexity and data throughput under the condition of longer code length of component codes.

Owner:XIDIAN UNIV

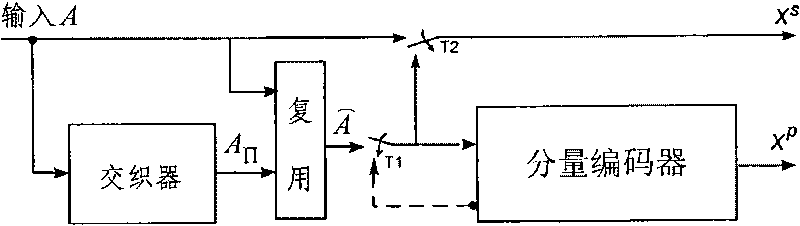

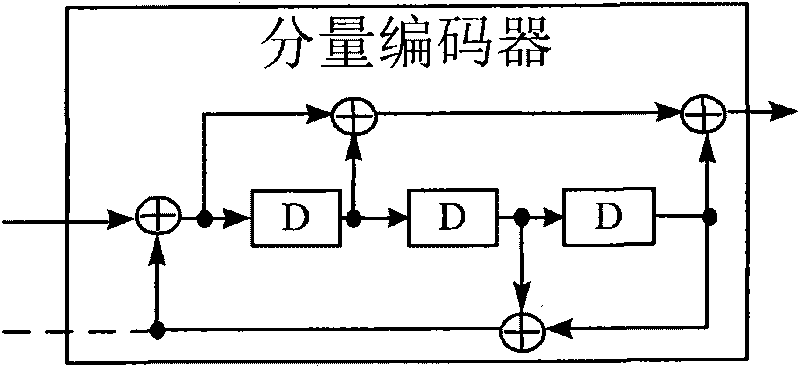

Turbo code encoder, decoder, encoding method and decoding method

ActiveCN101753153AReduce complexityReduce processing latencyError correction/detection by combining multiple code structuresTurbo codedComputer engineering

The invention discloses a Turbo code encoder and an encoding method. The Turbo code encoder comprises an interleaver and a component encoder. After the component encoder encodes the input information sequences, bits fed back by the component encoder are encoded and are distributed to the last place of information bit and the last place of check bit and the bits are output. Since the encoder adopts only one component encoder and the number of tail bits is reduced, the encoding processing delay is effectively reduced, the encoding complexity is simplified and the encoding speed and the rate matching speed are improved. The invention additionally discloses a decoder and a decoding method. By adopting the technical scheme, the invention has the advantages that the encoding and decoding complexity and the processing delay are reduced, and encoding speed and decoding speed are improved.

Owner:DATANG MOBILE COMM EQUIP CO LTD

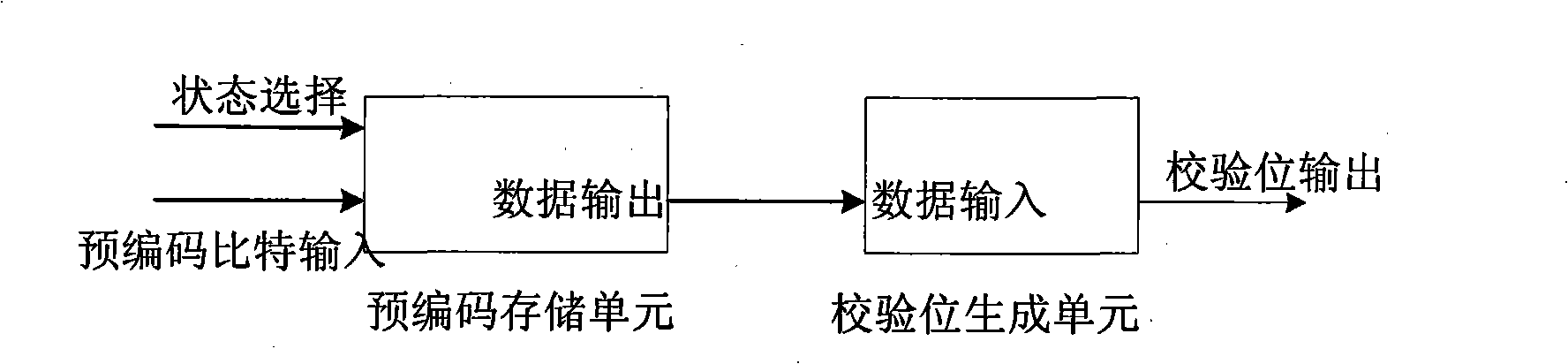

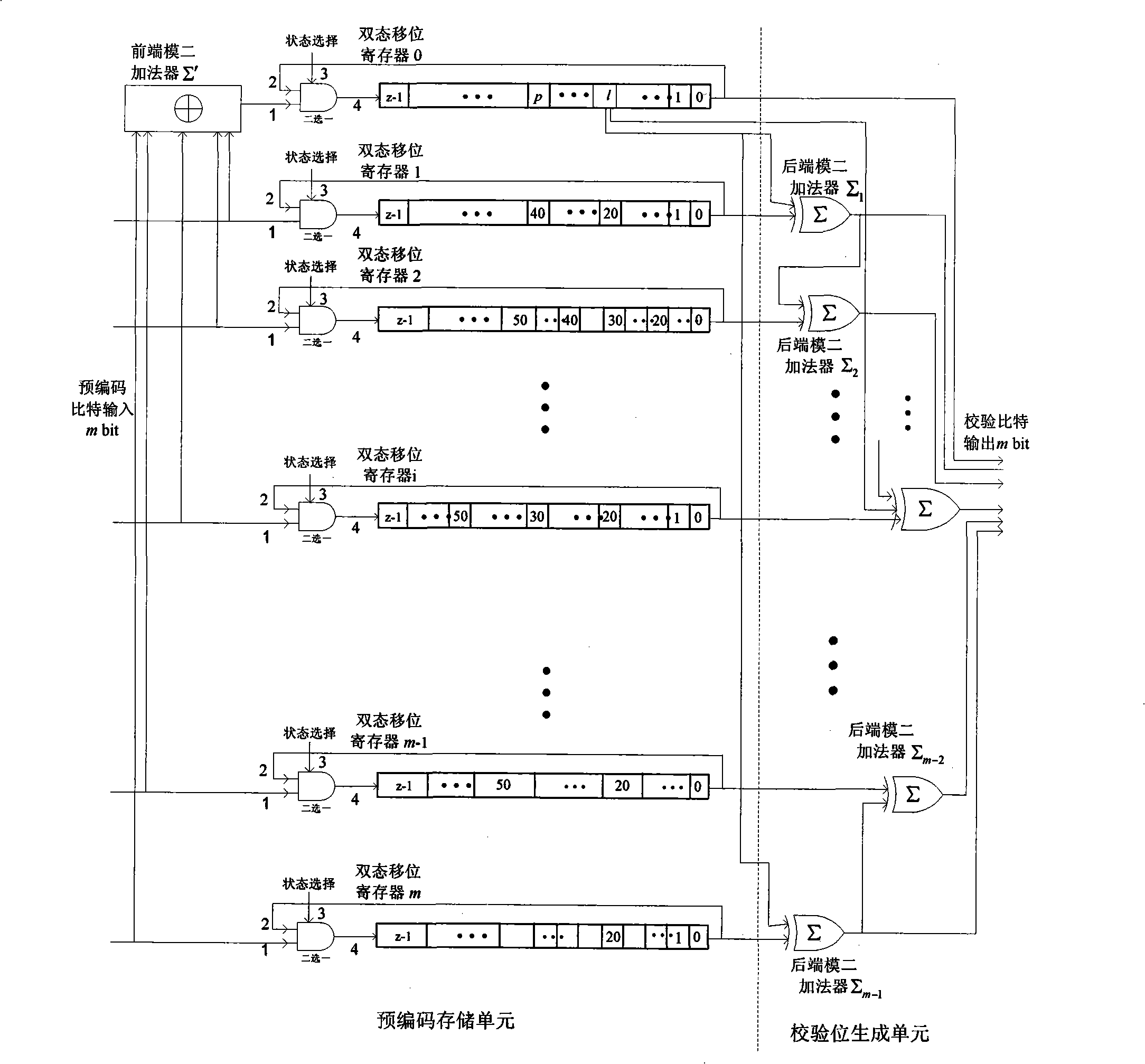

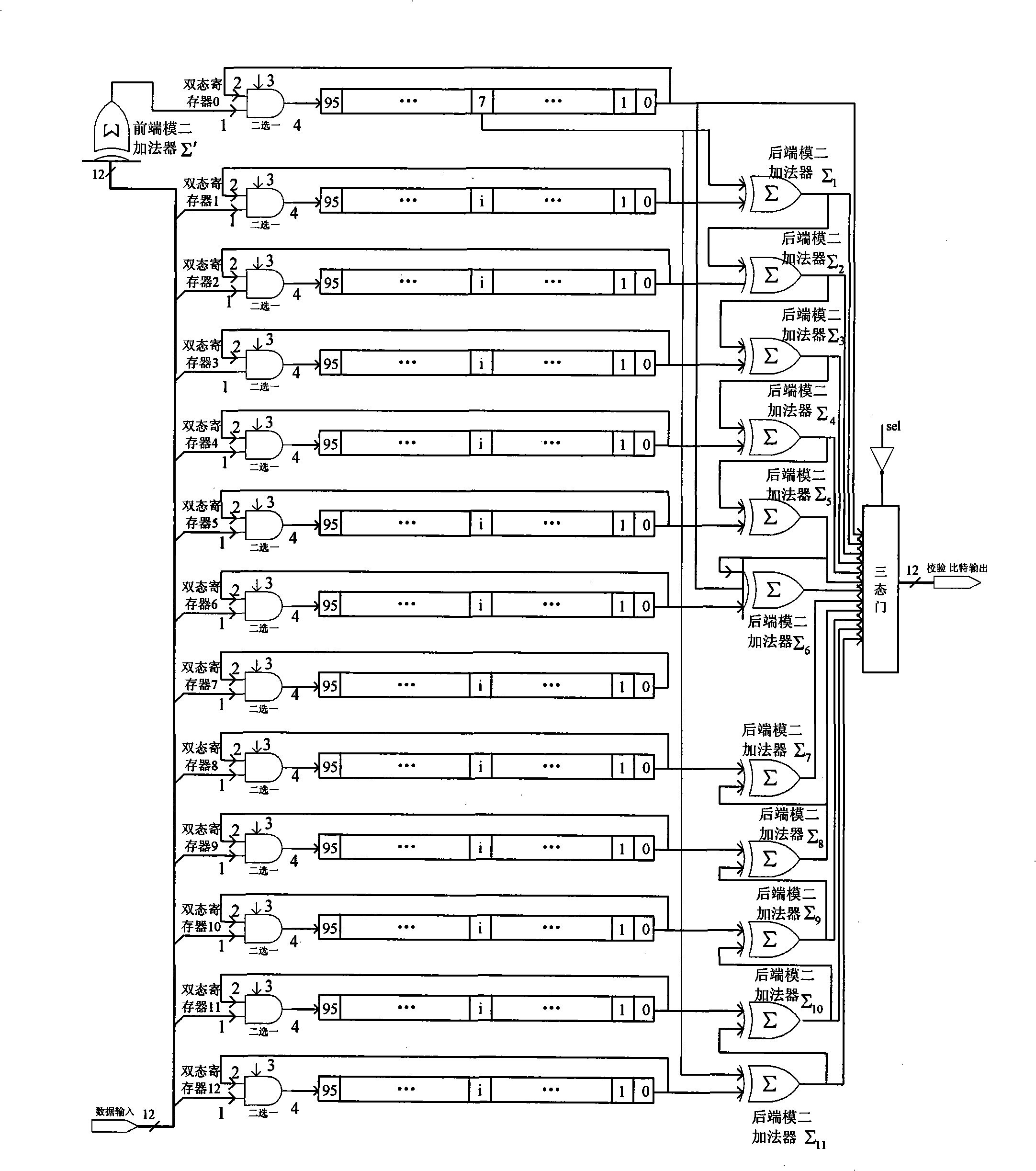

Generator for check bit of quasi-cyclic shift low-density check code base on bi-diagonal

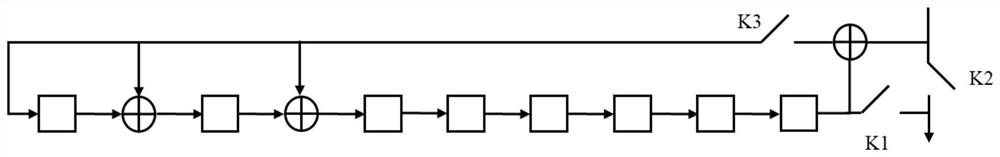

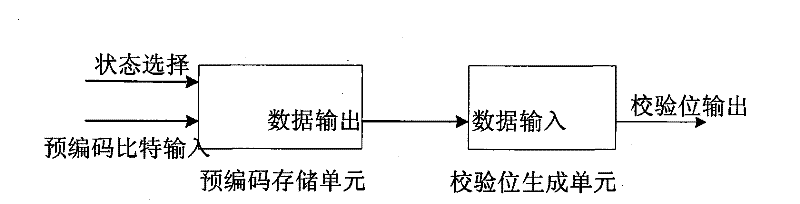

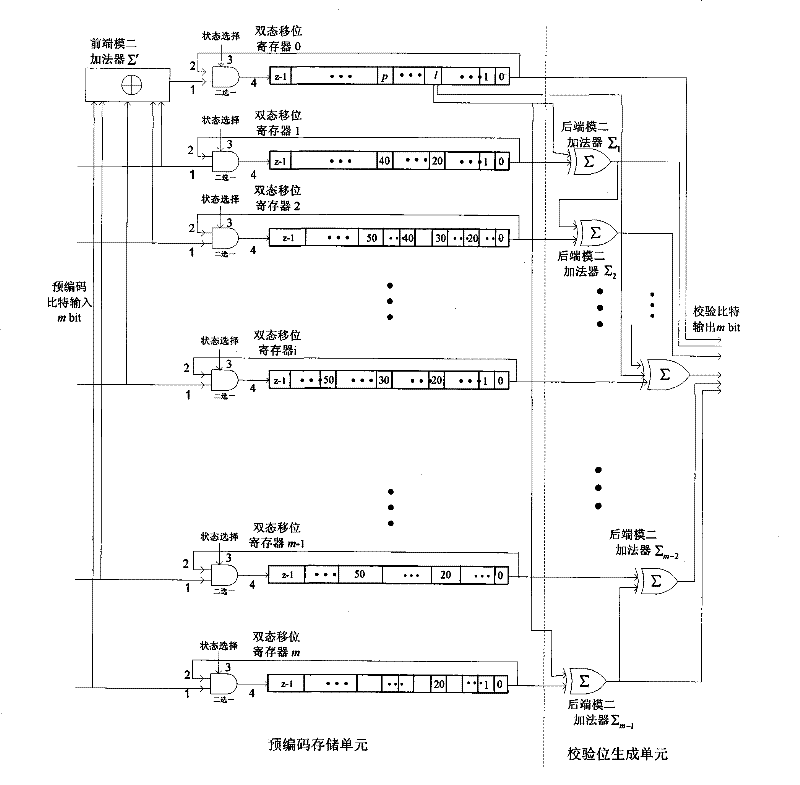

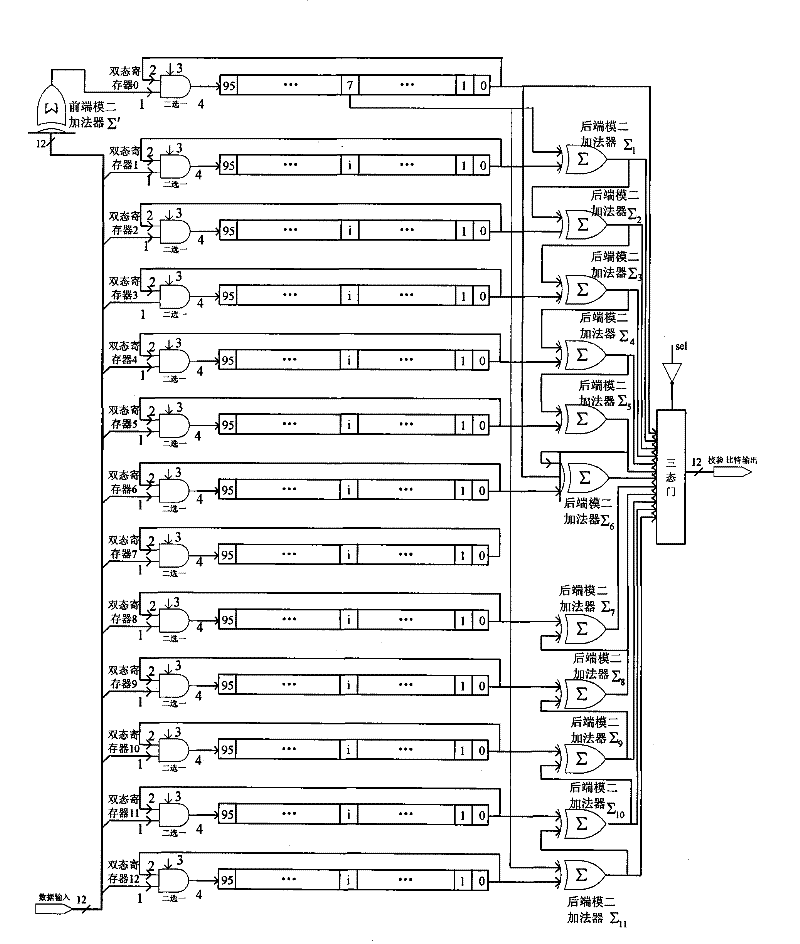

InactiveCN101409562AImprove throughputReduce encoding delayError preventionError correction/detection using multiple parity bitsPrecodingShift register

The invention discloses a check bit generator based on bidiagonal quasi-cyclic shift check code with low density, and relates to coding devices; the check bit generator mainly solves the problem of high complexity and long coding time in the existing encoder. The check bit generator comprises a precoding memory location and a check bit generation unit, wherein, the precoding memory location is used for storing precoded data, and includes a front-end modular two adder sigma' and a plurality of parallel two-state shift registers; each of the two-state shift registers is formed by sequentially connecting an either-or selector and a plurality of D triggers; the check bit generation unit is used for generating check bit which is composed of m-1 back-end modular two adders sigma. The data output by the precoding memory location is transmitted to the check bit generation unit, and the check bit is output by the check bit generation unit. The check bit generator has the advantages of simple structure and high coding efficiency, and can be used as the device of an LDPC encoder.

Owner:XIDIAN UNIV

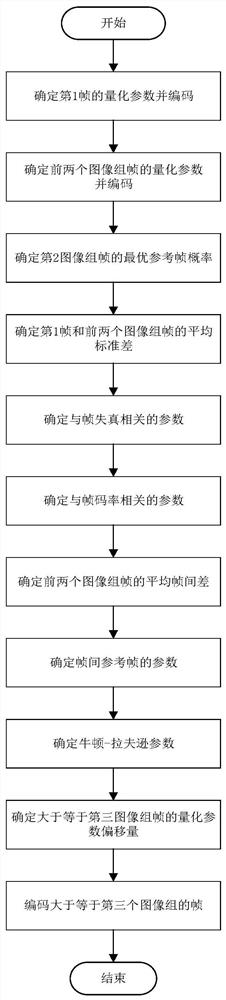

Monitoring video-oriented high-efficiency video coding standard quantization parameter cascading method

ActiveCN112218078ATroubleshooting Coding DependenciesSimple calculationDigital video signal modificationVideo encodingRate distortion

The invention discloses a monitoring video-oriented high-efficiency video coding standard quantization parameter cascading method. The method comprises the steps: determining and encoding quantizationparameters of a first frame, determining and encoding quantization parameters of first two image frames, determining an optimal reference frame probability of a second image frame, determining an average standard deviation between the first frame and the first two image frames, determining parameters related to frame distortion, determining parameters related to a frame code rate, determining anaverage inter-frame difference of the first two image frames, determining parameters of an inter-frame reference frame, determining Newton-Raphson parameters, determining a quantization parameter offset greater than or equal to a quantization parameter offset of a third image frame, and encoding a frame greater than or equal to the third image frame. The method solves the problems that in the prior art, coding dependence between video frames is not comprehensively considered, model parameter acquisition in the prior art is complex, and the method is not suitable for monitoring video coding. The method has the advantages of high coding rate distortion performance, simple model parameter calculation, small coding time delay and the like, and can be applied to the technical field of monitoring video coding.

Owner:XIAN UNIV OF POSTS & TELECOMM

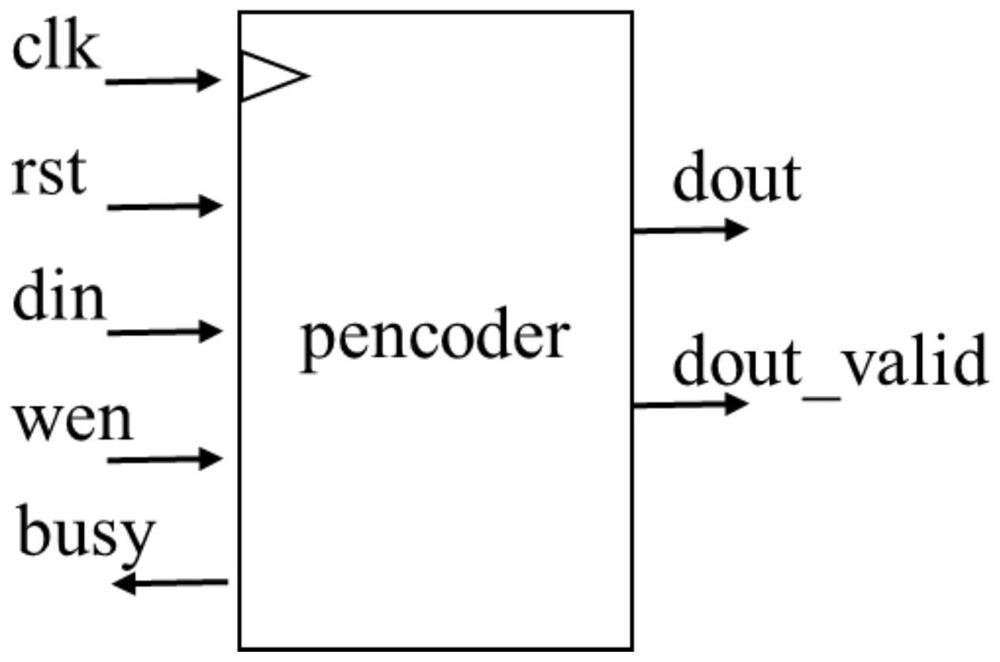

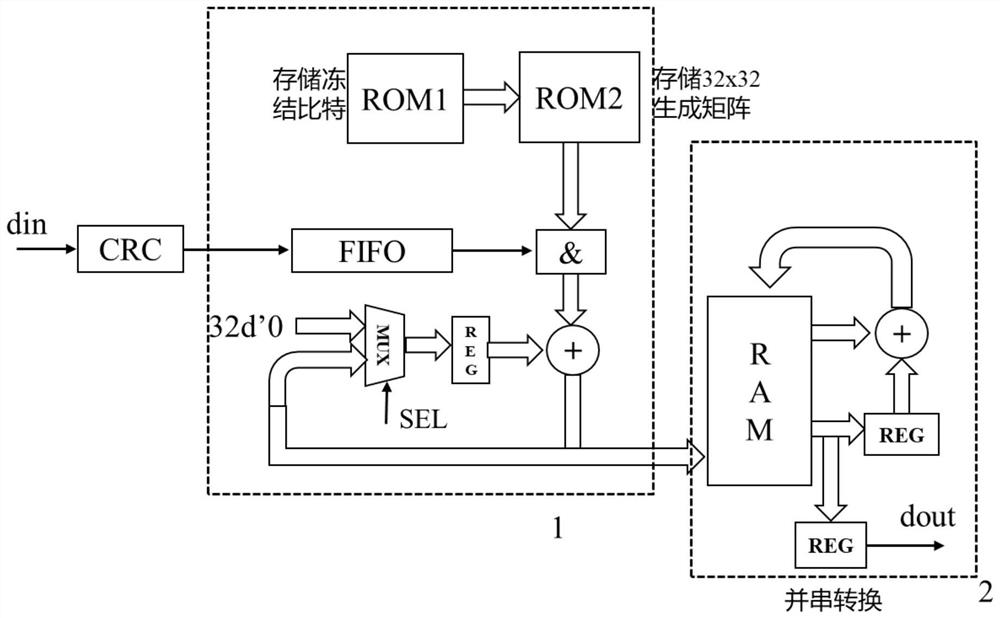

High-performance polarization encoding method and encoder for satellite discontinuous communication

ActiveCN111900999ASave resourcesReduce encoding delaySingle error correctionHigh level techniquesComputer hardwareCoding block

The invention discloses a high-performance polarization encoding method and encoder for satellite discontinuous communication, and the method comprises the steps: S1, dividing a polarization code freezing bit and an information bit into a plurality of code blocks, carrying out the polarization encoding of each code block, storing the information bit in an ROM1, and storing the polarization encoding in an ROM2; S2, addressing the ROM2 by utilizing the position information of the information bits stored in the ROM1; s3, performing bitwise exclusive OR on a result obtained by performing bitwise exclusive OR on a certain row output by the ROM1 and the data read from the FIFO at the moment and a data result stored in the register REG, and storing an obtained numerical value back to the registerREG; and S4, writing an encoding result in the step S3 into an RAM, and starting polarization encoding of the next group of code lengths after the REG of the register is reset. And in the second part, XOR operation is carried out on the code block coded in the first part according to the butterfly graph. FPGA hardware resources consumed by the encoder are extremely low; the encoding time delay ofthe encoder is extremely low; the encoder throughput rate is high.

Owner:BEIHANG UNIV

IEEE802.11n LDPC (Low Density Parity Check) encoding system and method as well as LDPC encoder

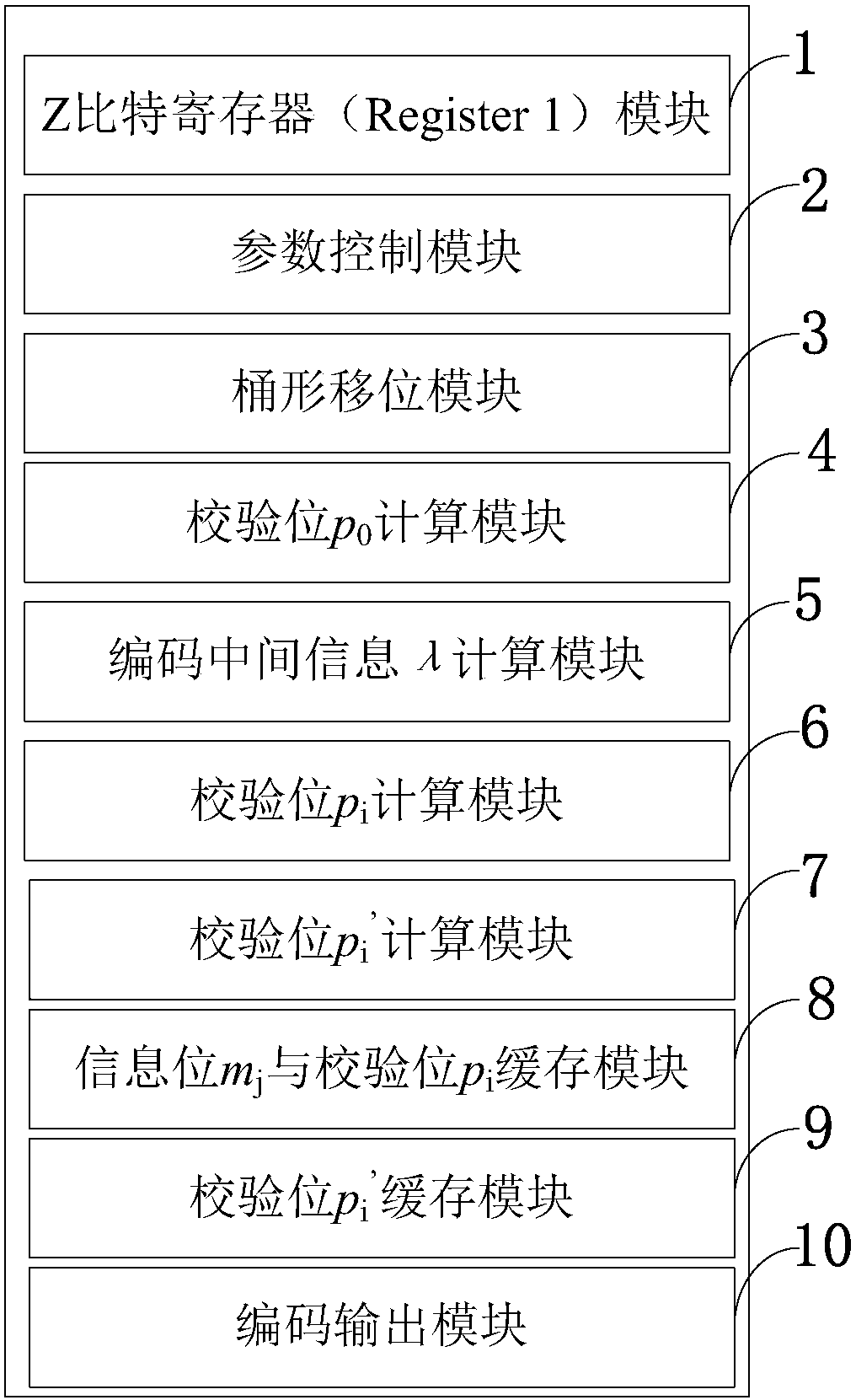

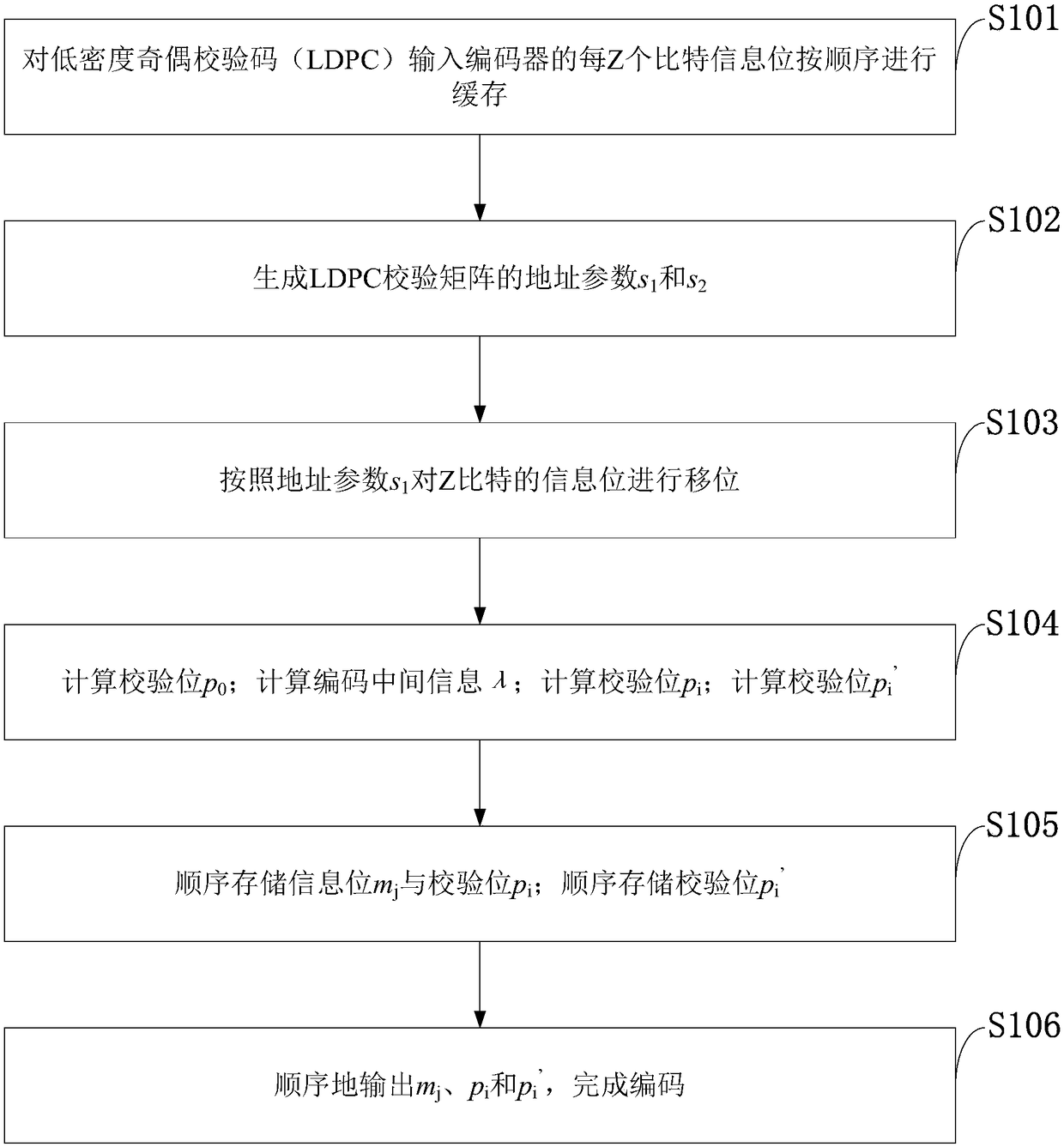

ActiveCN108566210AIncrease consumptionReduce encoding delayError preventionError correction/detection using multiple parity bitsParallel encodingEncoding algorithm

The invention belongs to the technical field of redundant term error detection or forward error correction for data expression, and discloses an IEEE802.11n LDPC (Low Density Parity Check) encoding system and method. The system comprises a Z-bit register module, a parameter control module, a barrel-shaped displacement module, a check bit p0 calculation module, an encoded middle information lambdacalculation module, a check bit pi calculation module, a check bit pi' calculation module, an information bit mj and check bit pi cache module, a check bit pi' cache module and a code output module. By adding of a dual-input xor summator and a register, parallel encoding of two paths of an encoder can be achieved, and the encoding time delay of an LDPC encoder is substantially shortened, so that increase of the throughput rate is realized. According to the IEEE802.11n LDPC encoding system, by use of the parallel calculation idea, a little hardware resource consumption is increased, but the throughput rate of the encoder is substantially increased. The used encoding algorithm is low in complexity, high in throughput and suitable for hardware implementation.

Owner:XIDIAN UNIV

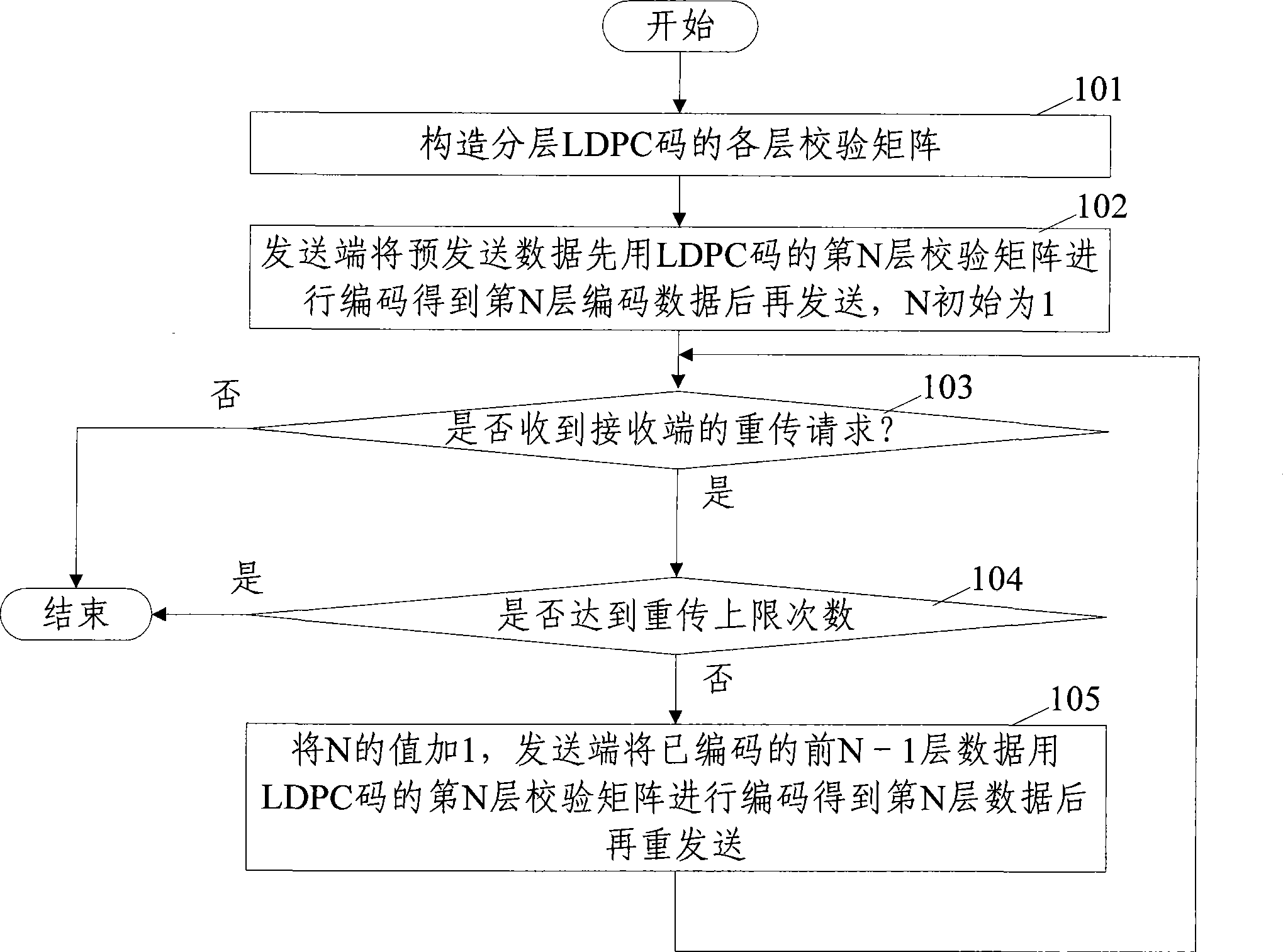

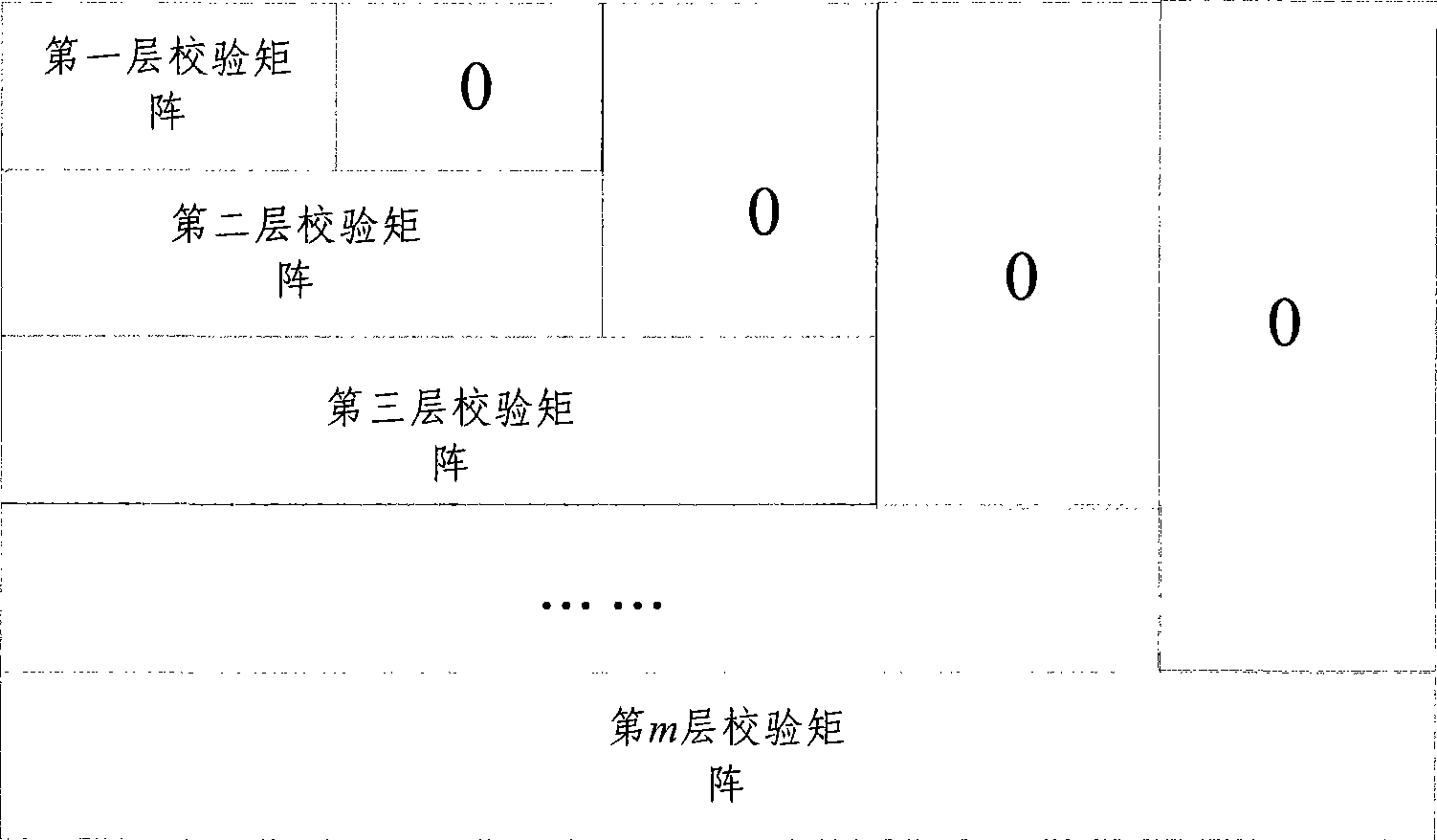

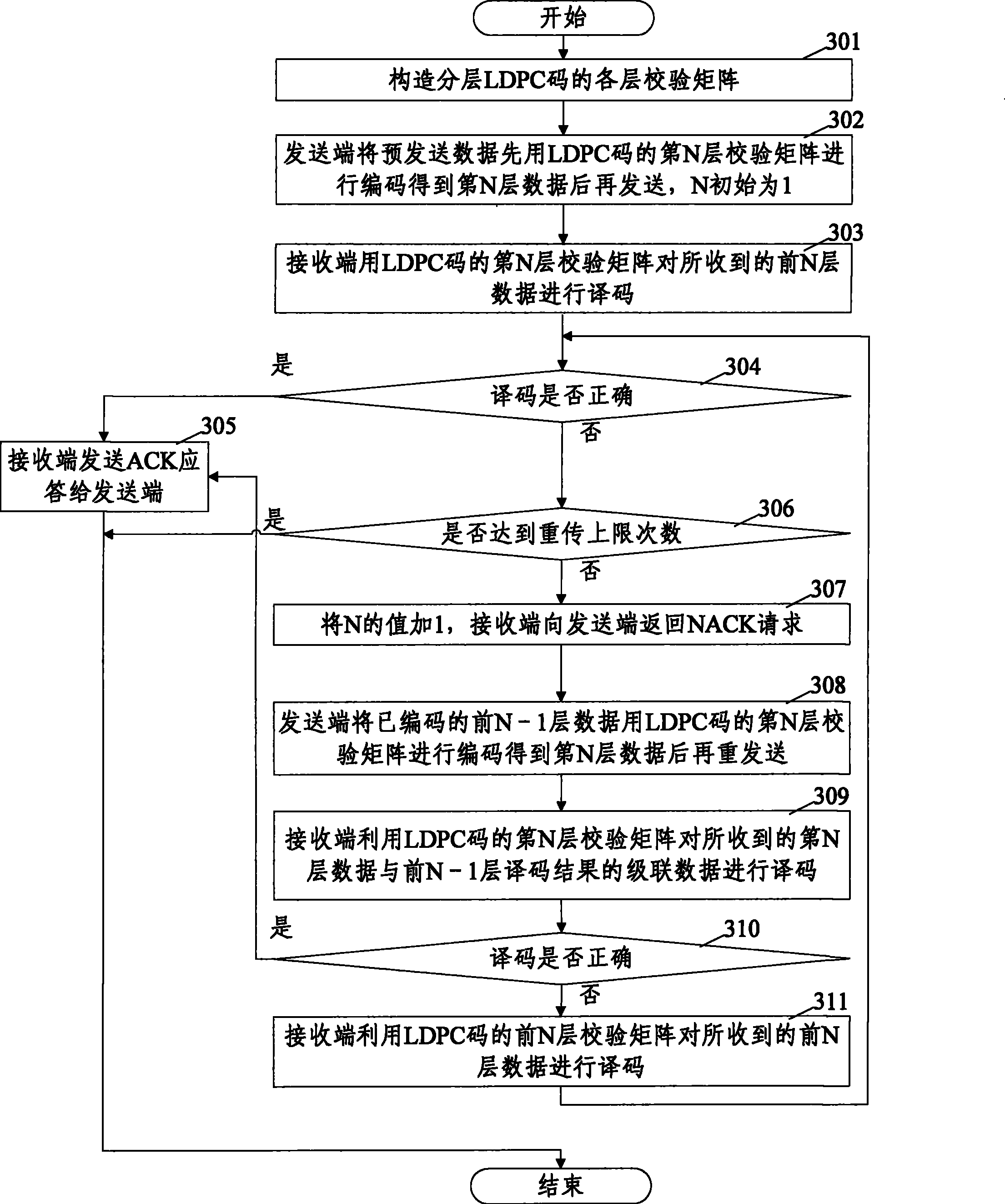

Encoding method and encoding apparatus based on mixed automatic retransmission communication

ActiveCN101321044BFlexible structureLow costError prevention/detection by using return channelCode conversionData operationsStructural unit

The invention discloses a coding method based on the hybrid automatic retransmission (HARQ) communication, according to the method, the layering LDPC code is used as the error correcting code, and the layering LDPC code is used to perform the layering coding on the received data at the data transmitting end. The invention also discloses a coding device based on the hybrid automatic retransmission communication, comprising an error correcting code structural unit, for structuring each layer of check matrix of the layering LDPC code, and using the layering LDPC code as the error correcting code. The device also includes a code unit arranged at the data transmitting end, for performing the layering code on the received data through the layering LDPC code structured by the error correcting code structural unit. According to the method and the device, the cost of the system is reduced, the coding delay is shortened, the coding performance is advanced, which is applicable for the high speed data operation.

Owner:DATANG MOBILE COMM EQUIP CO LTD

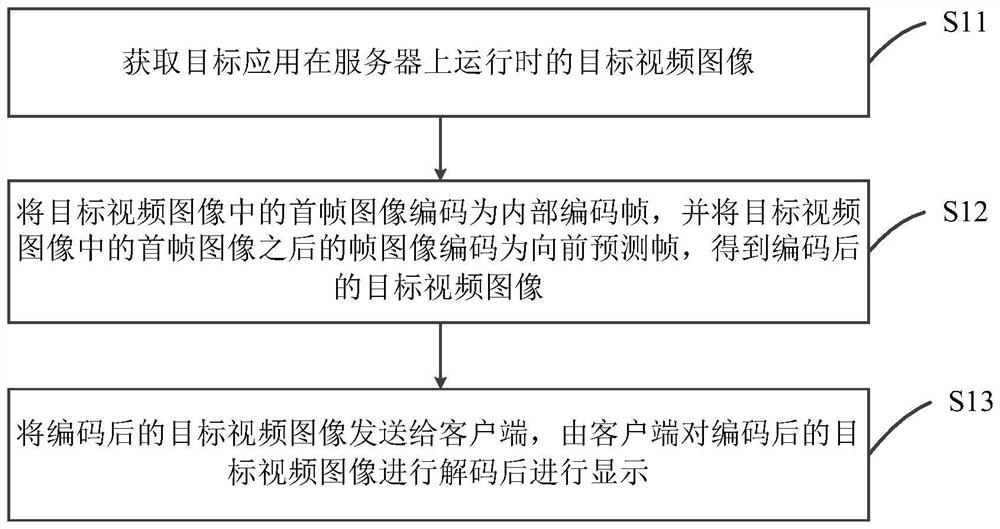

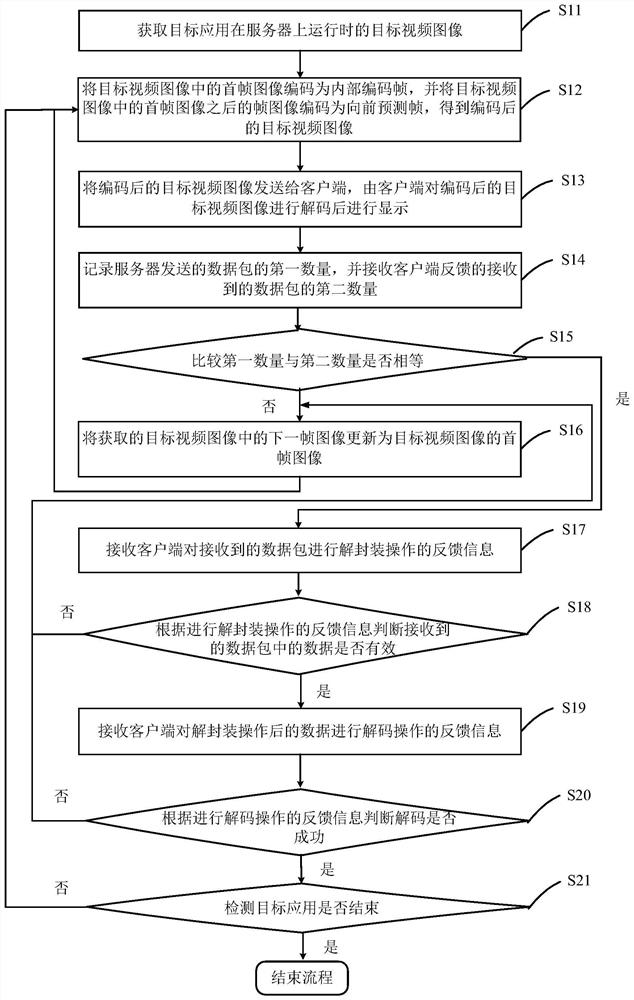

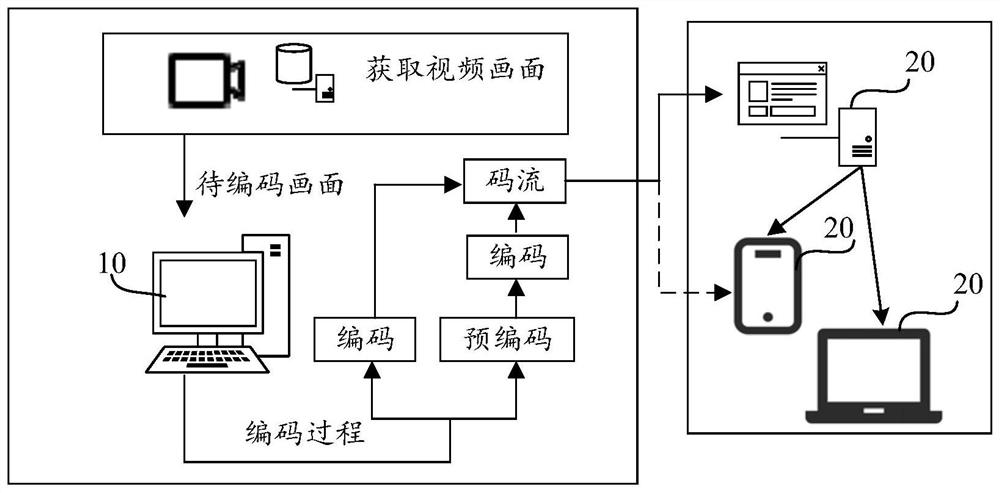

Video image processing method and device and server

PendingCN113794903AReduce data volumeReduce encoding delaySelective content distributionCloud computingComputer graphics (images)

An embodiment of the invention provides a video image processing method and device and a server, and relates to the technical field of cloud computing. The video image processing method is characterized in that a server encodes a first frame image in a target video image into an internal encoding frame and encodes frame images after the first frame image in the target video image into forward prediction frames, and the internal encoding frame and the forward prediction frames form the encoded target video image. On one hand, only the first frame image is coded into the internal encoding frame, so that the number of the internal encoding frames after encoding can be reduced, and the data volume of the target video image after encoding is further reduced; and on the other hand, the frame images after the first frame image are all coded into the forward prediction frames, and the bidirectional interpolation frames are not encoded, so that the encoding delay can be reduced during encoding. Therefore, the network requirement threshold of a client for using a cloud application can be reduced, and good cloud service can be obtained even under the condition that the real-time network speed is lower than the current cloud application requirement.

Owner:GUANGZHOU HUYA TECH CO LTD

Component coder and coding method, double-output Turbo coder and coding method

InactiveCN100488059CConsistent stateAvoid double encoding processCode conversionError correction/detection by combining multiple code structuresDecoding methodsProcessor register

The invention is concerned with the component encoder and the decoding method, the initial condition set of the register is zero state in the component encoder, the component encoder uses the outputting feedback bit from the self register to decode at the control of the controlling switch after finish the decode for each decoding block, in order to ensure the final condition and the initial condition of the register are consistent after decode. The method is concerned with the double inputting Turbo encoder and the encoding method using the above component encoder. The invention can avoid the two time encoding process in the existing encoder, reduce computation quantity of encode and the coding delay, and reduce the decoding computation quantity of the receiving terminal.

Owner:HUAWEI TECH CO LTD

Encoder of LDPC code of layered quasi-circulation extended structure

InactiveCN100566183CSave resourcesImprove throughputError correction/detection using multiple parity bitsVariable-length codeParallel computing

Owner:SHANGHAI JIAOTONG UNIV

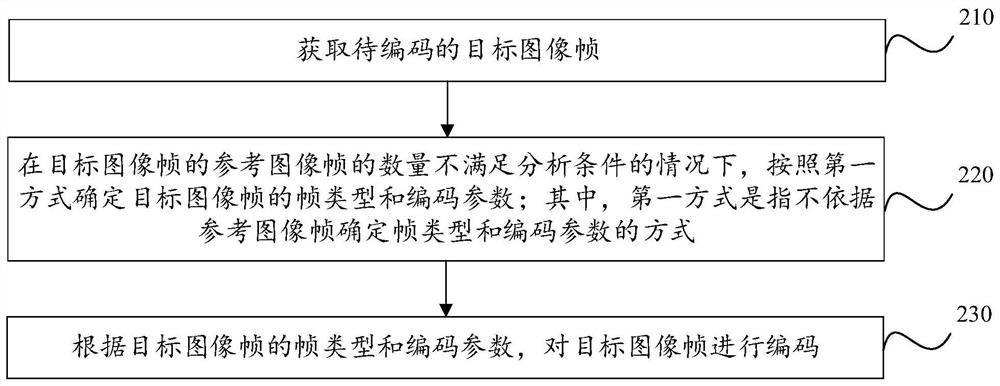

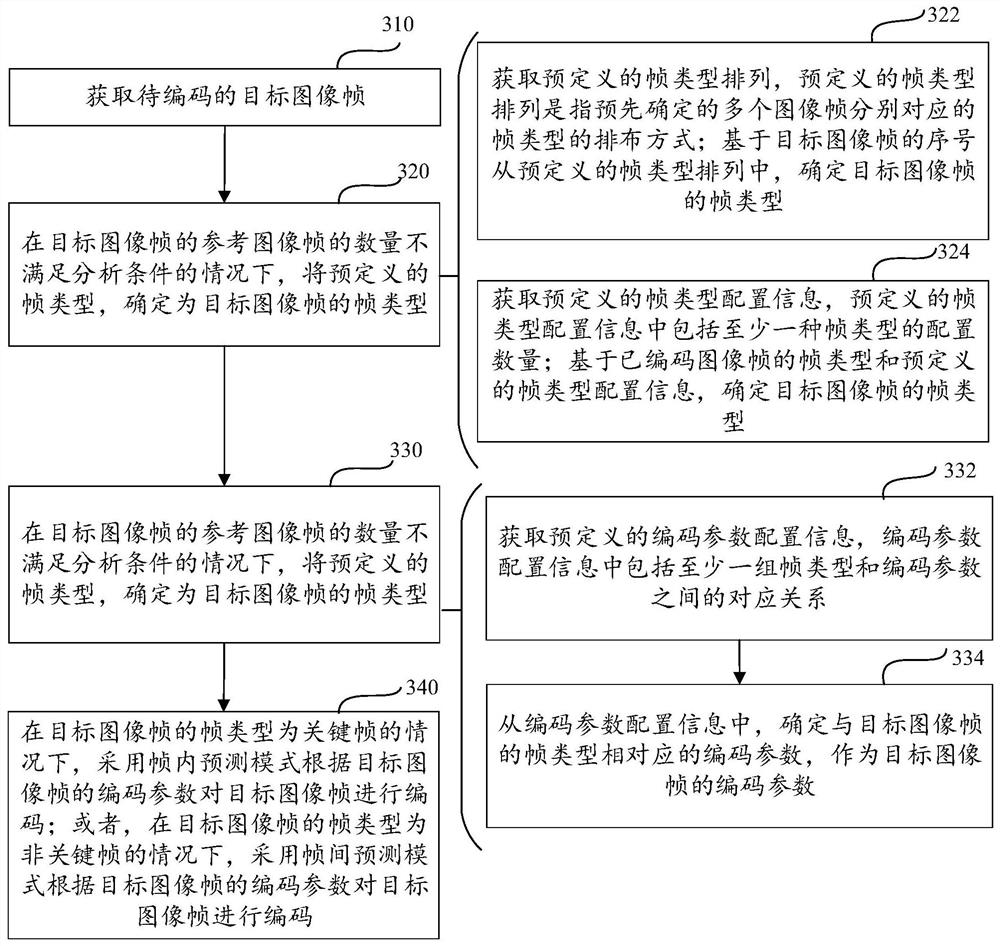

Video coding method and device, equipment and storage medium

PendingCN113973202AEliminate waiting timeReduce encoding delayDigital video signal modificationDigital signal processingVideo encoding

The embodiment of the invention discloses a video coding method and device, equipment and a storage medium, and belongs to the technical field of digital signal processing. The method comprises the following steps: acquiring a target image frame to be coded; under the condition that the number of the reference image frames of the target image frame does not meet the analysis condition, determining a frame type and a coding parameter of the target image frame according to a first mode, wherein the first mode is a mode in which the frame type and the coding parameter are determined not according to the reference image frame; and coding the target image frame according to the frame type and the coding parameter of the target image frame. According to the method, the waiting process that the coding device obtains the enough number of reference image frames under the condition that the number of the reference image frames of the image frame to be coded does not meet analysis is eliminated, the waiting time of the coding device is shortened, excessive parameters and complex calculation modes do not need to be introduced, and the coding time delay can be effectively reduced.

Owner:BIGO TECH PTE LTD

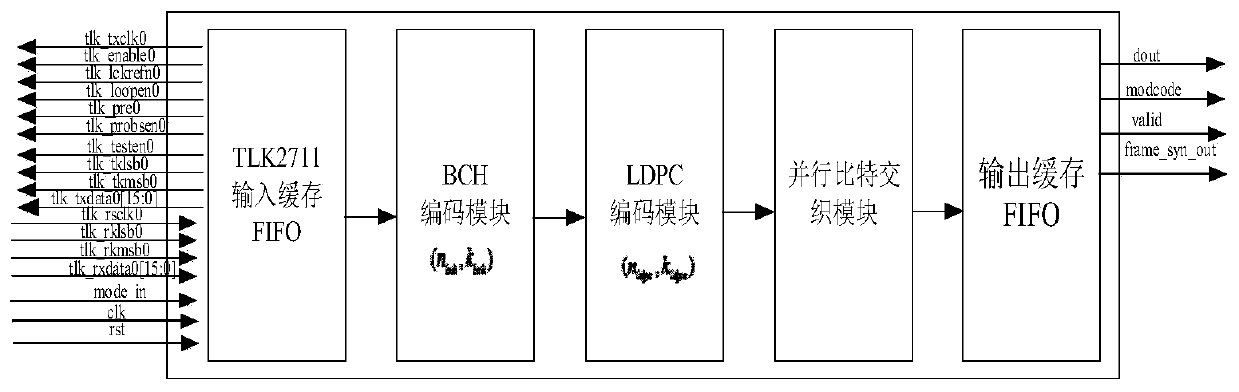

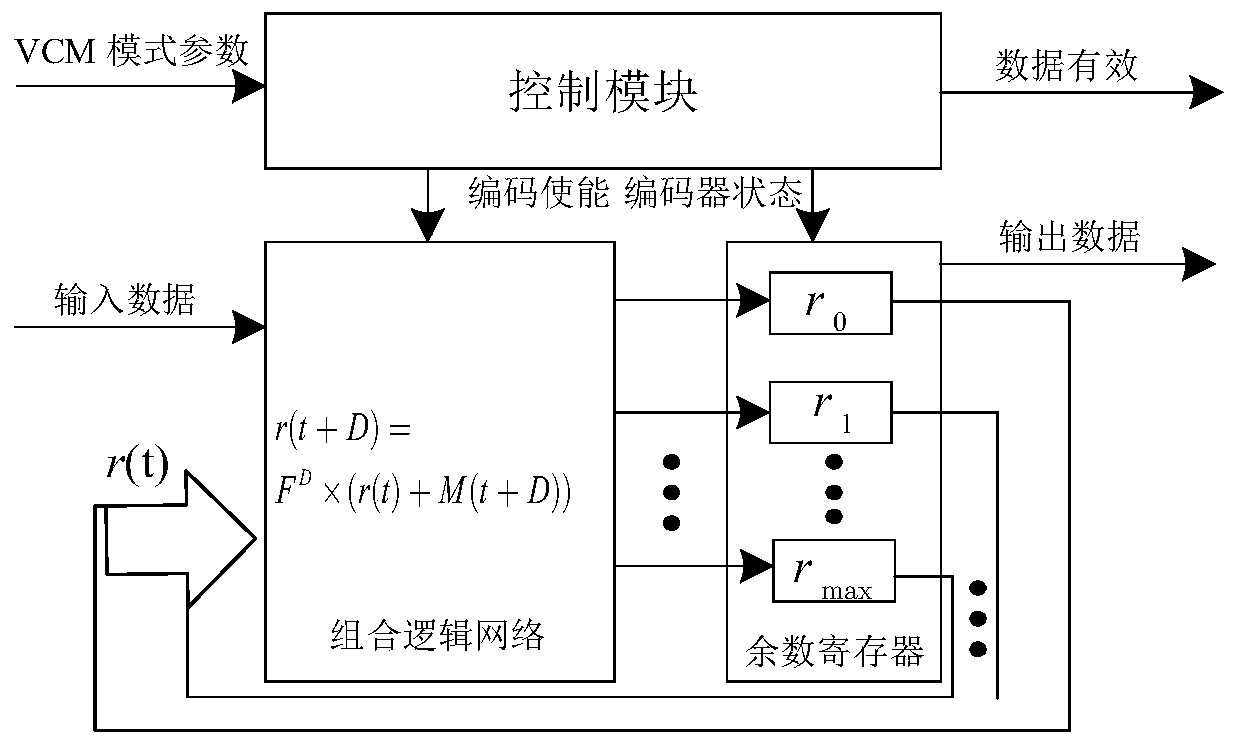

FEC coding IP core for LEO satellite VCM data transmission system

PendingCN111600612AImprove resource utilizationReduce resource consumptionError correction/detection using multiple parity bitsCode conversionEmbedded systemData transmission systems

The invention discloses an FEC coding IP core for an LEO satellite VCM data transmission system. The FEC coding IP core comprises an input cache module, a BCH coding module, an LDPC coding module, a parallel bit interleaving module and an output cache module, wherein the input cache module is used for receiving and caching to-be-coded information bits and VCM mode parameters set by a user; the VCMmode comprises a code rate R, a coding frame length L and a modulation mode; the BCH coding module is used for performing BCH coding on the kbch information bits according to a DVB-S2 standard, generating a code word with the length of nbch, and transmitting coded information to the LDPC coding module; the LDPC coding module is used for performing LDPC coding on the kldpc information bits according to a DVB-S2 standard to generate a code word with the length of nldpc; kldpc is equal to nbch, nldpc is equal to L, and the information bits and check bits are output to the parallel bit interleaving module in parallel in sequence; and the parallel bit interleaving module is used for realizing row and column interleaving required by a modulation mode in the DVB-S2 standard, and the coded and interleaved code words are transmitted to the output cache module in a symbol form for caching.

Owner:NAT SPACE SCI CENT CAS

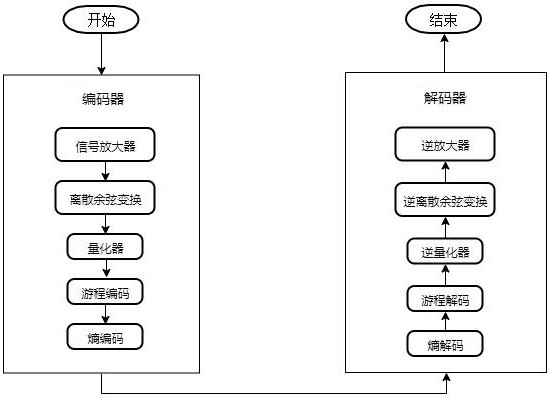

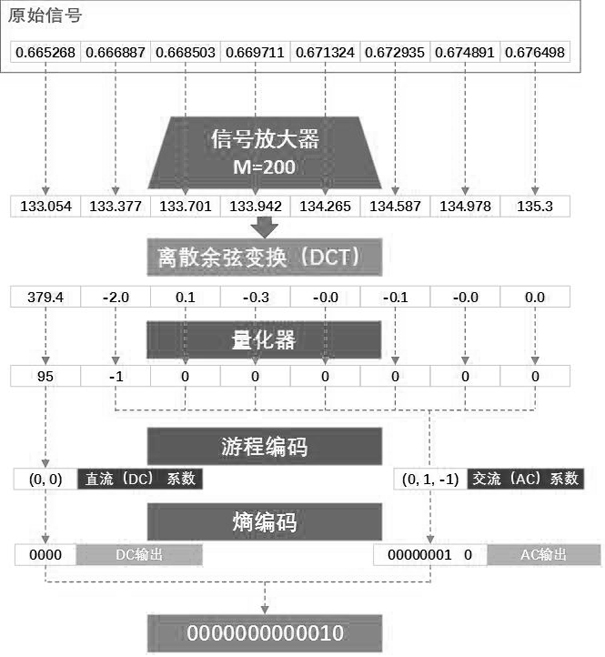

High-efficiency low-time-delay kinesthetic signal encoder and decoder and coding and decoding method

PendingCN112564713ALow latencyReduce encoding delayCode conversionCoding detailsSignal amplifierRun-length encoding

The invention provides a high-efficiency low-time-delay kinesthetic signal encoder and decoder and a coding and decoding method. The encoder is composed of a signal amplifier, a discrete cosine transform module, a quantizer, a run length encoding module and an entropy encoder; the decoder is composed of an entropy decoder, a run length decoding module, an inverse quantizer, an inverse discrete cosine transform module and an inverse amplifier. Compared with an existing advanced tactile coding method, the high-efficiency low-time-delay kinect signal encoder and decoder design provided by the invention has the advantages that the compression ratio is averagely reduced by 50% in comparison with a tactile coding standard algorithm based on a dead zone, and meanwhile, the distortion degree and the time delay are smaller.

Owner:FUZHOU UNIVERSITY

Ultra-low time delay H.264 coding method and coder

InactiveCN104768021AReduce storage timeReduce encoding delayDigital video signal modificationVIT signalsSignal coding

The invention discloses an ultra-low time delay H.264 coding method and coder, and relates to the field of video signal coding. According to the technical scheme, the ultra-low time delay H.264 coding method comprises the steps of preprocessing input video, conducting cache on multiple video lines in the preprocessed video, conducting frame prediction on the multiple video lines, conducting DCT coding and quantization on frame prediction results in sequence, conducting entropy coding on a quantization result and a motion vector, outputting the result of the entropy coding after the result is buffered and the like.

Owner:四川正冠科技有限公司

Background modeling-based static camera video compression method and background modeling-based static camera video compression system

ActiveCN101742319BAvoid splittingImprove compression efficiencyTelevision systemsDigital video signal modificationVideo sequenceCompression method

Owner:PEKING UNIV