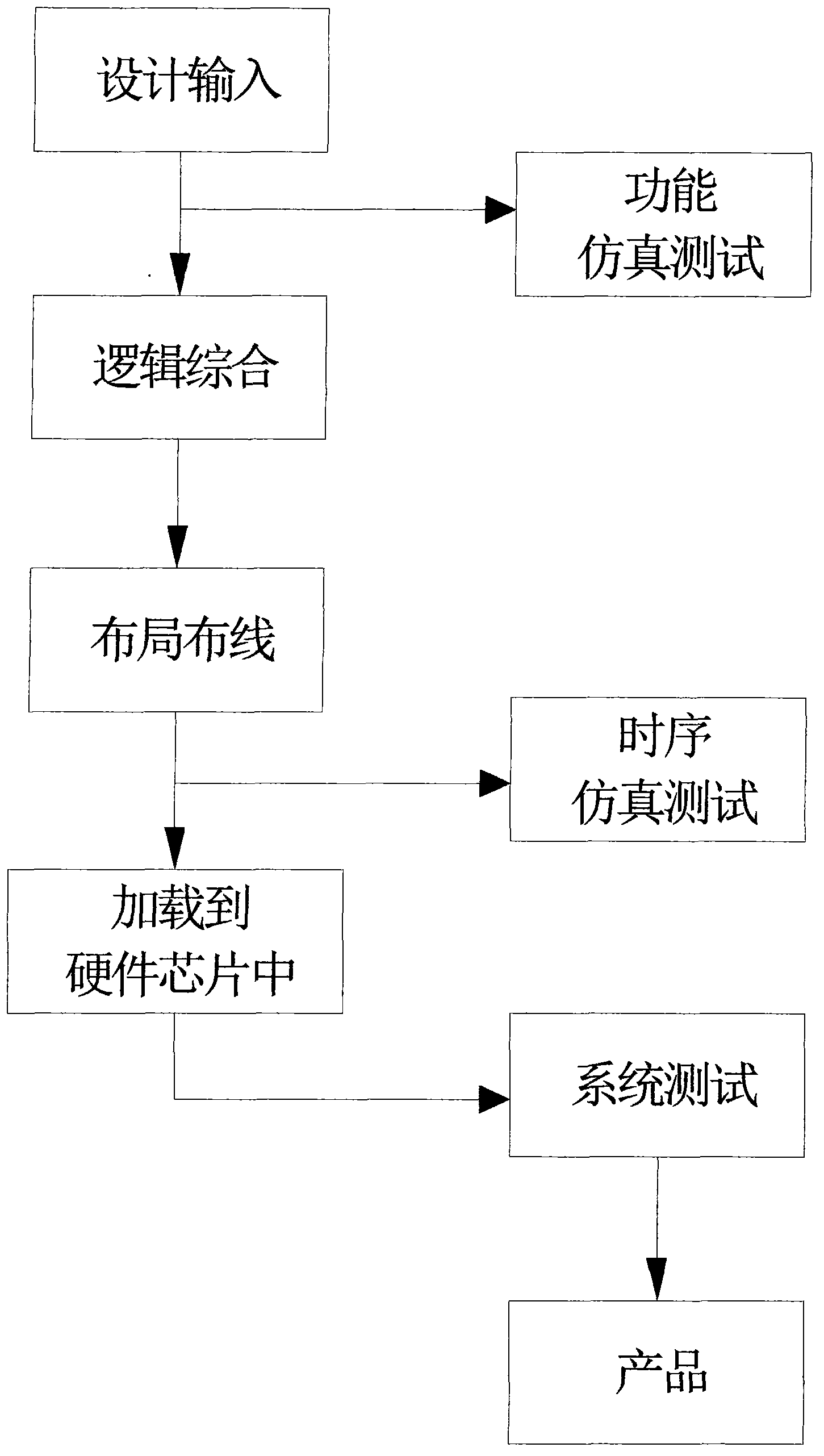

High data volume FPGA (Field Programmable Gate Array) simulating testing method based on time sharing multiplex

A time-sharing multiplexing and simulation testing technology, applied in electrical testing/monitoring, general control systems, instruments, etc., can solve problems such as insufficient memory for large-data FPGA simulation testing, reduce PC dynamic memory allocation, and improve port usage Efficiency, the effect of improving the efficiency of use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

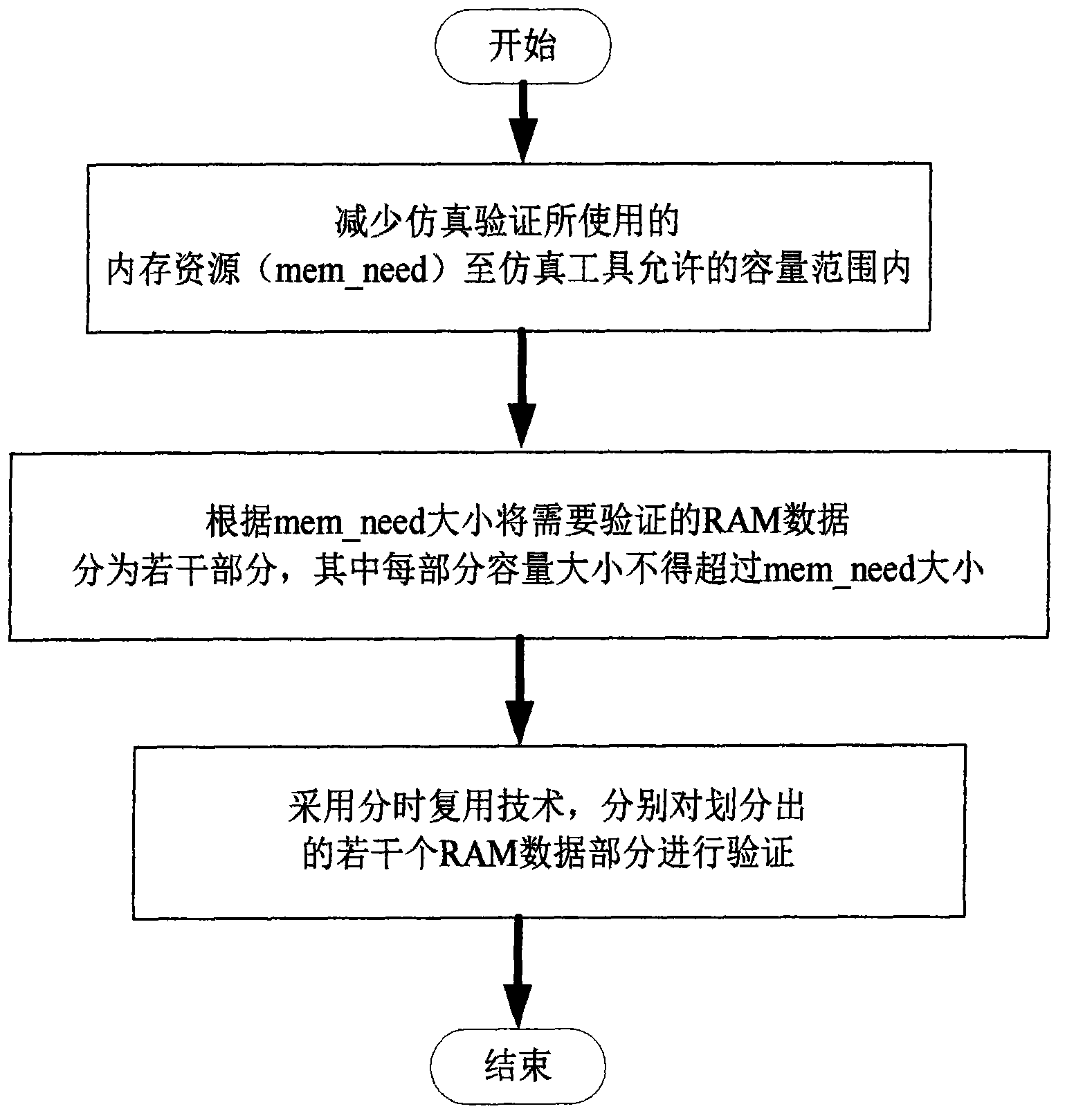

[0031] Below in conjunction with accompanying drawing and embodiment, a kind of FPGA emulation test method based on time-division multiplexing provided by the present invention is further described:

[0032] Such as figure 2 As shown, a large amount of data FPGA simulation test method based on time-division multiplexing comprises the following steps:

[0033] Step S1: reduce the memory resource (mem_need) used by the simulation test to within the capacity allowed by the simulation tool;

[0034] Step S2: divide the RAM data to be tested into several parts according to the size of the memory resource, wherein the capacity of each part shall not exceed the size of the memory resource;

[0035] Step S3: using time-division multiplexing to test the divided RAM data parts respectively;

[0036] Step S4: During time-division multiplexing, use a method of dynamically managing memory to allocate and release memory by dynamically calculating the system memory space required by the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More