Testing device of 3D-SIC (Three-Dimensional-Semiconductor Integrated Circuit) through silicon vias provided with signal rebounding module

A through-silicon via and signal bounce technology, which is applied in the field of 3D-SIC through-silicon via test equipment, can solve problems such as the difficulty of effective detection of failed TSVs, and achieve low power consumption, small area, and low practical cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

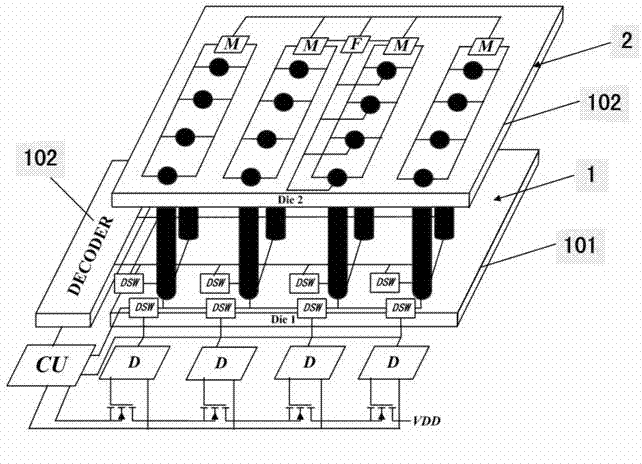

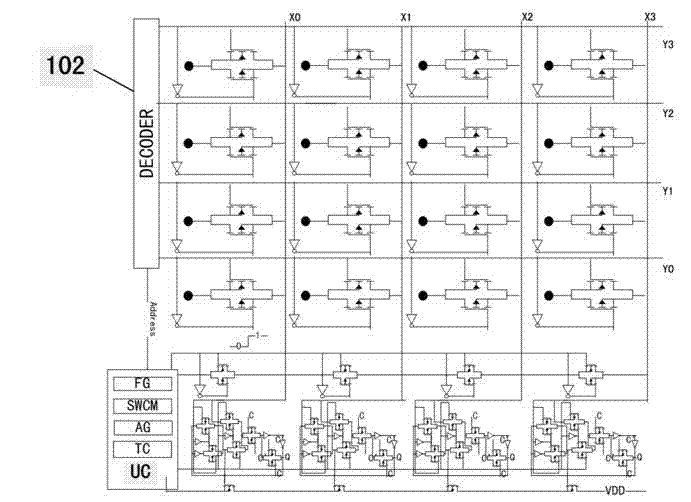

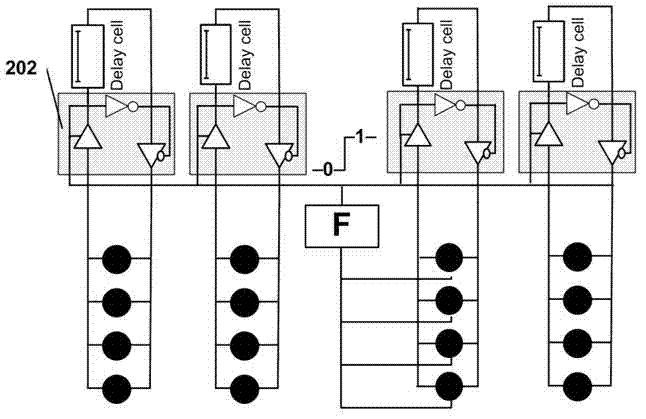

[0031] join Figure 1 ~ Figure 4 , a 3D-SIC through-silicon via testing device provided with a signal bounce module, including a transmitting end 1 and a receiving end 2; the transmitting end and the receiving end are connected through a plurality of through-silicon vias TSV; the transmitting end includes a first chip under test 101, a decoder 102, a control unit CU, a latch D and a bidirectional switch DSW; the receiving end 2 includes a second chip under test 201 and a signal bounce module; the signal bounce module includes a A signal generator F, a plurality of delay units M and a plurality of tri-state gates 202;

[0032] The upper end of the TSV is connected to the delay unit M and the signal generator F at the receiving end, and the delay units M are connected to the signal generator F through respective tri-state gates 202;

[0033]The lower end of the TSV is connected to the decoder 102 and the bidirectional switch DSW at the sending end; the decoder 102, the latch D ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More