Semiconductor package and method of fabricating the same

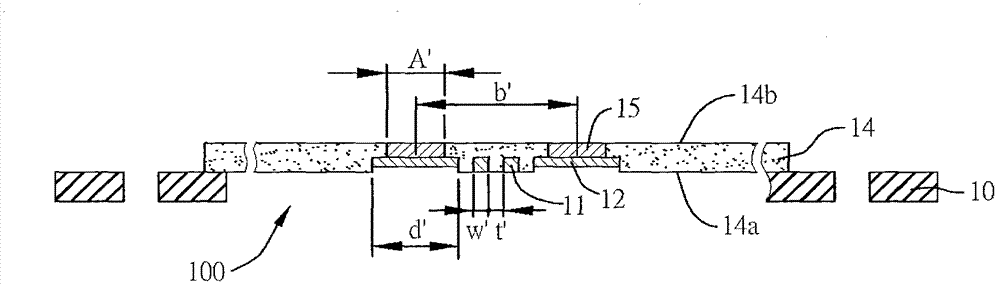

A semiconductor and packaging technology, applied in the field of semiconductor packaging and its manufacturing method, can solve the problems of reducing the bonding force of solder balls, the number of conductive traces 11 is limited, and the distance between electrical contact pads 12 cannot be increased, so as to increase the design elastic effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

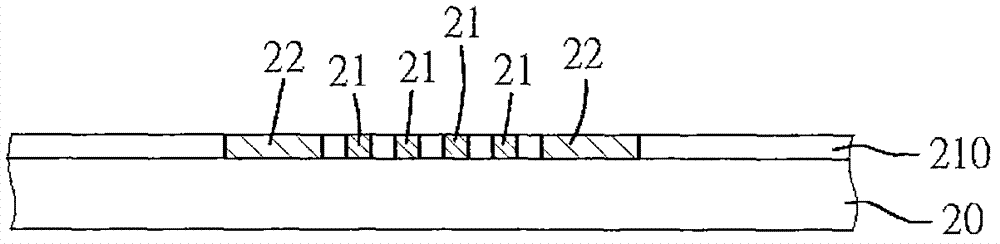

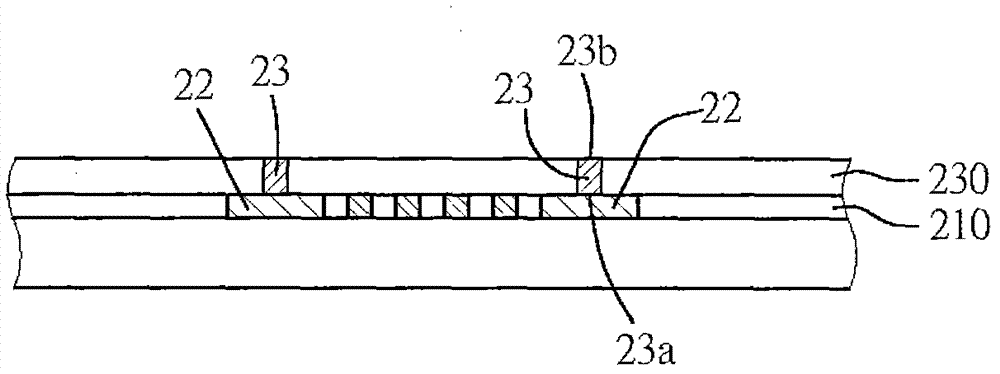

[0045] The implementation of the present invention will be described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification.

[0046] It should be noted that the structures, proportions, sizes, etc. shown in the drawings attached to this specification are only used to match the content disclosed in the specification for the understanding and reading of those skilled in the art, and are not intended to limit the implementation of the present invention. Limiting conditions, so there is no technical substantive meaning, any modification of structure, change of proportional relationship or adjustment of size, without affecting the effect and purpose of the present invention, should still fall within the scope of the present invention. The disclosed technical content must be within the scope covered. At the same time, terms such as "above" and "a" quot...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More