Method and device for processing hardware table entry checking error

A technology for hardware table entry and error checking, applied in the field of communication, which can solve the problems of not providing a hardware table entry recovery mechanism and Parity's inability to correct errors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

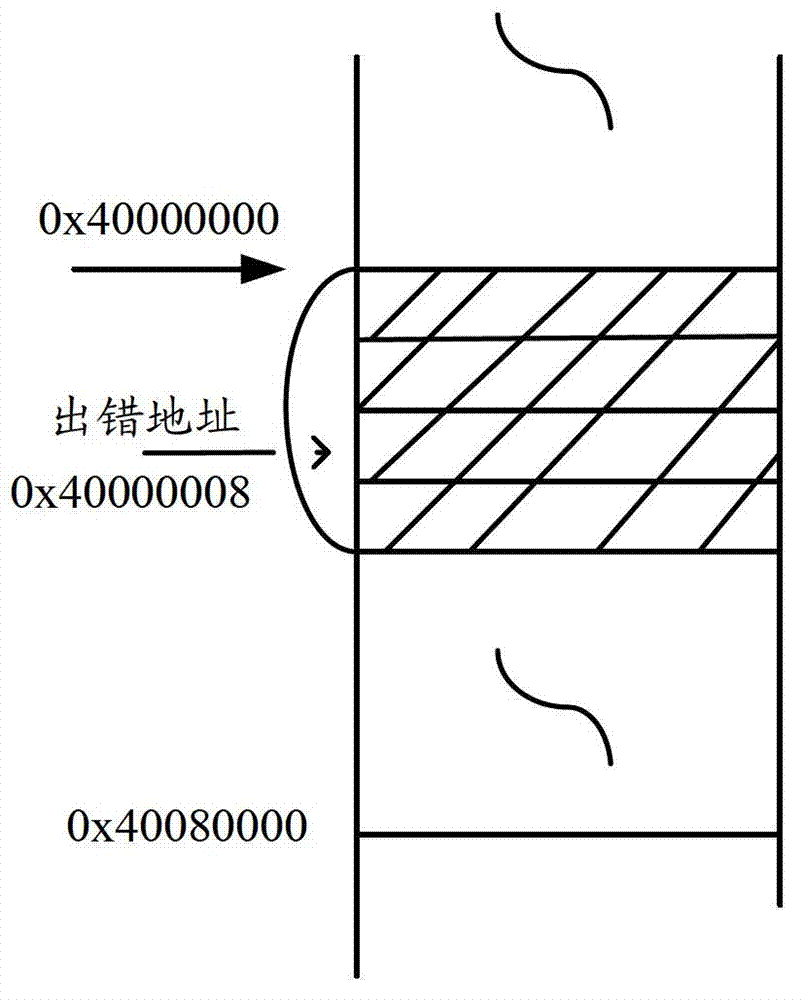

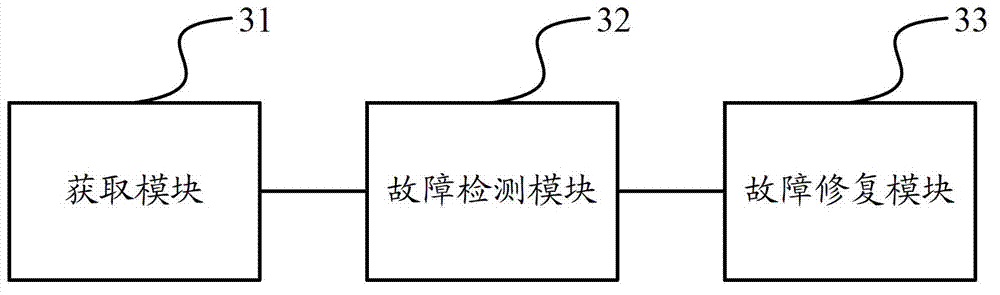

[0041] In view of the above problems existing in the prior art, the embodiments of the present invention provide a technical solution for processing hardware table entry verification errors. In this technical solution, by obtaining the hardware table entry verification error information of the device recorded in the verification information register of the device, the error information of the erroneous hardware table entry in the hardware table entry verification error information within the first preset time length is determined. If the number of errors exceeds the threshold, the index of the faulty hardware entry is determined according to the address of the faulty hardware entry; the corresponding software entry is queried according to the index of the faulty hardware entry, and refreshed according to the queried software entry. In the error hardware table entry, it is determined that the verification information register of the device does not record the new hardware table ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More