semiconductor storage device

A storage device, semiconductor technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problems of memory cell data damage, transistor deviation increase, etc., to achieve the effect of preventing data damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

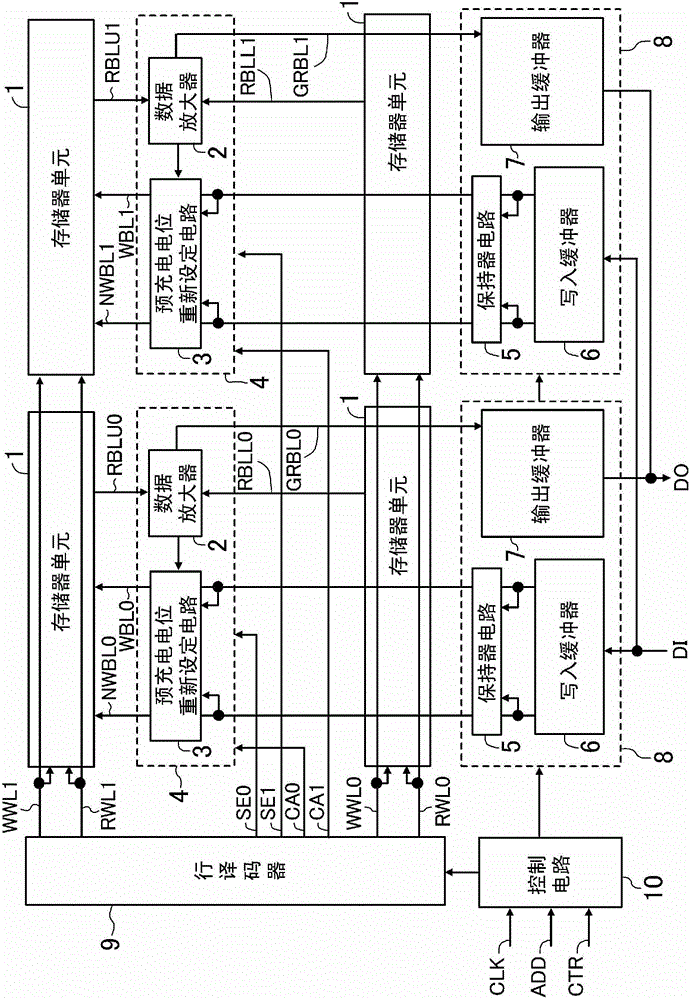

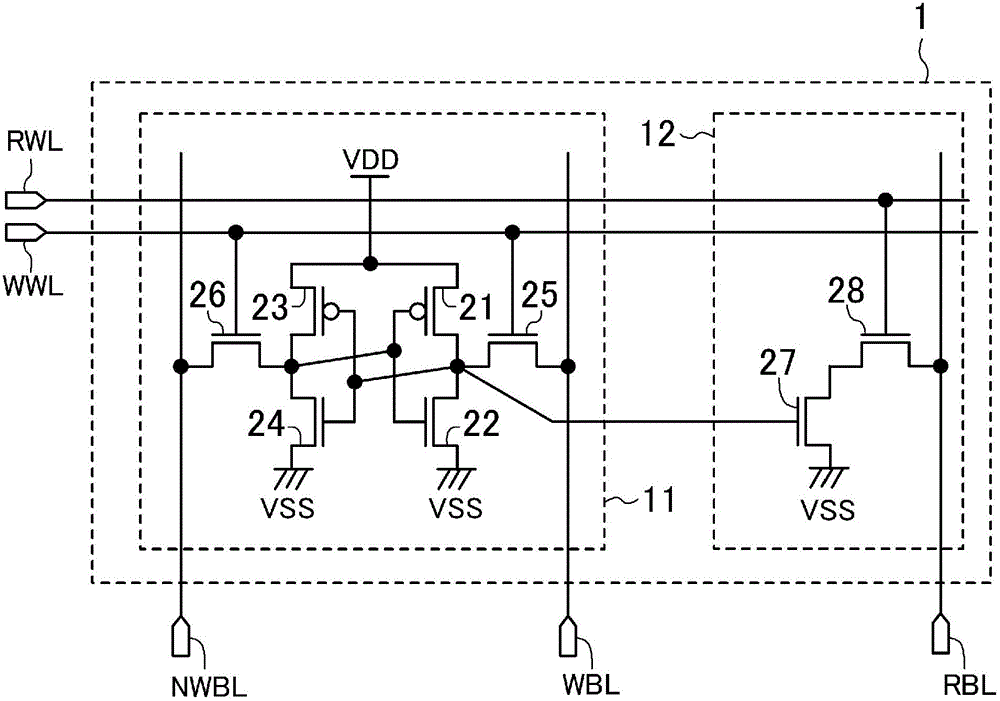

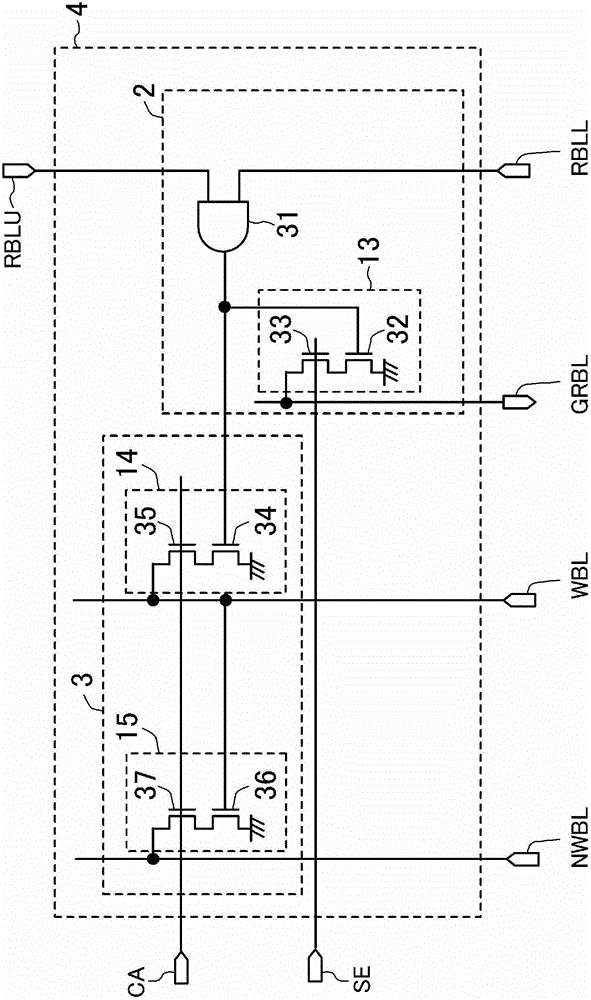

[0031] Regarding the semiconductor memory device according to Embodiment 1 of the present invention, as a specific example, using figure 1 , figure 2 , image 3 , Figure 4 Be explained.

[0032] figure 1 The shown semiconductor memory device includes: a plurality of memory cells 1 arranged in a matrix; a data amplifier 2 for amplifying data on read bit lines RBLU0 / RBLL0 / RBLU1 / RBLL1 connected to each memory cell 1; A precharge potential resetting circuit 3 that resets the precharge potential of the write bit line pair WBL0 / NWBL0, WBL1 / NWBL1 connected to the memory cell 1 by reading data; includes these data amplifiers 2 and precharge potentials. The charging potential reset circuit 3 is arranged between the memory cell 1 and the local amplifier circuit 4 between the memory cell 1; a ground potential (VSS level or L level) is used to hold the bit line pair WBL0 / NWBL0 for writing , a keeper circuit 5 for the power supply potential (VDD level or H level) of WBL1 / NWBL1; a wr...

Embodiment approach 2

[0071] use Figure 10 A block diagram of the semiconductor memory device according to Embodiment 2 of the present invention will be described. Figure 10 The semiconductor memory device shown is relative to figure 1 In the block diagram shown, N-channel transmission gates N0, N1, N2, N3, N4, N5, N6, N7, N8, N9, N10, N11 , N12 , N13 , N14 , and N15 have a function of controlling switching operations by use of write control selection signals SEL0 , SEL1 , SEL2 , SEL3 , SEL4 , SEL5 , SEL6 , and SEL7 .

[0072] With regard to the selection operation during the write operation of the semiconductor memory device having the above configuration, use Figure 11 The timing diagram will be described. Here, it is assumed that the writing operation is completed within one cycle of the clock signal CLK from the time TA to the time TB.

[0073] At time TA, the write operation is started by input of the WRITE command, and the write word line WWL1 and the read word line RWL1 corresponding ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More