DCM (data communications multiplexer) automatic resetting method in satellite-borne high-speed modulator coding FPGA (field programmable gate array)

An automatic reset and modulator technology, applied in electrical components, pulse technology, electronic switches, etc., can solve the problems of large operation delay, increase the complexity of star service software, etc., achieve reliable clock conversion, and good portability, Good product versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

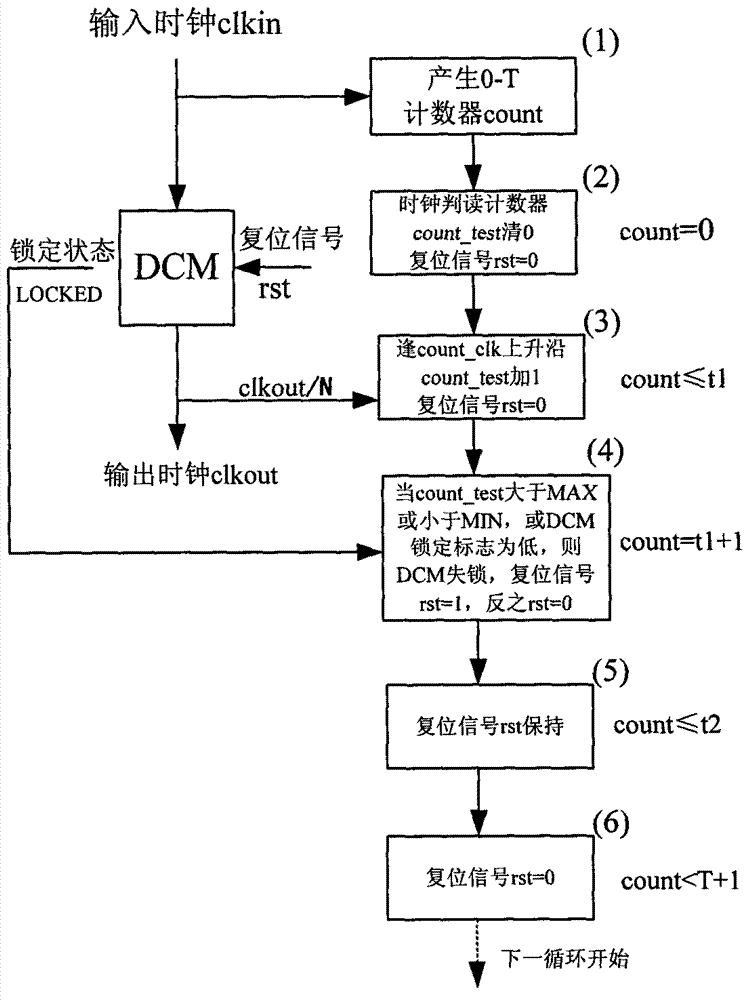

[0026] The present invention will be described in detail below in conjunction with the accompanying drawings.

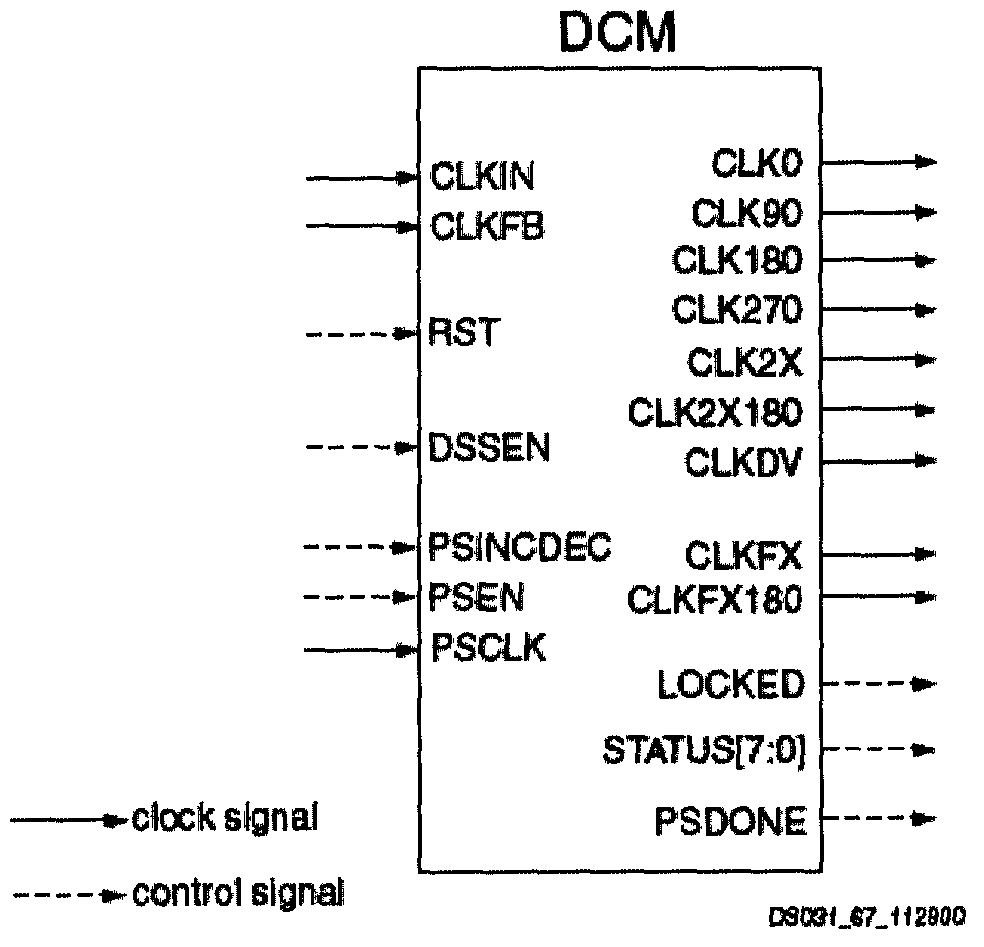

[0027] Firstly, the principle of the present invention is introduced: the key of the present invention is to determine and identify the key factors for DCM out-of-lock, and to issue a reset signal reasonably and effectively. As can be seen from the interface diagram of the DCM module, it has an output signal named "LOCKED", which is defined in the Xilinx user manual "Virtex-II Platform FPGA User Guide" (UG002) as "when all DCM circuits activated goes high when locked" (see figure 1 ).

[0028] However, in practical applications, we found that the lock signal of the DCM module cannot reliably reflect the output state of the DCM. In some cases, the lock signal may be high, but the DCM module does not work normally. In other words, the "LOCKED" signal cannot be relied upon alone to determine the locked status of the DCM. From a practical point of view, the most direc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More